#### **USC-SIPI REPORT #180**

#### VLSI Neurocomputers: EE 599 Term Projects / 1990-1991

edited by

Bing J. Sheu and Chia-Fen Chang

May 1991

## Signal and Image Processing Institute UNIVERSITY OF SOUTHERN CALIFORNIA

Department of Electrical Engineering-Systems

Powell Hall of Engineering

University Park/MC-0272

Los Angeles, CA 90089 U.S.A.

## **VLSI Neurocomputers**

## - EE599 Term Projects / 1990-1991 -

## Edited by Bing. J. Sheu, Ph.D. and Chia-Fen Chang

## **Table of Contents**

| Part I. Digital Neurocomputer Architectures and Design                 |     |

|------------------------------------------------------------------------|-----|

| 1. Te-Ho Chen, Systolic Neural Network                                 | 1   |

| 2. Juinn-Yan Chen, VLSI Implementation for Systolic Neural Network     | 15  |

| 3. Mike Wang, Digital Neurocomputer Design                             | 30  |

| Part II. Applications                                                  |     |

| 4. Hiroto Okada, A Study of an Application of the Back-propagation     |     |

| Network for the Surface Reconstruction                                 | 66  |

| 5. Sa Hyun Bang, A Neural-based Digital Communication Receiver for     |     |

| Inter-Symbol Interference (ISI) and White Gaussian Noise Channel       | 103 |

| 6. Kotleong Shin, A Forecasting Model in the Volatile Stock Market     |     |

| Using Neural Network: A Software Approach                              | 124 |

| 7. Li-Ping King, A Neural-based Voice Control System                   | 142 |

| Part III. Structured Network Solvers for Matrix Algebra                |     |

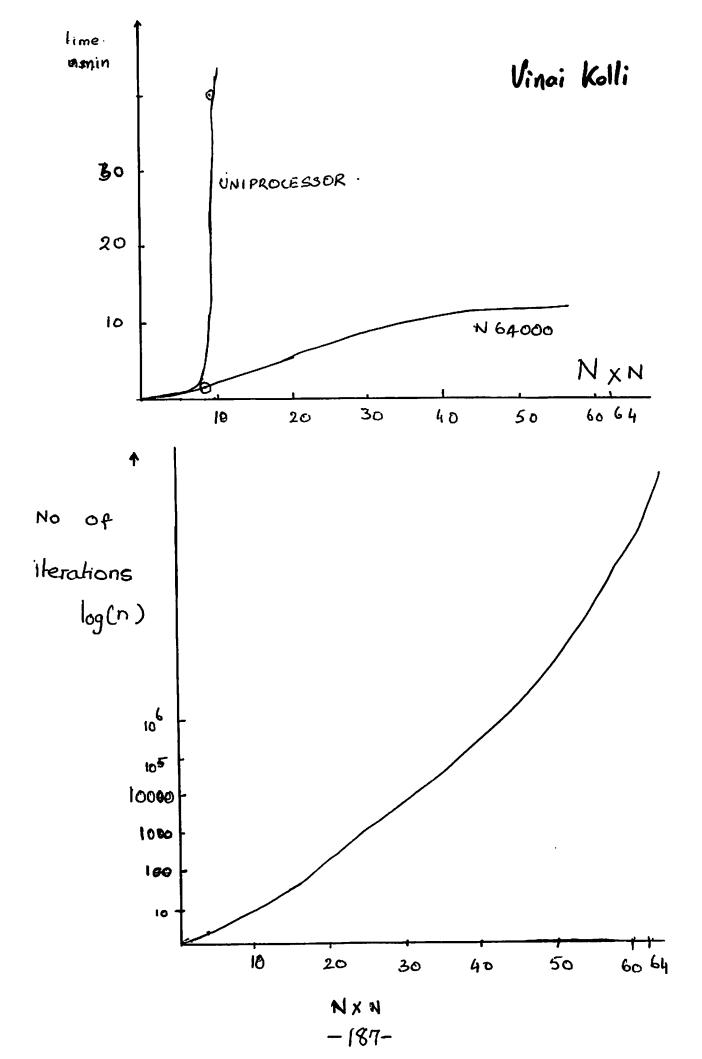

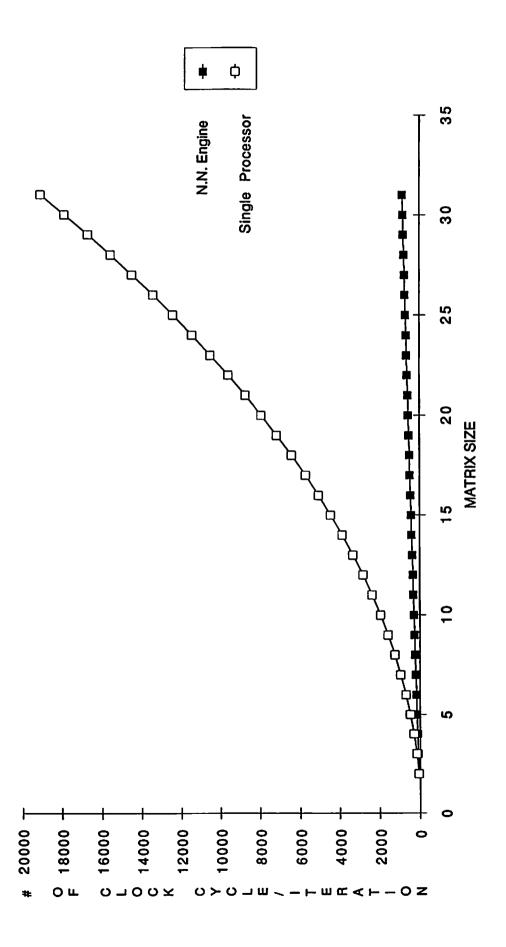

| 8. John Vranich, Srinivas S. Reddy, Vinai Kolli, VLSI Neurocomputing   |     |

| Hardware for Matrix Algebra Using N64000 Chips                         | 168 |

| 9. Joseph C. Wong, System Integration of Structured Trainable Networks |     |

| for Matrix Algebra (LU Decomposition)                                  | 194 |

## SYSTOLIC NEURAL NETWORK

EE 599 term project

professor: B. J. Sheu

Auther: Te-Ho Chen

partner: Juinn-yan Chen

Date: November 28, 1990

#### A.Introduction:

In this project, we tried to implement systolic neural array to take advantage of benefits of neural network, that massively parallel computation and learning algorithm available for neural networks, and benefits of systolic array, that compressing multi-dimensionnal PE into one-dimensional PEs. And this system can satisfy the requirements of digital signal / image processing.

#### B. work partition:

I take care of system level and control unit, and Mr. Juinn-yan Chen works on processing element.

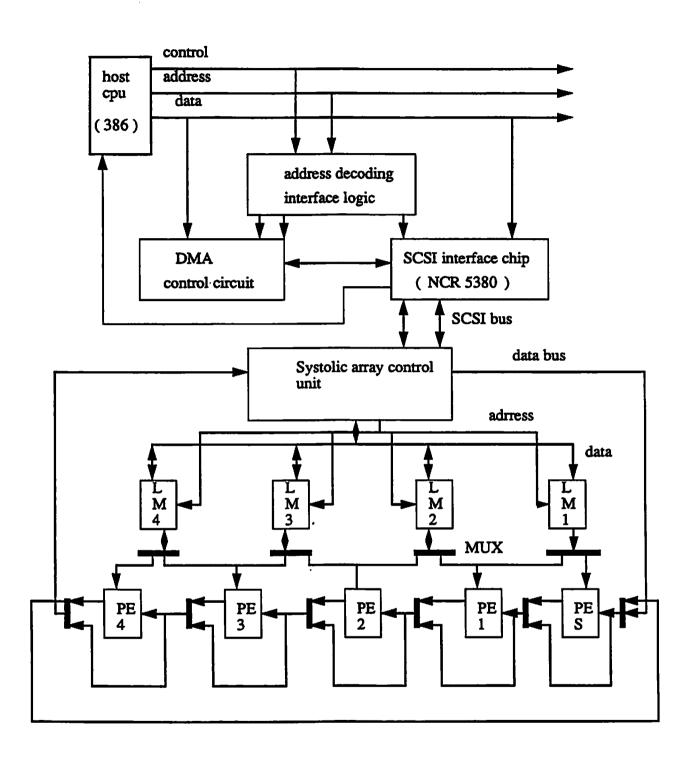

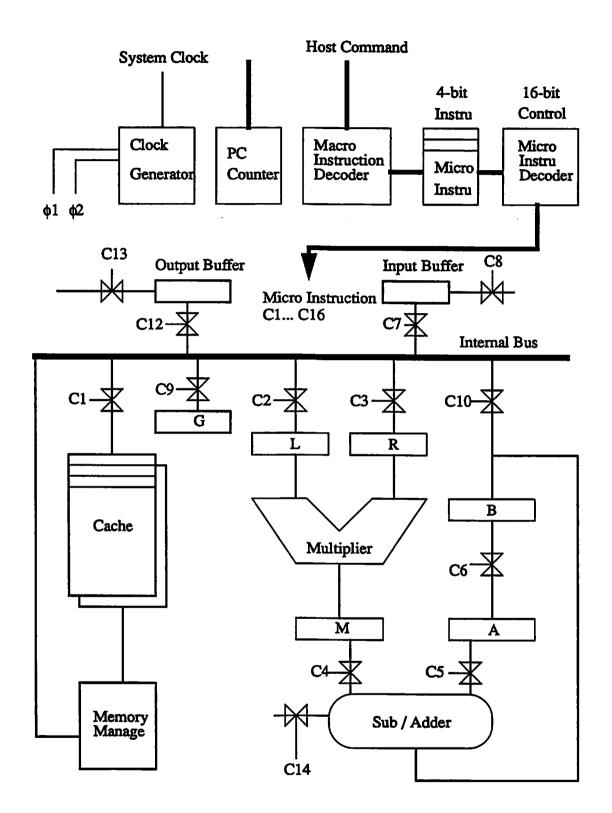

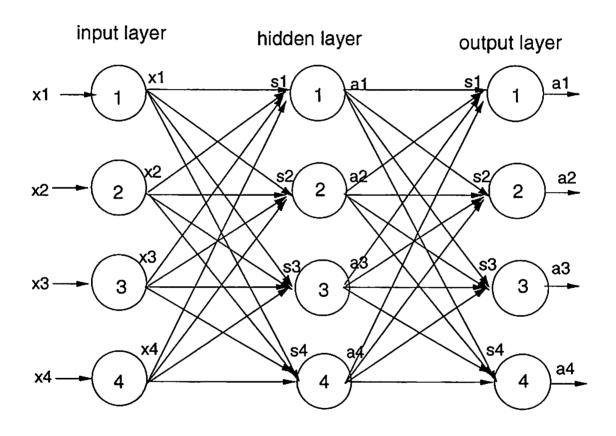

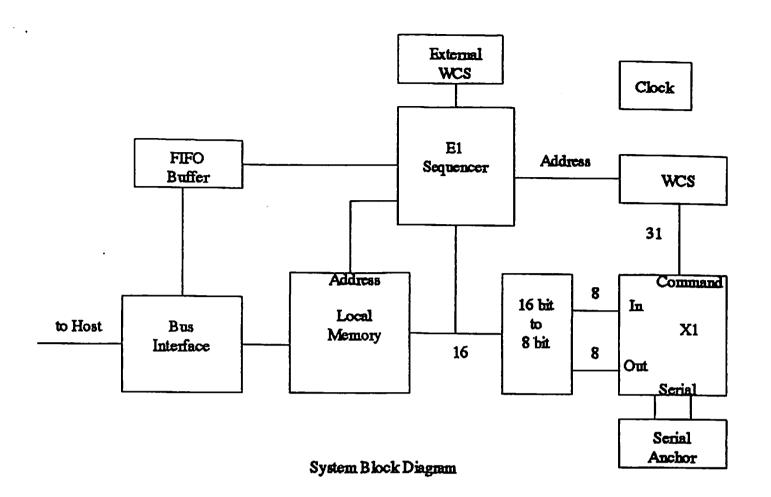

#### C. system architecture: (Fig 1)

.use interface chip as one I/O port, host issue macroinstruction and dimension, then download data via DMA.

- . control unit includes 4 major parts:

- a.memory access part: for download data to each local memory.

- b. fault detection and recovery parts: detect faulty PE, correct error and recover by spare PE.

- c. I/O port: recept data, macrocode and dimension from fost, upload data, faulty signal to host.

- d. contol unit: to control operation of each PE, and to broadcast and collect data.

#### D. implementation:

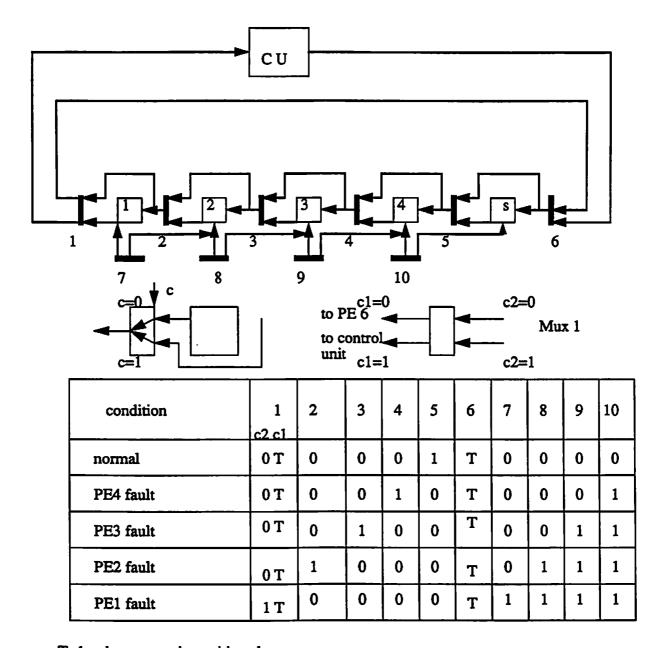

- 1. fault detection and recovery part:

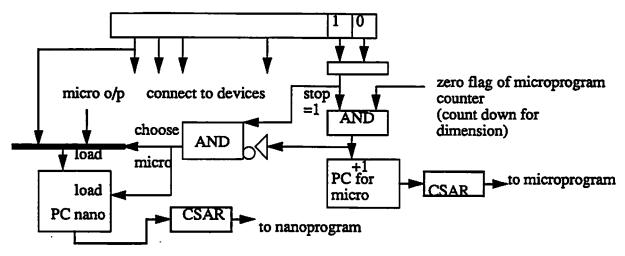

- .use microprogramming

- .advantage: easy to design, maintain, and expand; great portability and compatibility with different performance and different architecture of host and PEs.

- .disadvantage: slower than dedicated control finite state machine.

(could use high speed memory to improve)

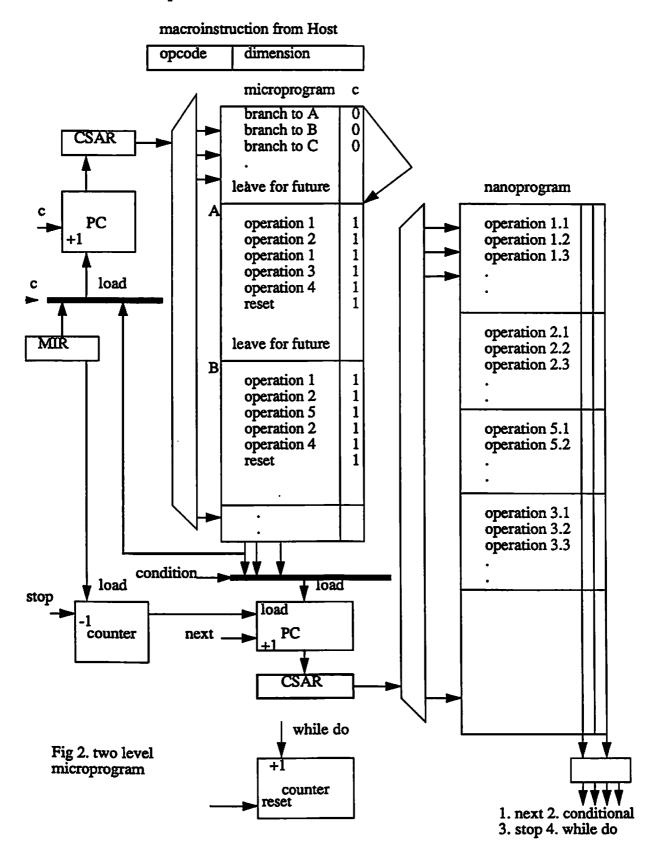

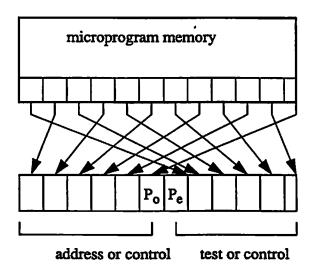

microprogram and supporting hardware isin Fig 2.

.use 2 level microprogram to speedup the accessing speed for most operations are repetious and commonly used.

.use program table on top of microprogram for portability with host.

.4 major operations in microprogram:

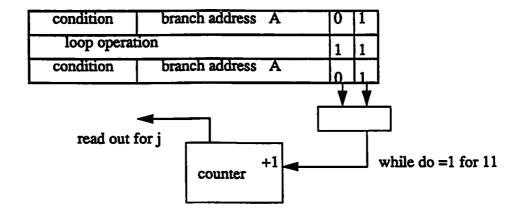

a. next address operation: next operation is at next address. opcode=00.

b.conditionnal branch operation: next operation's address depends on condition in the microcode. opcode=01.

c.while do operation: could be done by combination of next address and conditional branch operations, and use a dedicated counter to count the iteration number. opcode=11.

d.stop operation: for the last operation in nanoprogram, test if repetition enough (content of dedicated counter for dimension of macroinstruction of host). If yes, microprogram go to next operation, else nanoprogram go to first nanooperation and trigger dimension counter to count down. opcode=10.

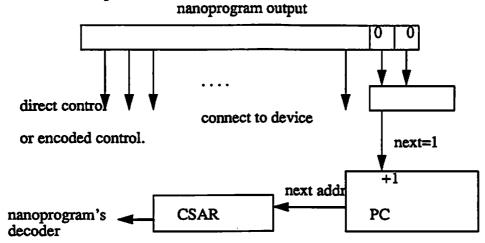

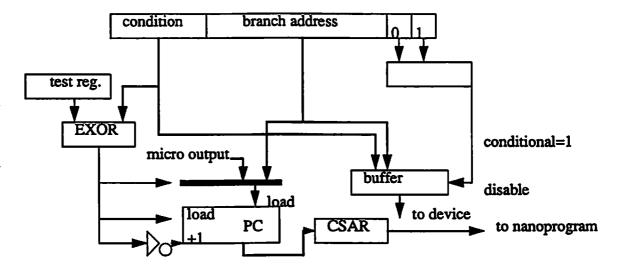

refer to Fig 3,4

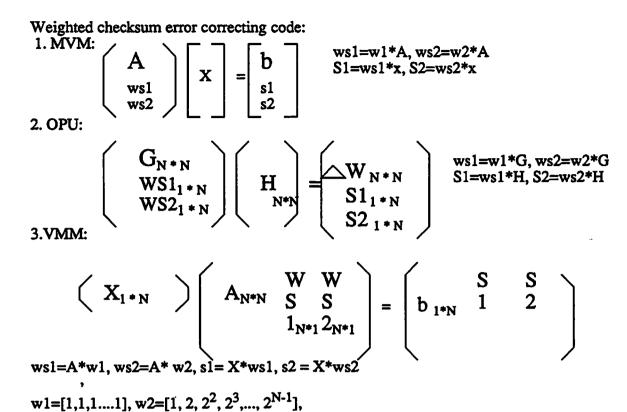

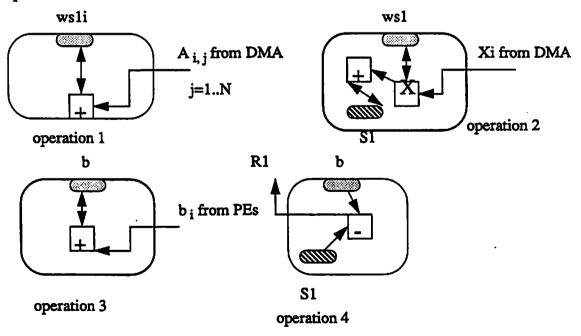

.fault tolerant algorithm use weighted check sum to detect and correct error. (ref 1) Fig 5. Flowchart and corresponding microoperation is in Fig 6. For multiple faulty PEs, the algorithm need a little modification. (ref 1).

Error detection in microprogram and counter:

.use parity bits to detect one or two adjacent faulty bits.( ref 2)

Fig 7, Fig 8.

. required ALU, register and bus even some nanoprogram are the same with PE's. (my partner took care of that part)

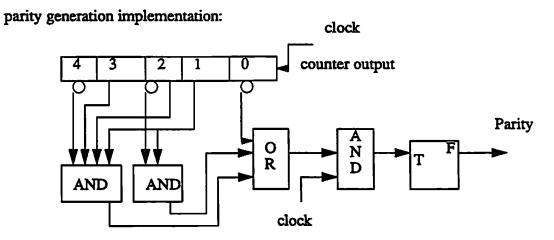

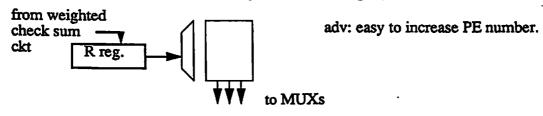

after completion of error detection and correction, recovery operation can be accomplished by dedicated microprogram (not combinational ckt, in order to facilitate the scaling (increase PE number). Fig 9.

#### 2.control unit:

- .to control and monitor each PE's operation.

- .to broadcast and collect data to and from each PE.

- .accomplished by microprogramming.

- .macroprogram (for PEs) format is composed of opcode and iteration number.

.Fig 10.

3 I/O port and memory access parts: future work.

#### E. discussion

.could do RBP and HMM algorithm .(ref 3)

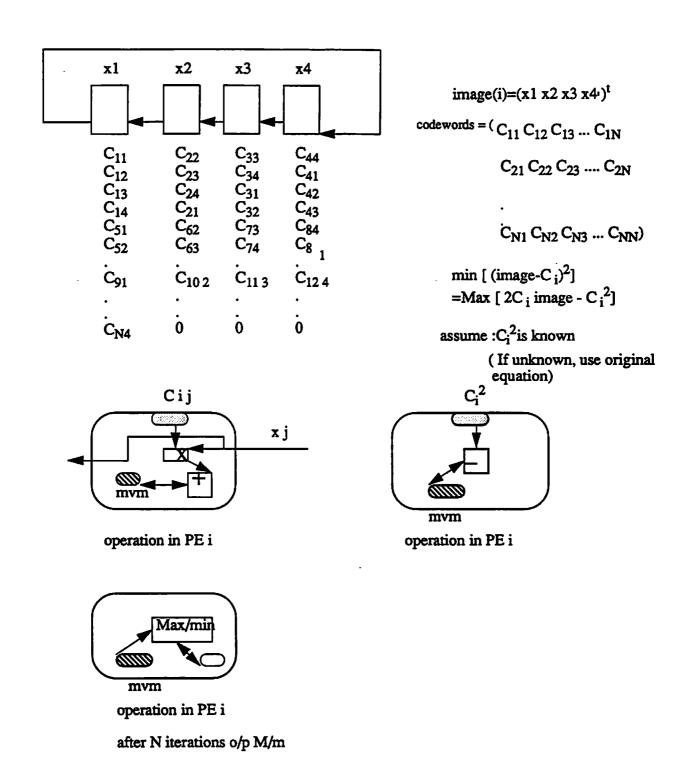

.also can do normal algorithm by ring architecture. eg. vector quantization. Fig 12.

. most operations in PE can be done in pipeline by dedicated buses and registers, and so does parallel processing among PEs. High performance is expected. For 4 PEs, 256\*256 image, 2\*2 window, 1024 codewords, the throught for each PE is 1/15 nsec, then throughput of whole system is 2 frames/sec; copression rate is 3.2:1.

.This system could be general-purpose scalable digital signal processing array (extra application can be done by adding or modifying microprogram).

.also can be special purpose accelerator by using dedicated microprogram in small ROM to set up the configuration.

.suitable to apply to HDTV for image compression and store.

.also suitable for PC for image processing: this system doesn't need high speed host because of macroinstruction. (more image and less text is the future trend).

- .could be self organized system by expanding I / O part and memory management.

- .also could be emulator for neural network and multiprocessors system.

- .This project isn't finished yet, and needs lots of work.

#### Reference:

- 1."VLSI array processors "by S. Y. Kung Prentice - Hall, 1988, 102-408.

- "Microprogrammed control and reliable design of small computers" by George D. Kraft / Wing N. Toy.

Prentice - Hall inc., 1981, P 297 and 277.

- 3. "A systolic neural network architecture for hidden Markov Models" by Jenq Neng Hwang, John A. Vlontzos, and Sun-Yuan Kung.

IEEE Trans. on ASSP, vol. 37, NO. 12, Dec 1989, 21967—1979.

Fig 1. Systolic array neural network architecture. (4 PE's are shown, more PE's and LM's can be added with modification of program memory content in control unit.)

#### mware/hardware implementation:

1

#### architecture for 4 kinds of operation: (in nanoprogram)

#### 1. next address operation

#### 2. conditional branch operation:

#### 3. while do operation:

Fig 3. microoperation format and supporting hardware.

4. stop operation: the last operation in nanooperation sequence.

Fig 4. stop oeration

#### Fault tolerant for microprogram and counter:

- 1. fault tolerant for microprogram:

- . assume only one bit error or 2 bit adjacent errors considered.

.use one parity bit for ease (m -out-of-2m could detect multiple adjacent errors, but complicated, and un-systematic)

Fig 7 interleaved coding fault detection for microprogram

R1=w1\*X-S1, R2=w2\* X-S2( depend on format of ws1,2)

IF R1  $\neq$  0 and R2  $\neq$  0 then R2/R1=2<sup>j-1</sup>, b<sub>j</sub> error, and correct b<sub>j</sub> = b<sub>j</sub> - R1.

Implementation in neural PE for case of R1:

Fig 5. weighted check sum coding

Microprogramming for weighted check sum coding and fault tolerant: take MVM as example:

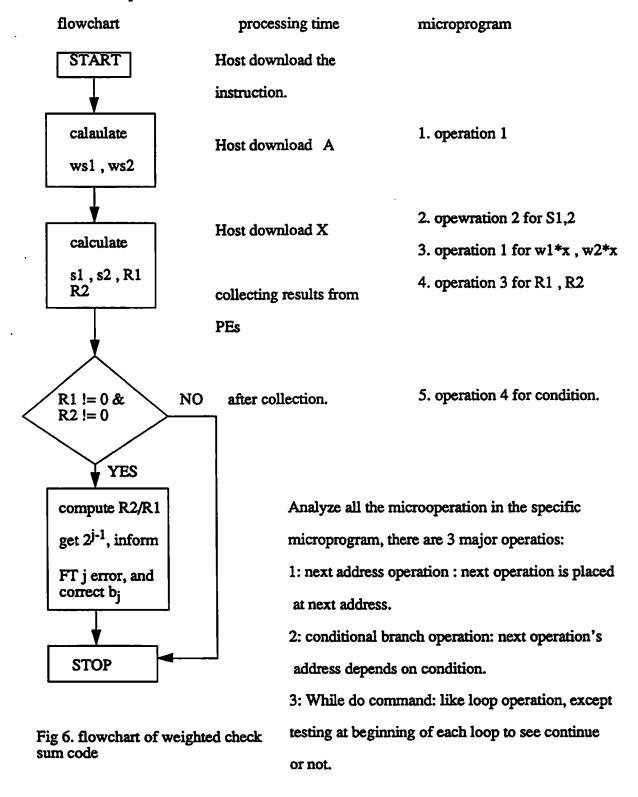

2. fault tolerant for counter: also use single parity bit.

| present | next    | parity change |

|---------|---------|---------------|

| 0       | 1       | yes           |

| 0 1     | 1 0     | no            |

| 0 1 1   | 1 0 0   | yes           |

| 0111    | 1 0 0 0 | no            |

From the table, we find that

- 1). If the rightmost 0 occurs in an even-number bit, then parity change.

- 2). otherwise no.

Fig 8. counter parity bit generation.

Recover circuit after knowing falty PE:

T=1: when vector is partitioned

T=0: otherwise

The above words can be directly stored as microprogram. (c1, MUX 6 excluded).

Fig 9. recover y microprogram.

#### . Control unit:

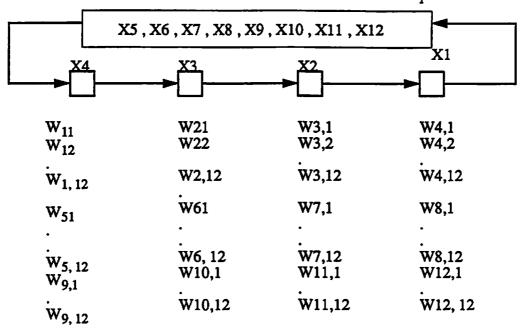

MVM (matrix - vector multiplication): [A]<sub>12\*12</sub>[X]<sub>12\*1</sub> partition method:

weight arrangement is different from original because serially not parallely input vector.

| step | instruction<br>from control | PE1   | PE2   | PE3   | PE4   |

|------|-----------------------------|-------|-------|-------|-------|

| 1    | 36<br>mvma to PE 1          | mvm a |       |       |       |

| 2    | mvm a to PE 2               | mvm a | mvm a |       |       |

| 3    | mvm a to PE 3 36 36         | mvm a | mvm a | mvm a |       |

| 4    | 36<br>mvm a to PE 4         | mvm a | mvm a | mvm a | mvm a |

| •••• |                             | mvm a | mvm a | mvm a | mvm a |

| 37   | mvmb 3 to PE                | mvm b | mvm a | mvm a | mvm a |

| 38   | mvmb 3 to PE 2              | mvm b | mvm b | mvma  | mvm a |

| 39   | mvmb 3 to PE 3              | mvm b | mvm b | mvm b | mvm a |

| 40   | mvmb 3 to PE 4              |       | mvm b | mvm b | mvm b |

mvm a: weighted sum processing, mvm b: threshold activation. 36, 1 means dimension. could use microprogram to do control.

Fig 10. control unit microprogram.

Fig 12. one of the application except RBP, HMM of systolic neural circuit.

## VLSI Implementation for Systolic Neurial Network

#### Introduction

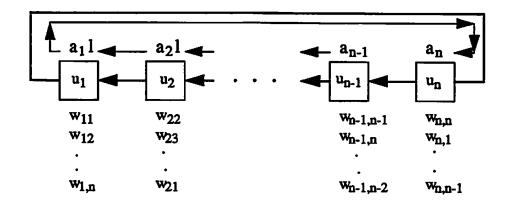

The original idea of this report comes from the publication of S.Y. Kung, "A systolic Neurial Network Architecture for Hidden Markov Models", IEEE Transactions on Acoustics, Speech and Signal Processing. vol 37, No 12. DEc 1989.

In S.Y. Kung's paper, he advocates a systolic neurial network architecture for implementating the hidden Marcov Models ( HMM's ). He also gives a unified algorithm formulation for recurrent back-propagation ( RBP ) network and HMM's for architectural design.

However, we find this architecture is very powerful and not just only suitable for Artificial Neurial Network (ANN) but also signal processing. We can find the data processing portion between ANN and Signal Processing is very similar. Therefore, we want to modify this structure to adapt more applicastions.

#### Work Partition

This work will be acomplished by two-people team work. One is for the overall system architecture design. One is for the design of Processor Element ( PE ).

Teho Chen will be responsible for the overall system architecture which includes

- 1. Host computer.

- 2. Ring Controller.

- 3. Fault Tolerance Architecture.

His work will concentrate on finding algorithms for a specific application, and implement these algorithms in a systolic procedure, then send macro commands to each PE and monitor its opeartion.

I will be responsible for the VLSI Implementation of the PEwhich includes

1. Control Portion.

()

- 2. Data Communication Portion.

- 3. Data Processing Portion.

My work will concentrate on decompose the mavro command received from Host Computer into several micro commands, find algorithms for these micro commands then implement them with a systolic procedure.

## Algorithm

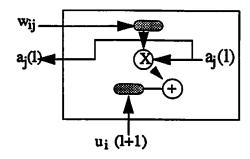

It can be shown that operations in both the retrieving and learning phase of RPB's and HMM's can be formulated as consecutive matrix-vector multiplication ( MVM ), consecutive outer-product updating (OPU) and consecutive vector-matrix multiplication (VMM) problems. In terms of the array structure all these formulations lead to a universal ring systolic array architecture. We can find all these operations call for an MAC (multiplication and accumulation ) processor. So, we can integrate the three architectures for these operation into one processor element.

Below are the algorithm for MVM, OPU and VMM

MVM:

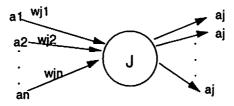

$$\mathbf{u_i(l+1)} = \Sigma \; \mathbf{w_{ij}} \mathbf{a_j(l+1)}$$

$$a_i(l+1) = f_i(u_i(l+1), \theta_i(l+1))$$

where  $u_i$  is the net inputs,  $\theta_i$  is the external inputs, fi is the nonlinear activation function, ai is the activation function, wij is the weighting function.

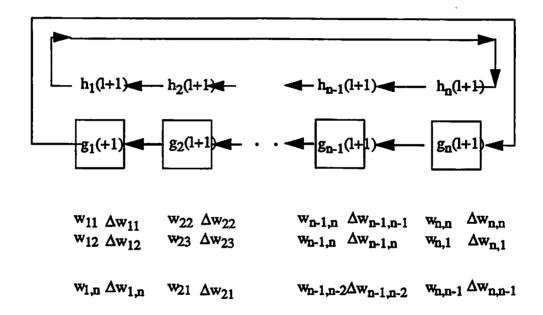

OPU:

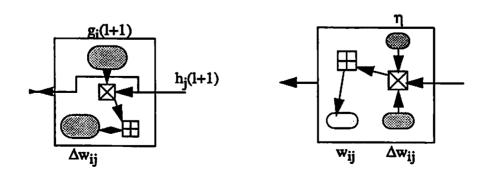

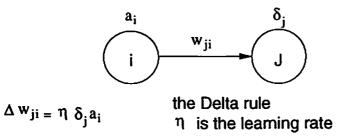

$$w_{ij} \Leftarrow w_{ij} \oplus \eta \Delta w_{ij}$$

where  $\oplus$  is a minus opoeration in RBP's and a multiplication operation in HMM's

and

$$g_i(l+1)=\delta_i(l+1)f'(l+1)$$

,  $h_i(l+1)=a_i(l)$

$$h_j(l+1)=a_j(l)$$

for RBP's

$$g_i(l+1)=\delta_i(l+1)f_i(\theta(l+1))$$

,  $h_i(l+1)=a_i(l)$

$$h_i(l+1) = a_i(l)$$

for HMM's

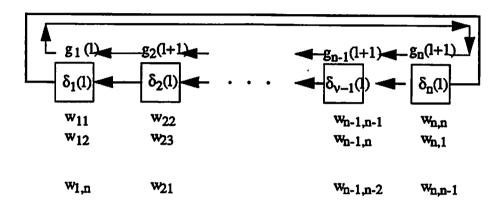

VMM:

$$\delta_{i}(l) = \Sigma \; g_{j}(l+1) w_{ij}$$

where  $\delta_i$  is the back-propagated corrective signal.

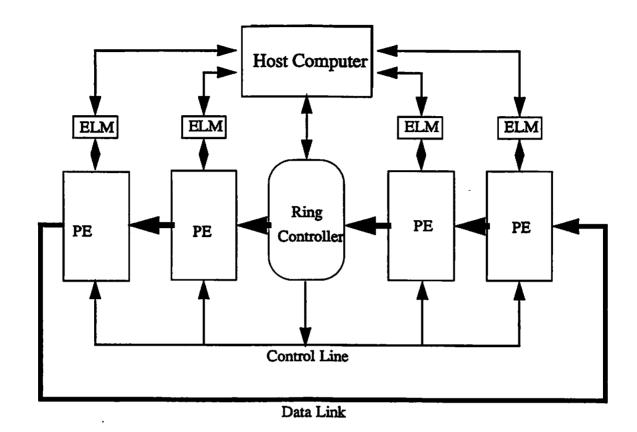

#### \* Overlook for the overall system

It's clear that we can have more operations except these three operation. However, for a ANN application, these will be enough. So, we will concentrate on integrating these three operations into a single PE. Other algorithms such as FFT, Convolution and Viterbi are mainly composed of MVM, OPU and VMM operation. Therefore, it is desirable to design a programmable PE that will be used not only in ANN.

#### \*\* General Operatio

For this purpose, we devided the overall system into Host Computer, Ring Controller, PE and connection. The Host Computer will analysis whole problem and choose a specific program to work. This specific program will be decomposed into consecutive MVM, OPU and VMM operations. And these operations will be recognized as macro commands.

#### \* First Version of micro instruction

The PE will receieve macro command and decompose this command into several micro instructions. These micro instructions will control the switch of bus to ensure accurate data flow and processing.

#### \* RISC approach of micro instruction

After we got the original micro instruction steps, we found there are many overlap ther.

Therefore, we can redece these instruction steps into compact instructions. We should notice the data cannot be the internal bus simutaneously. Besides, the multiplication and the addition should be seperate apart at least one step.

#### \* Pipeline apoproach

In order to increase the speed of the processor, we can break the internal bus into more bus line. Then we can overlap more steps together because they do not occupy the same bus.

#### \* Circuit Design Consideration

\* The speed of the PE will be limited by multiplier. We choose wallice multiplier. Because wallice structure can be seprated into 4\*4 muiplier block and wallice tree block, we can add a pipeline procedure here and increase the speed of the PE. Actually, in this report, we do not do pipeline here.

- \*Adder will be Carry Look Ahead Adder

- \* Register and memory will use standard cell design.

## Overall System Architecture for Ring Systolic Array

- \* Host Computer load data and commands into PE through Ring Controller.

- \* For a specific algorithm, Host Computer will chose a specific program composed of macro command sequences.

- \* Data such as  $w_{ij}$ ,  $\Delta w_{ij}$ ,  $g_i$ ,  $h_j$ ,  $\delta_j$  and  $\eta$ ...will be loaded into External Local Memory from Host Computer directly.

Processing Element Building Blocks for Ring Systolic Array

#### MVM OPERATION

\* Algorithm

$$\mathbf{u_i(l+1)} = \mathbf{w_{ij}a_j(l)}$$

## \* Associative Ring Structure

## \* Associative Data Processing Structure

## \* Associative Original Micro Instruction Bus Control

0 initialize zero A=0 B=0

| Step | Micro instru description                 | cl | c2 | <b>c</b> 3 | c4 | <b>c</b> 5 | <b>c</b> 6 | <b>c</b> 7 | c8 | <b>c</b> 9 | <b>c10</b> | c11 | c12 | c13 | c14 |

|------|------------------------------------------|----|----|------------|----|------------|------------|------------|----|------------|------------|-----|-----|-----|-----|

| 1    | load a <sub>j</sub> (1)                  |    |    |            |    |            |            |            | 1  |            |            |     |     |     | П   |

| 2    | a j (1) _ L ,output                      |    | 1  |            |    |            |            | 1          |    |            |            |     | 1   |     |     |

| 3    | <sup>W</sup> ij → R                      | 1  |    | 1          |    |            |            |            |    |            |            |     |     |     |     |

|      | Do multiply                              |    |    |            |    |            |            |            | П  |            |            |     |     |     |     |

| 4    | $w_{ij} a_j(1) + u_i(1+1) \rightarrow B$ |    |    |            | 1  | 1          |            |            |    |            |            |     |     |     |     |

|      | Do addition                              |    |    |            |    |            |            | $\top$     |    |            | Π          |     |     |     |     |

| 5    | $B \longrightarrow A (u_i(1+1))$         |    |    |            |    | 1          |            |            |    |            |            |     |     |     |     |

## \* Associative Reduced approach of Micro Instruction

| Step | Micro instru description | c1 | c2 | с3 | c4 | с5 | сб | с7 | с8 | с9 | c10 | c11 | c12 | c13 | c14 |

|------|--------------------------|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|

| 1'   | Group 1, 2, 4            |    | 1  |    | 1  | 1  |    | 1  | 1  |    |     |     | 1   |     |     |

| 2'   | Group 3, 5               | 1  |    | 1  |    |    | 1  |    |    |    |     |     |     |     |     |

<sup>\*</sup> Time comsumiing 1x addition + 1xmultiplication

#### OPU OPERATION

## \* Algorithm:

$$\begin{split} \Delta w_{ij} & \longleftarrow \Delta w_{ij} + g_i(l+1)h_j(l+1) \\ w_{ij} & \longleftarrow w_{ij} \oplus \eta \Delta w_{ij} \end{split}$$

## \* Associatative Ring Structure:

## \* Associatative Data Processing Structure

## \* Associative Original Micro Instruction Bus Control

| Step | Micro instru description              | c1 | c2 | <b>c</b> 3 | c4 | <b>c</b> 5 | <u>c6</u> | c7 | c8 | c9 | c10 | c11 | c12 | c13 | c14 |

|------|---------------------------------------|----|----|------------|----|------------|-----------|----|----|----|-----|-----|-----|-----|-----|

| 1    | load g <sub>i</sub> (l+1) to L from G |    | 1  |            |    |            |           |    |    | 1  |     |     |     |     |     |

| 2    | read hj(l+1) to buffer                |    |    |            |    |            |           |    | 1  |    |     |     |     |     |     |

| 3    | $h_j(l+1) \longrightarrow R,buffer$   | Γ  | Π  | 1          |    |            |           | 1  |    |    |     |     | 1   |     |     |

|      | Do multiplication                     |    |    |            |    |            |           |    |    |    |     |     |     |     |     |

| 4    | read $\Delta w_{ii}$ from cache       | 1  |    |            |    |            |           |    |    |    | 1   |     |     |     |     |

| 5    | Δw <sub>ii</sub> → A                  |    |    |            |    |            | 1         |    |    |    |     |     |     |     |     |

| 6    | Do addition — B                       |    |    |            | 1  | 1          |           |    |    |    |     |     |     |     |     |

| 7    | restore $\Delta w_{ij}$ to cache,R    | 1  |    | 1          |    |            |           |    |    |    | 1   |     |     |     |     |

| 8    | load $\eta$ from G                    |    |    |            |    |            |           |    |    | I  |     |     |     |     |     |

|      | Do multiplication                     |    |    |            |    |            |           |    |    |    |     |     |     |     |     |

| 9    | load wij from cache                   | 1  |    |            |    |            |           |    |    |    | 1   |     |     |     |     |

| 10   | W <sub>ij</sub> — ▶ A                 |    |    |            |    |            | 1         |    |    |    |     |     |     |     |     |

| 11   | Do addition                           |    |    |            | 1  | 1          |           |    |    |    |     |     |     |     |     |

restore w<sub>ij</sub>

## \* Associative Reduced Micro Instruction

| Step | Micro instru description | c1 | c2 | с3 | c4 | c5 | <b>c</b> 6 | c7 | с8 | с9 | c10 | c11 | c12 | c13 | c14 |

|------|--------------------------|----|----|----|----|----|------------|----|----|----|-----|-----|-----|-----|-----|

| 1'   | Group 1,5                |    | 1  |    |    |    | 1          |    |    | 1  |     |     |     |     |     |

| 2'   | Group 2, 3, 10           |    |    | 1  |    |    |            | 1  | 1  |    |     |     | 1   |     |     |

| 3'   | Group 4, 6               | 1  |    |    | 1  | 1  |            |    |    |    | 1   |     |     |     |     |

| 4'   | Group 7, 11              | 1  |    | 1  |    |    |            |    |    |    | 1   |     |     |     |     |

| 5'   | Step 8                   |    | 1  |    |    |    |            |    |    | 1  |     |     |     |     |     |

| 6'   | Step 9                   | 1  |    |    |    |    |            |    |    |    | 1   |     |     |     |     |

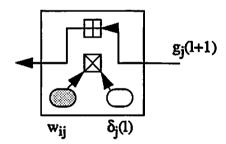

#### VMM OPERATION

\* Algorithm:

$$\delta_i(l) = \sum_{j=1}^n g_i(l) w_{ij}$$

\* Associative Ring Structure

\* Associative Data Processing Structure

\* Associative Original Micro Instruction Bus Control

| Step | Micro instru description      | c1 | c2 | с3 | c4 | <b>c</b> 5 | сб | c7 | c8 | c9 | c10 | c11 | c12 | c13 | c14 |

|------|-------------------------------|----|----|----|----|------------|----|----|----|----|-----|-----|-----|-----|-----|

| 1    | read g j (l+1) to buffer      |    |    |    |    |            |    |    | 1  |    |     |     |     |     |     |

| 2    | g <sub>j</sub> (l+1) L,output |    | 1  |    |    |            |    | 1  |    |    |     |     | 1   | -   |     |

| 3    | feach wij from cache to R     | 1  |    | 1  |    |            |    |    |    |    | 1   |     |     |     |     |

|      | Do multiplication             |    |    |    |    |            |    |    |    |    | П   |     |     |     |     |

| 4    | Do addition                   |    |    |    | 1  | 1          | 1  |    |    |    | 1   | İ   |     |     |     |

| 5    | B A                           |    |    |    |    |            | 1  |    |    |    |     |     |     |     |     |

## \* Associative Reduced approach of Micro Instruction

| Step | Micro instru description | c1 | c2 | с3 | c4 | <b>c</b> 5 | с6 | с7 | с8 | с9 | c10 | c11 | c12 <del>c</del> 13 | c14 |

|------|--------------------------|----|----|----|----|------------|----|----|----|----|-----|-----|---------------------|-----|

| 1'   | Group 1, 2, 4            |    | 1  |    | 1  | 1          |    | 1  | 1  |    |     |     | 1                   |     |

| 2'   | Group 3,5                | 1  |    | 1  |    |            | 1  |    |    |    |     |     |                     |     |

<sup>\*</sup> Time comsumiing 1x addition + 1xmultiplication

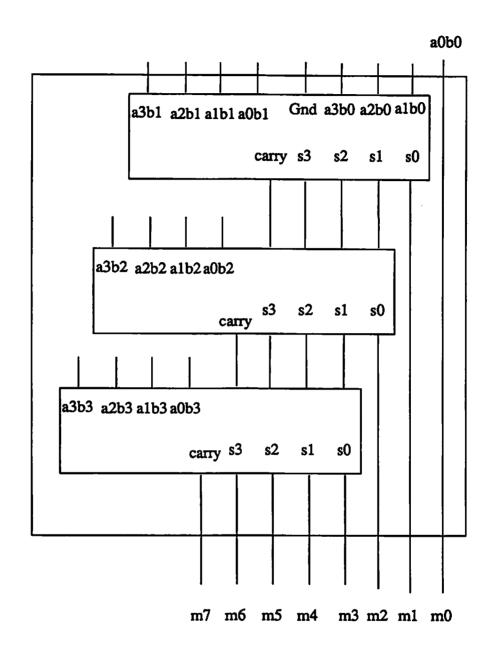

Building Block of 4x4 multiplier

- \* the three small building blocks are 4-bit carry look ahead adder

- \* time comsuming is (1xAND gate delay + 3x Carry-Look -Ahead-Adder delay)

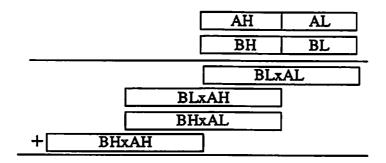

\* Algorithm for an 8x8 Wallice multiplier

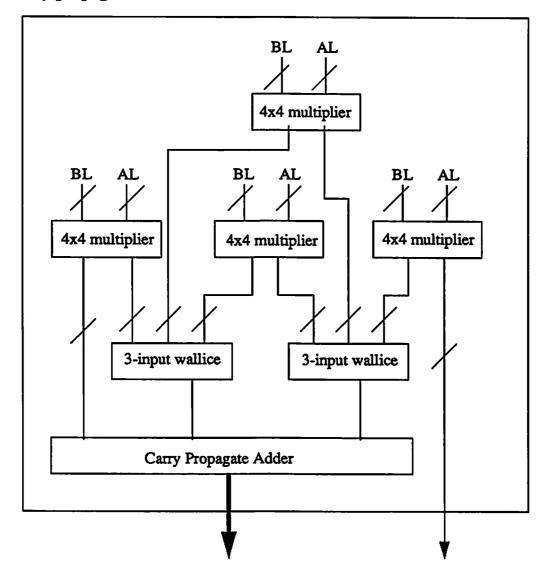

\* For an 8x8 multiplier, we need 4x4 multiplier, 3-input wallice tree, and a carry propagate adder.

# EE599 Dytal VLSI Neurocomputer Design Mike Wang Spring 1991 573-75-0171

#### **ABSTRACT**

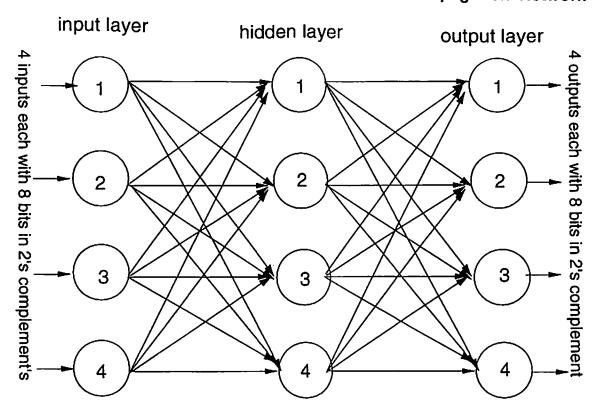

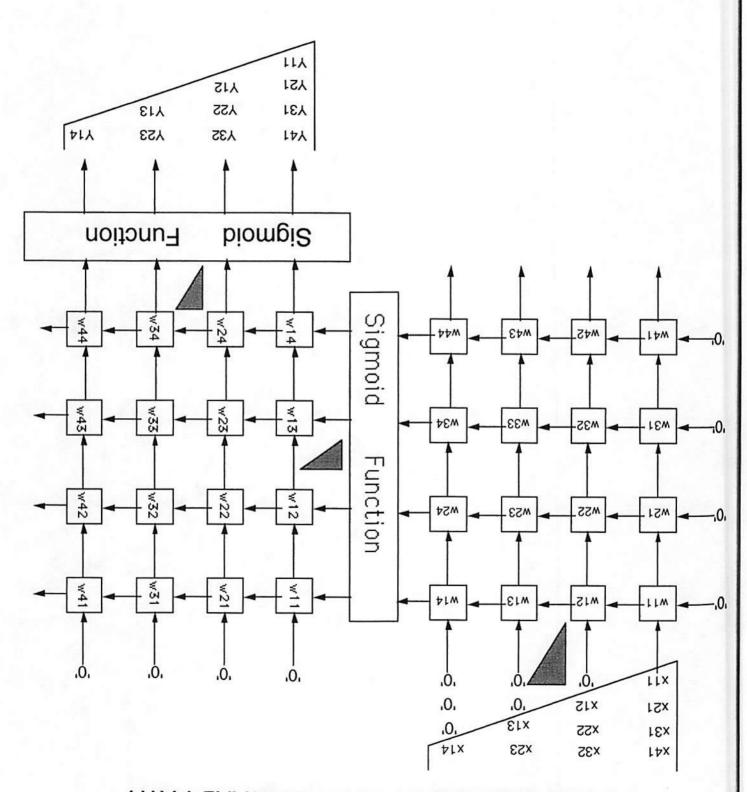

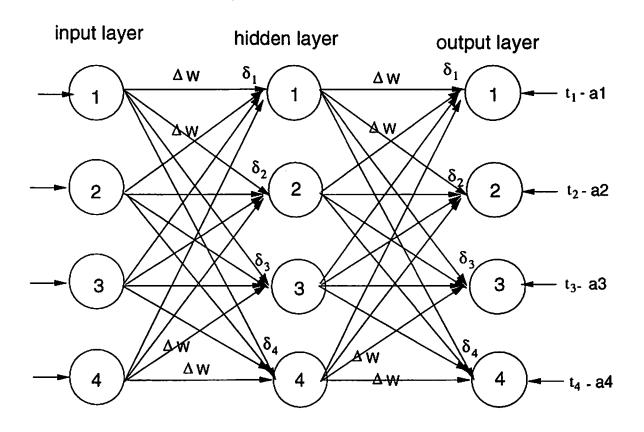

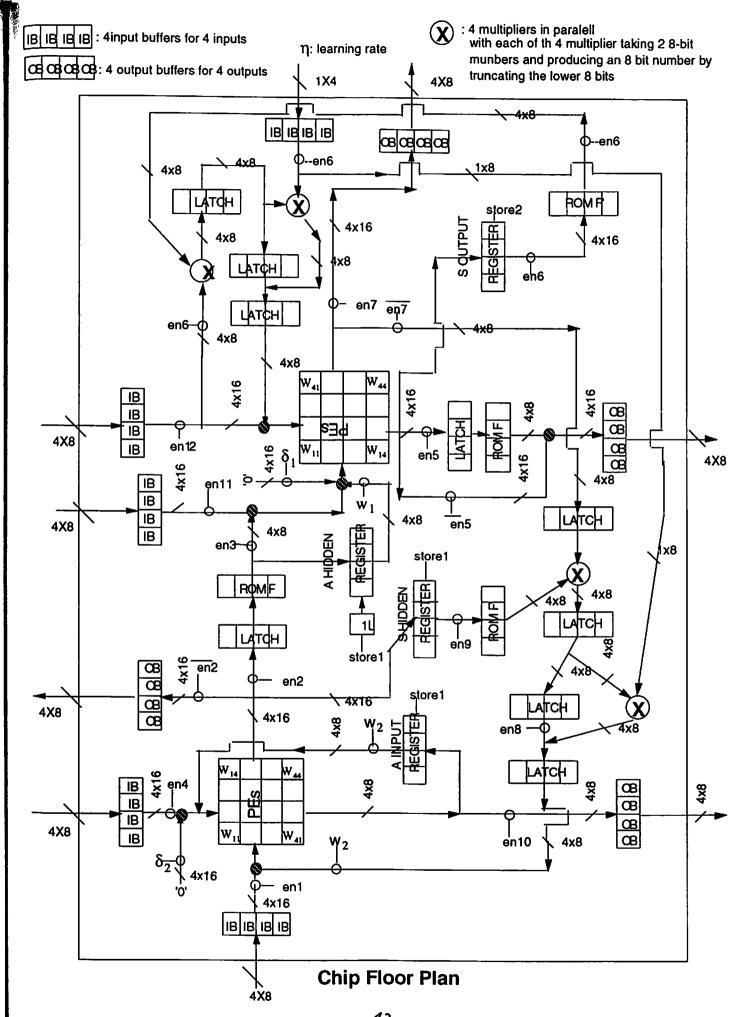

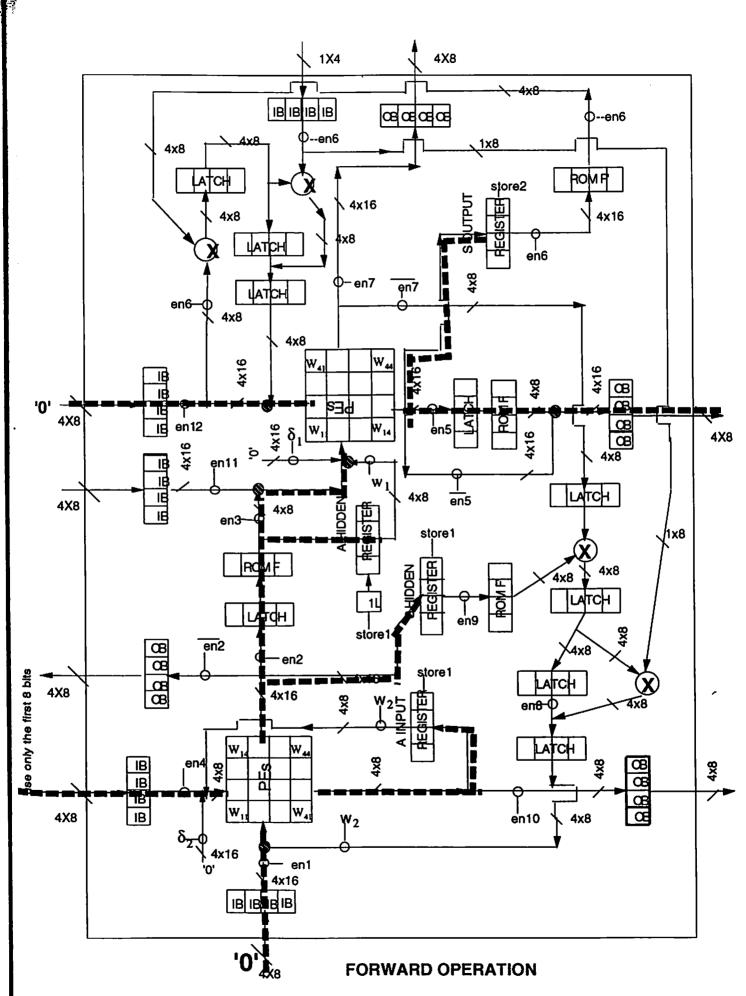

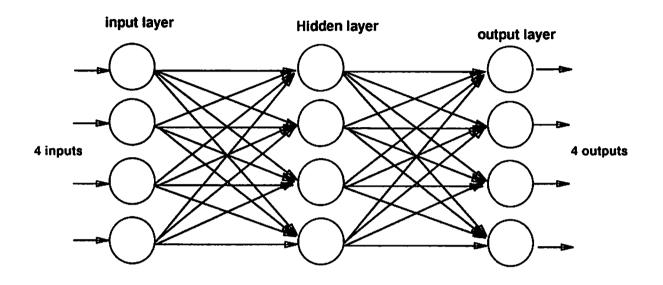

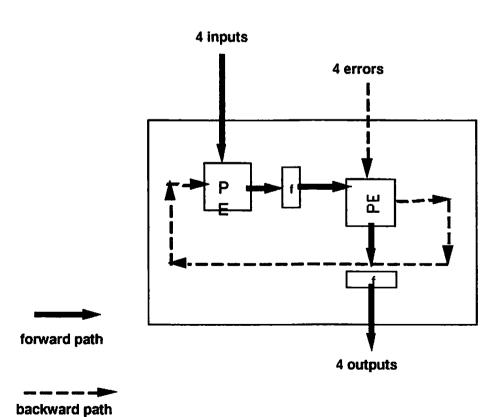

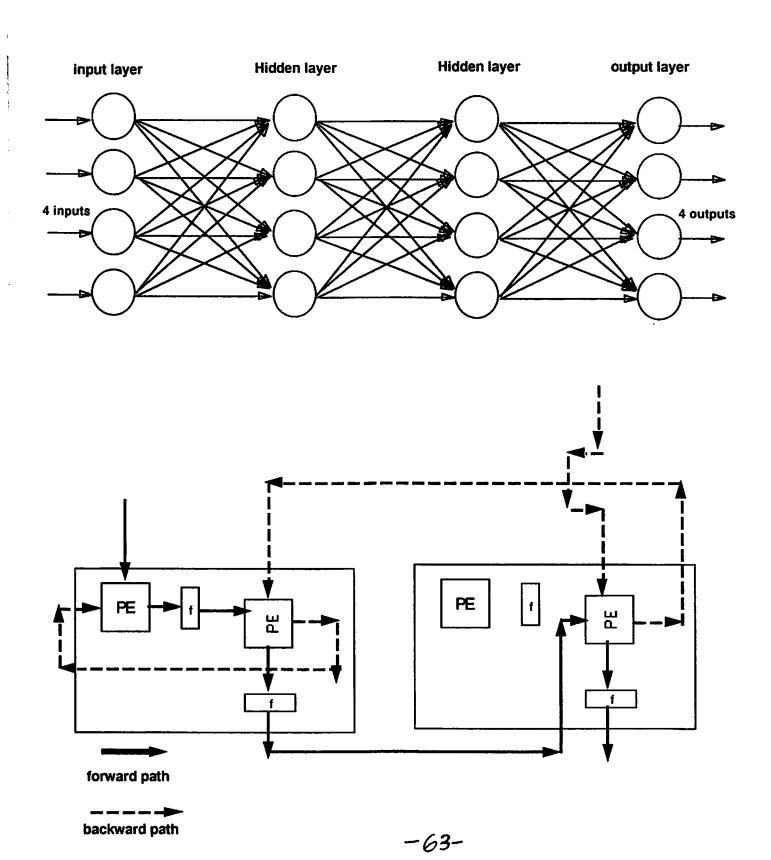

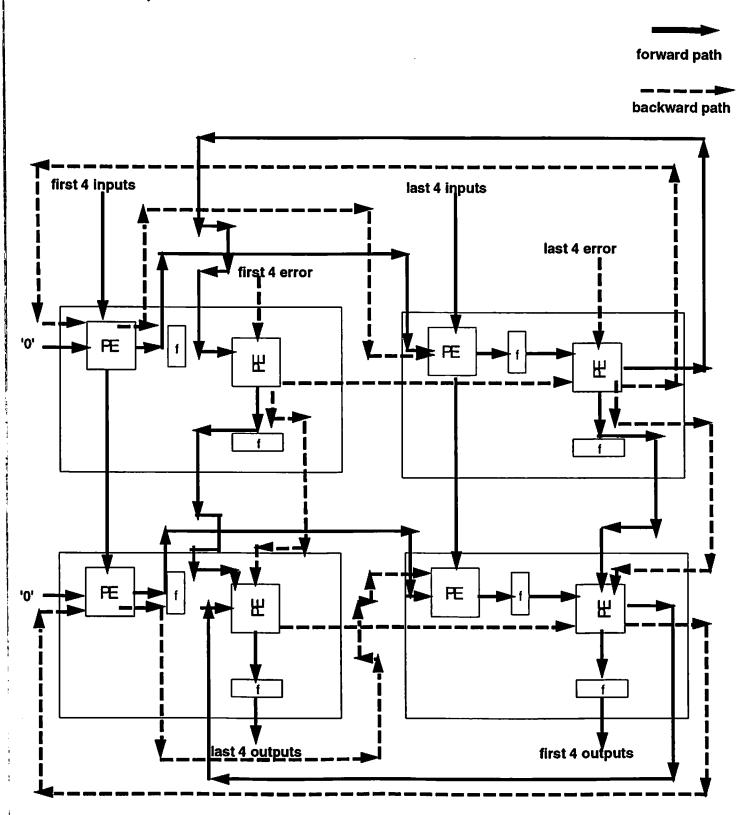

In this project, a general purpose 4-input, 4-output, 3-layered, fully-connected Back Error Propagation network is realized by using array processors. This chip is designed to be scalable and reconfigurable meaning that a network of any number of layers, inputs, outputs and connections can be realized using multi-chip configuration. Fast on-chip learning is also provided with each layer's weights updated simultaneously. Some measure of fault tolerance is also incorporated for this chip to prevent process time error from rendering the chip useless.

#### **Table of Contents**

| $\Box$ - $\alpha$ i $\alpha$ $\alpha$ | F Danari                                                               |

|---------------------------------------|------------------------------------------------------------------------|

| Projec                                | t Report                                                               |

| Apper                                 | dix                                                                    |

| (1)                                   | Network topology of a Back-Error Propagation Network                   |

| (2)                                   | Why not a systolic array                                               |

| (3)                                   | Forward / backward operations and their data flow path in PE arrays    |

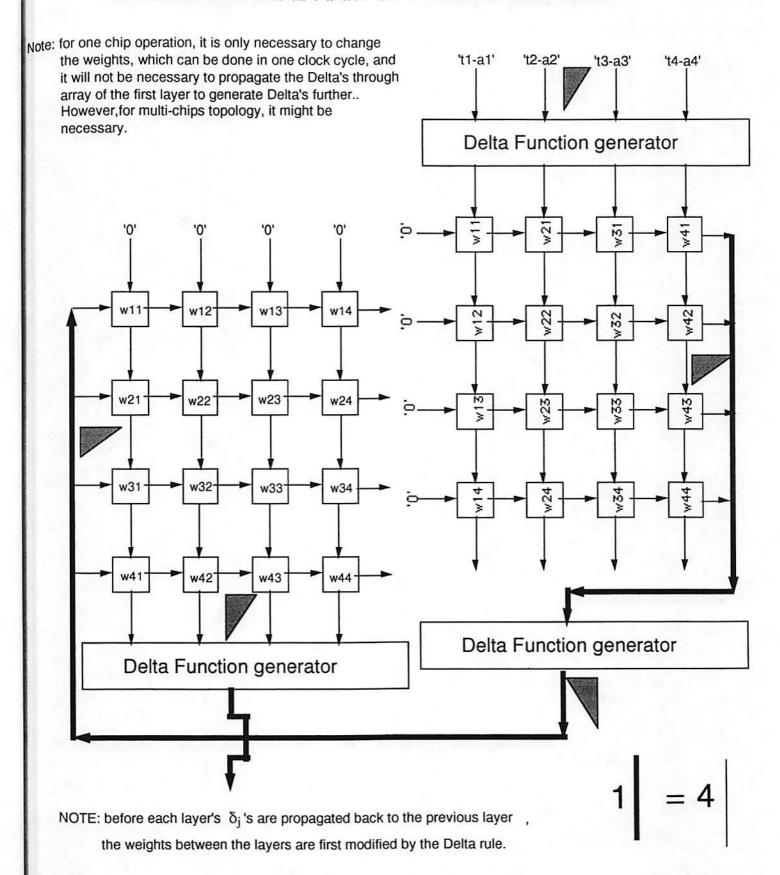

| (4)                                   | PE / chip floor plan                                                   |

| (5)                                   | data path in PE / chip for forward operation                           |

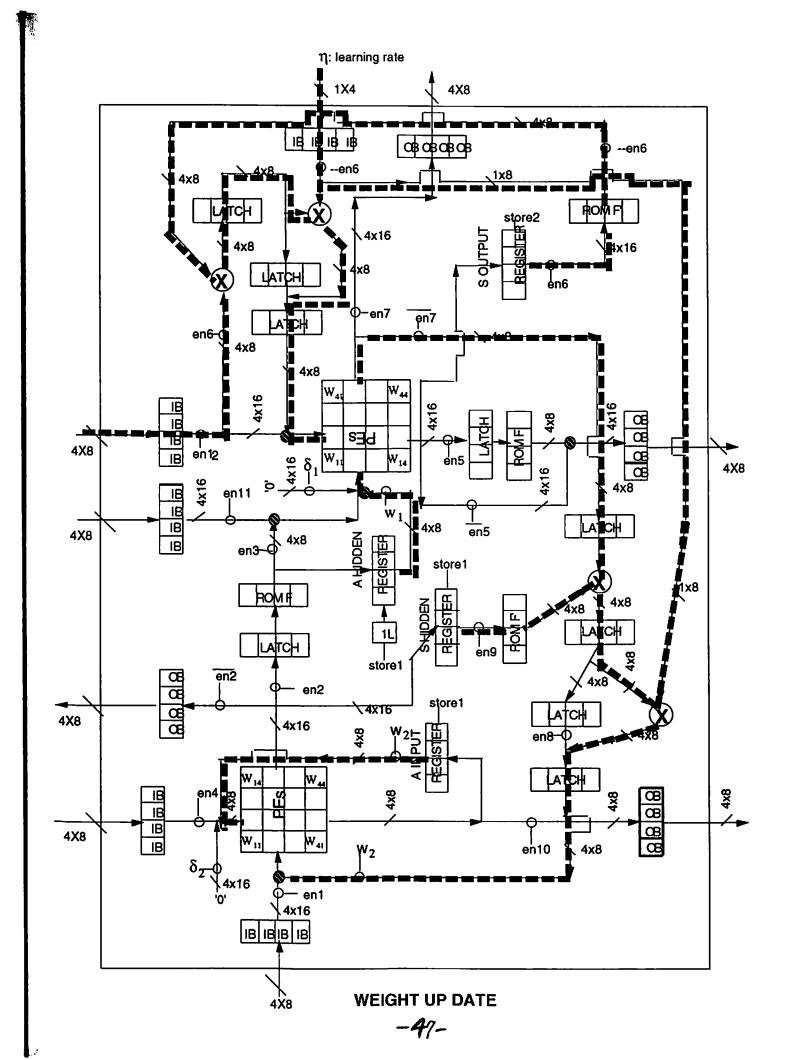

| (6)                                   | data path in PE / chip for weight update                               |

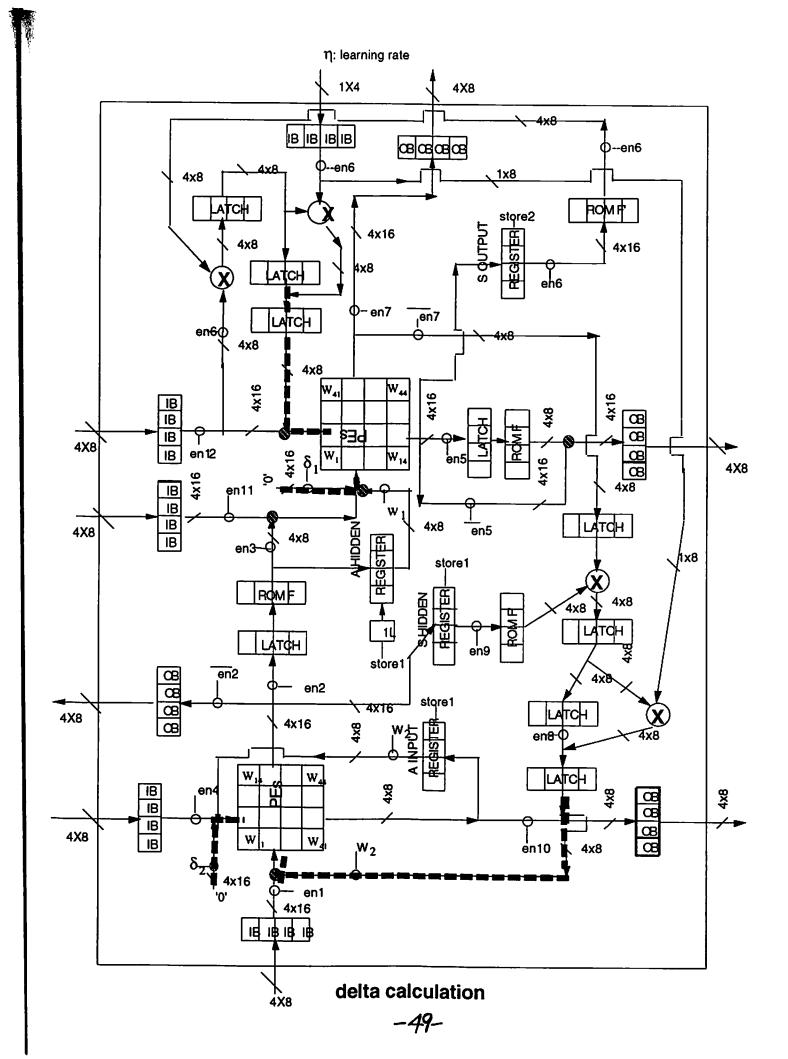

| (7)                                   | data path in PE / chip for delta calculation                           |

| (8)                                   | signals and operation                                                  |

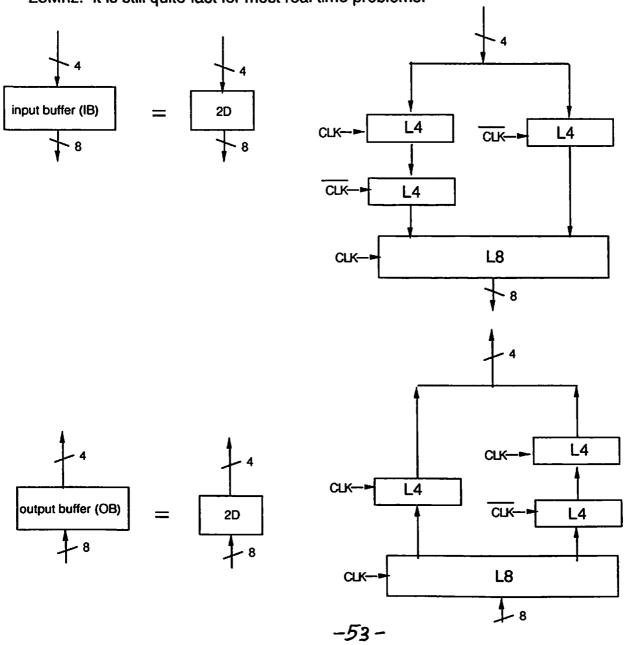

| (9)                                   | I/O buffer design                                                      |

| (10)                                  | Fault tolerance design with example of data flow in case of PE failure |

| (11)                                  | Sigmoid and Sigmoid prime realization with quantization error          |

| (12)                                  | multichip configuration                                                |

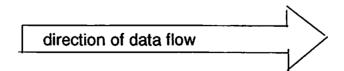

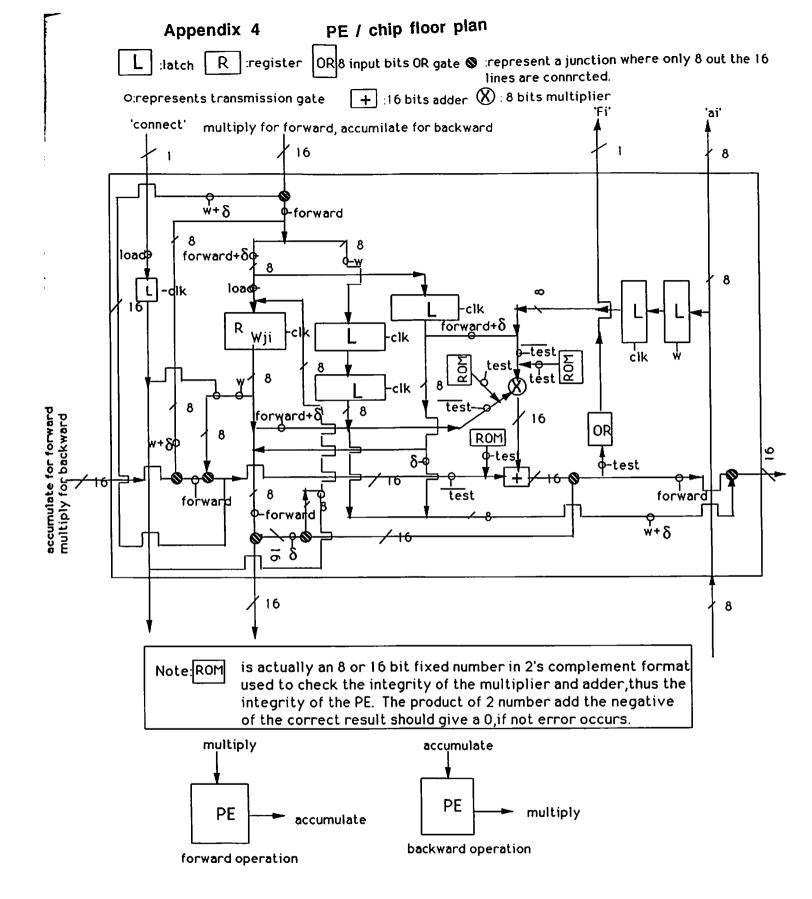

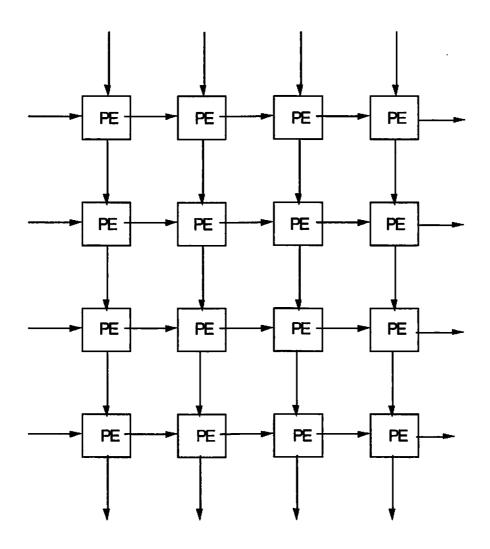

In this project, a general purpose 3-layer, 4-input, 4-output Back-Error Propagation network is realized by using array processor design. The choice is made due to its following advantages:

- (1) fast forward propagation time: the I/O can be pipelined in and out of the chip with pipeline period  $\alpha = 1$ .

- (2) it offers on-chip, local, simultaneous weight updates. This enhances the learning speed of the algorithm.

- (3) weights can be both loaded and unloaded before and after training process, so one can store the trained weights for different applications and just load the appropriate weight among different learned applications.

Two 4x4 arrays of PE's are used to realize the network. As S.Y. Kung suggested, each array can be further projected into a 1X4 systolic array. However, as pointed out in the appendix, this method suffers the drawback that the I/O can not be pipelined, and the I/O rate is effective 1/4 of that of the 4x4 design. There is thus a trade-off between speed and area used. Moreover, the systolic array design will be unsuitable for training as it has longer training time and will have to use either additional dedicated circuitry or off-chip learning. The 4x4 array is very suitable for the learning process as the data for backward propagation actually travel along the transpose of the array. It is also shown in the appendix that as the problem size grows, the time required for learning actually grows almost linearly. This is again a very good reason for choosing this design method.

As compared with some commercial products, this chip definitely has less number of neurons and synapses. However, it can be easily explained as follows:

- (1) this design tries to maximize the speed of operation at a cost of area used. Most of the commercial chips use memory to store information of synapse weights and neuron outputs, and the PE's are actually shared among neurons. However, that will result in a slower chip, especially for learning.

- (2) because actual layout of chip is not done, so only an estimation of the numbers of PE's is given. From the EE599 VLSI for DSP class project, I found out that a PE with an 8 bit multiplier, a 16 bit adder, and many latches and registers will occupy approximately  $1020\lambda$  x1459 $\lambda$  of area. If 1um technology is used, a PE will results in 0.015 cm<sup>2</sup> of area.

So two 4x4 array will result in about 0.5 cm<sup>2</sup> of area. Therefore, conservative estimation was given for the array size thus the number of neurons and synapse weights.

(3) since this chip is scalable and reconfigurable, multi-chip configuration can be used to increase the network to any size the problem requires.

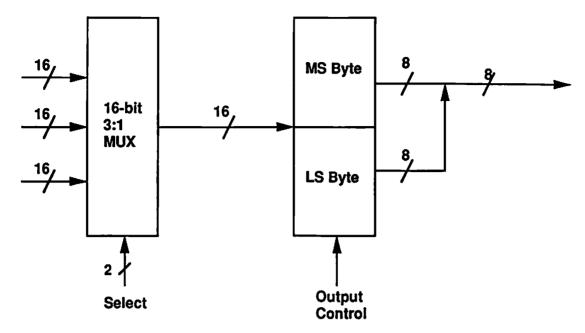

Moreover, from the VLSI DSP class project, it was found out that the PE can finish all required operation within 20ns. Thus, a 50 Mhz system clock is used for this chip. However, because of this chip is designed to be scalable, the number of pins on the chip is large. In order to constrain the pin number to be within 300, the I/O is forced to multiplex its higher byte with its lower byte thus results in an I/O rate of 25 Mhz. This is still in reasonable range of speed. This is a trade-off between the number of pins on IC (the scalability) and the speed of I/O operation.

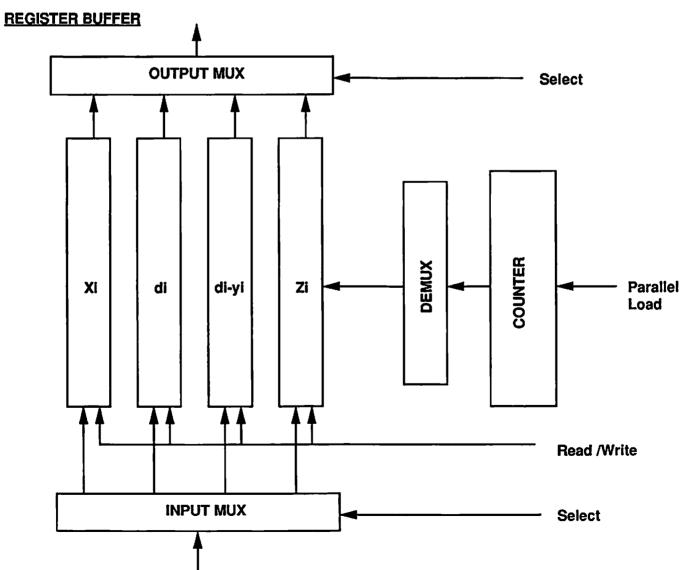

Since each PE must be able to take data for both the forward and backward operations, it must have 16-bit data bus for all its 4 sides. Some kind of routing is required within each PE, and special design consideration is also given as some 16 bits and 8 bits data lines have to connect. Because each of the 4 sides of a PE has a 16-bit data bus,

the number of pins on the chip is therefore large as seen from the chip floor plan. This can be improved if the weights within the PE arrays can be switched to realize the transpose of original array. However, additional connection and logic circuit will be required. So for simplicity, it is not implemented this way.

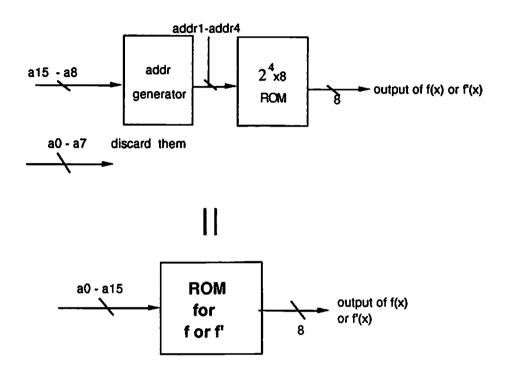

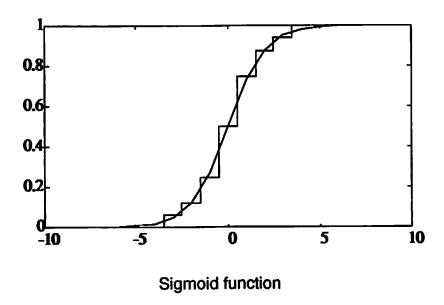

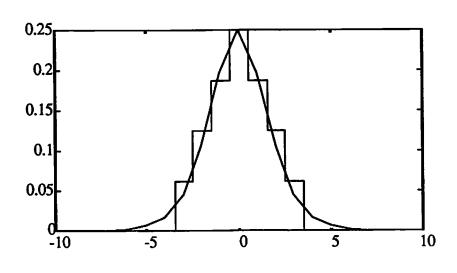

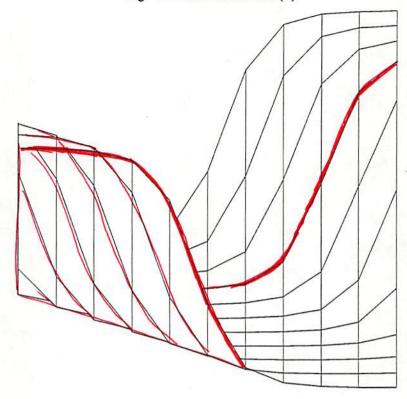

Each of the sigmoid function and its prime is realized by using table look-up from a 16x8 ROM circuit on the chip. I chose 16 points because I want to use as small of an area as possible to realize these functions. The results are shown in appendix with quantization error also. One can increase the precision easily by following the analysis in the appendix.

Even though the array processor approach looks straightforward on the surface, beneath it are many design choices, trade-offs and difficulties. There remain many optimizations to be done in both the system level and physical layout level. Nevertheless, the proposed architecture provides a very good starting point for a full IC design process.

Appendix 1

## Network topology of a Back-Error Propagation Network

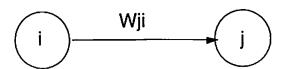

THE WEIGHTS BETWEEN 2 NEURONS ARE DEFINED AS THIS

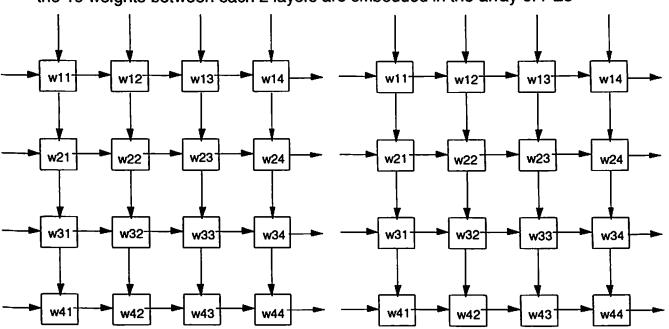

the 16 weights between each 2 layers are embedded in the array of PEs

**NETWORK TOPOLOGY**

### For Backpropagation network

### Forward Operation:

the data propagate from input to output layer.

for input unit, output of neuron i= input at neuron i =ai for hidden and output layers, the neuron output is calculated as follows:

$$S_{j} = \sum_{i} a_{i} w_{ji}$$

$$a_{j} = f(S_{j}) = \frac{1}{1 + \exp(S_{i})}$$

### **Backward Operation:**

the data propagate from output layer back to input layer.

for output layer:

$$\delta_j = (t_j - a)$$

f'(  $S_j$ ) where  $t_j$  is the trained pattern

for all hidden layers, it is necessary to change weights between it and the previous layer first, then one can calculate the delta for the hidden layer.

for the hidden layer:

$$\delta_{j} = \begin{bmatrix} \sum_{k} \delta_{k} w_{kj} \end{bmatrix} \qquad f'(S_{j})$$

NOTE: for backward propagation, the transpose of the W matrix is used while for forward operation it is W that is used

### Appendix 2

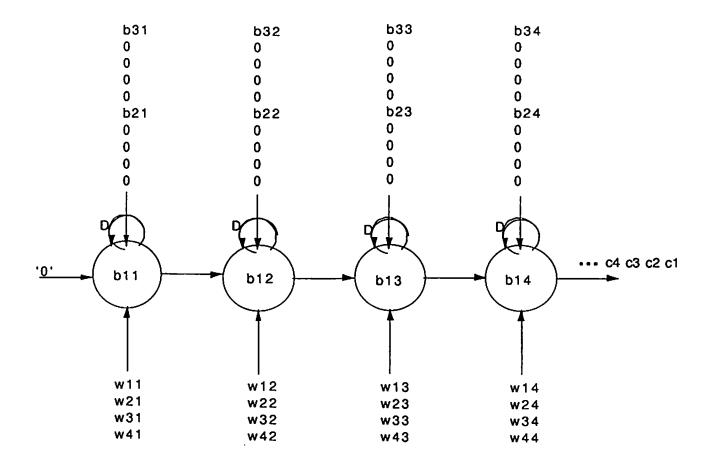

### Why Not a Systolic Array

$[W] \times [b] = [c]$

where bi1 - bi4 represent the ith set of data

As can be seen from above, even though the output is one number each clk cycle, the input can only be applied every 4 clk cycles-- it is not pipelined. So the effective rate for input and output is 1/4 of that using a 4x4 array. This may render the chip unsuitable for real-time processing. This is a trade off between hardware and speed.

Moreover, the systolic array is not suitable for calculating weight changes, and dedicated hardware or off-chip learning may become necessary. So the 4x4 array actually makes design simpler and learning faster than what the systolic array can offer. There is again some trade off of hardware vs.simplicity and speed.

## Appendix 3

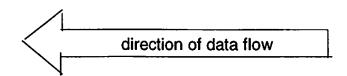

# Forward / backward operations and their data flow path in PE arrays

# **Forward Operation**

# HTA9 GRAWRON OF FORWARD WOJN ATAG

# **Backward Operation**

## DATA FLOW DIADRAM OF BACKWARD PATH

Note :because ai is a broadcasted signal, the weight update for the whole array can be done locally and simultaneously in one clock cycle

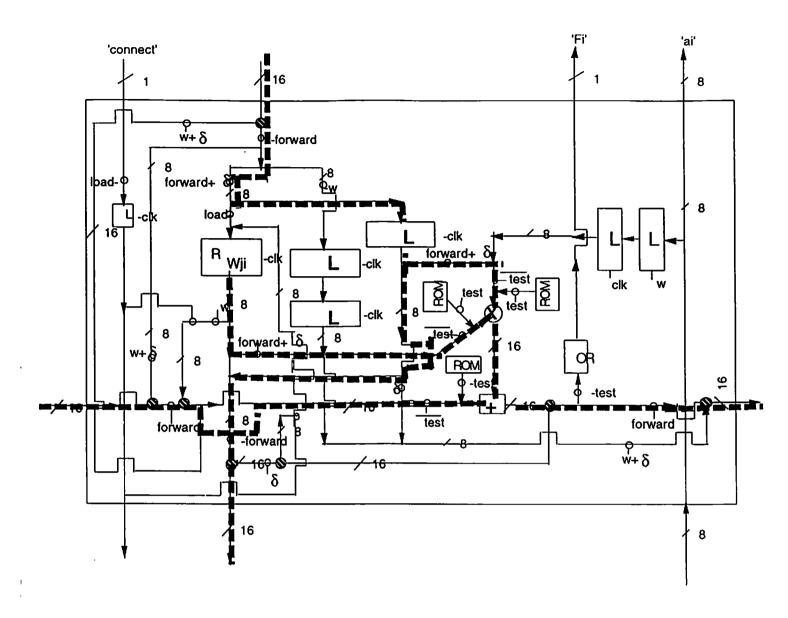

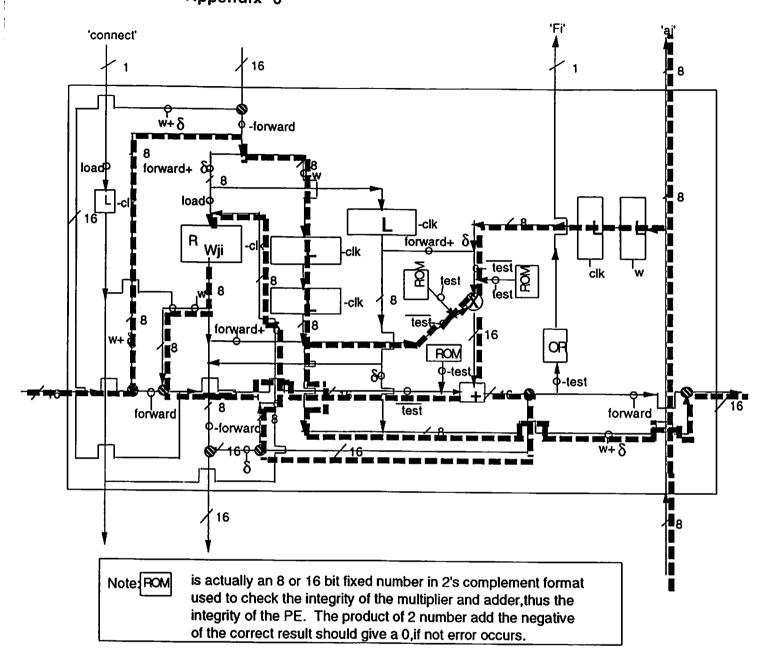

PE Wji Floor Plan

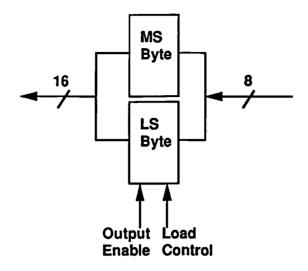

Note: becaust the same PE is used for both forward and backward operation with one side being able to take either 8 or 16 bits of inputs ,it is necessary to make them all 16 bits with some bits not necessaryly connected for different operations. This cause the need for the connector shown in the flow plan.

this connector simply outputs the higher 8 bits of the 16 bits input signal or puts the 8 bits input to the higher byte of the 16bits number

Appendix 5 data path in PE / chip for forward operation

Appendix 6 data path in PE / chip for weight update

# **WEIGHT UPDATE**

## Appendix 8 signals and operation

### Signals and Operation

On the chip there are the following signals that need to be fed by the host

| test                                                      | self test for fault tolerant connection path set up             |

|-----------------------------------------------------------|-----------------------------------------------------------------|

| load                                                      | load wji's                                                      |

| forward                                                   | help each PE to make the right connection for forward operation |

| en1-en12                                                  | set up the topology for either multi- or uni- chip operation    |

| connect1-8                                                | to make the network not fully connected                         |

| store1                                                    | store first layer's ai and Si                                   |

| store2                                                    | store 2nd layer's ai and Si                                     |

| cik                                                       | system clock which is about 1/20ns =50Mhz                       |

| Vdd                                                       | power supply                                                    |

| G//D                                                      | power supply                                                    |

| w 1                                                       | change 2nd layer weights                                        |

| w 2                                                       | change the first layer weights                                  |

| $egin{array}{c} egin{array}{c} eta_1 \ eta_2 \end{array}$ | calculate the 2nd layer delta's                                 |

| $\delta_2$                                                | calculate the ast layer delta's                                 |

there are 32 pins required for the above 32 signls with the (4x8)x8+4=260 pins on the chip floor plan, there are a total of 292 pins on this chip . this rather large number of pins id due to the fact that this chip is fully scalable-- any number of neurons and layers are possible.

For one chip operation, there are 4 phases to consider

- (1) test phase

- (2) load phase

- (3) forward phase

- (4) backward phase

### TEST PHASE

the test signal nees to be on for one clock cycle, and at the end of next cycle the connection logic circuit should have the topology set up since it only employs simple 2 level logic. If more then 2 PE's in an array are detected faulty, the chip shoule be rejected at the production stage by using testing probes.

#### LOAD PHASE

wi1 wi2 wi3 wi4 (weights in each row) are pipelined down when the signal load is On. It takes 1 clock cycle to load one row, so for 4 rows it takes 4 clock cycles to finish the loading. Note for the 2nd array of weights, because its topology is the transpose of the first array, so we have to enable the  $\delta_1$  signal as well. This is generally true for any hidden layer weights

it is also necessary to load the connect bits to determine if the synapse connection exist. If a connection between neurons does not exist, the corresponding weight is loaded as '0' and also the corresponding connection bit is set to '0' to prohibit future weight update, so that weight remains at '0'

#### FORWARD PHASE

after the weights have been loaded, we can apply the following signaltoestablish the right path for forward phase en1 en2 en3 en4 en5 en12

all these signals must be '1' during the period of forward training. All the other eni's are set to '0' for 1 chip operation.

Note: if the net work has been properly trained, it will not need to apply the backward phase, and the input can be pipelined into the system, and the output will be pipelined out at the same rate. Because the number of pins is very large, it was necessary to multiplex the higher byte with the lower byte for both the input and output. Thus, the rate data does in and comes out is half of that of the system clock, so the speed is about 25 Mhz which is still O.K. for most applications.

If backward operation is to be expected, store1 and store2 should go to '1' to enable the weighted sum Sj and neuron output ai to be stored. For one chip operation, it 2 latches and 4 PE's (6 clk cycles) to finish the first signal propergation, and it should be kept on for 4 clk cycles for all the pipelined signal to be captured. Similar comments can be applied to store2 signal.

#### **BACKWARD PHASE**

this is necessary for the network to learn to adjust the weights for proper operation, after one forward operation has completed for one input set, thehost computer compares the answer with the desired answer, and the error ti-ai are fed back. the following signals have to be set to ;'1' for proper operation topology en6 en9 en8, and en7 is set to '0'

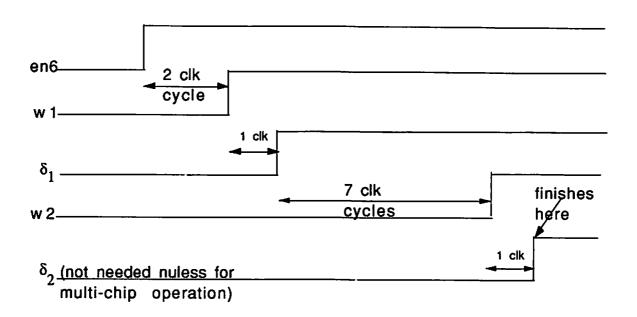

there are also other signals that can go on only at the right time and they are shown as below

note: it takes 11 clk cycles to finish 1 chip backward phase, and out of which 7 is the big factor. But the 7 cycles consists of 3 latches used for 2 multiplications and 4 cycles for signals to propagate down the array. So it is obvious that as the array size increases using many chips, the learning time will increase almost linearly with the arrsy size or problem size. This is actual an indication of pretty fast learning time as in many case the learning time will vary expotentially with the problem size. There are some unused signals which will be necessary for multi-chip topology.

# I/O BUFFER DESIGN

Since this chip is design to be scalable - being able to expand the number of neurons and layers, it will be inevitable to have many pins on the chip for this off-chip interconnection purpose.

Therefore, the I/O has to be multiplexed so the first 4 bits of data is fed in/out first, then at the next clock cycle the last 4 bits. So the speed is effectively reduced by half. This is a trade off between speed and flexibility and expandability

But since the clock is about 50Mhz, the data I/O is then about 25Mhz. It is still quite fast for most real time problems.

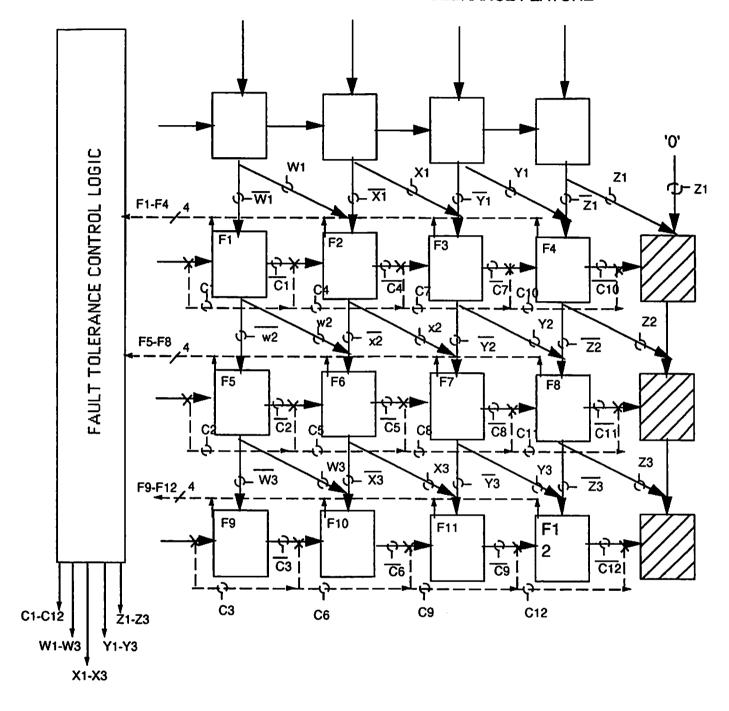

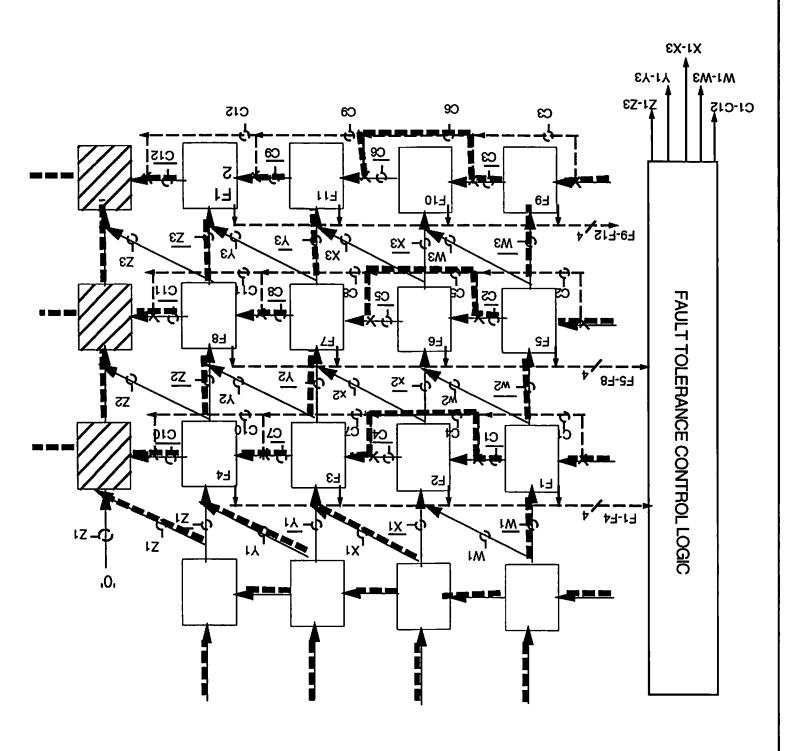

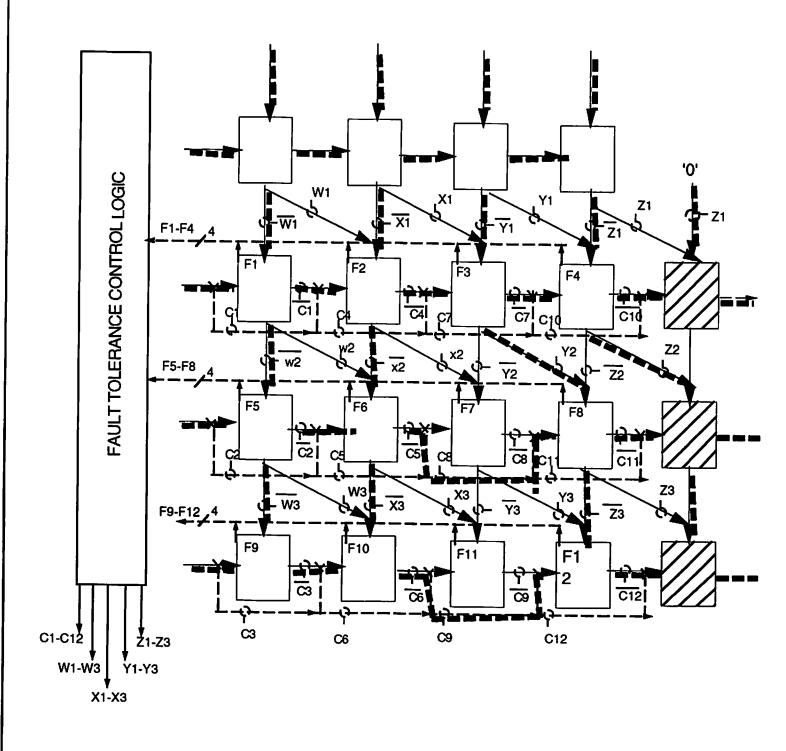

Appendix 10 Fault tolerance design with example of data flow in case of PE failure

## THE REAL ARRAY OF PE'S WITH FAULT TOLERANCE FEATURE

The control logic generate output signals to establish the right connection among PE's so we will have a virtual 4x4 standard array.

For simplicity, all the rest diagram will employ only the virtual PE array, and it should be understood that the real array actually looks like this diagram.

Chip fails if for each PE arrays more than one Fi are '1'

The Fi in each chip is generated in the TEST phrase of this chip operation. It uses the stored numbers in the PE and multiplt 2 of then then subtract the other. If the subtracted number is the correct number, 16 bits of '0' will result. These correctness of the operation can then be checked by ORing these 16 bits. If the result is wrong, the OR will output a '1' for the Fi. Otherwise, it will be '0' for correct operation.

If any one of the 12 lower 3 rows of PE's fails (any one of the signals F1-F12 goes to '1'), the 3 shaded duplicated PE's will operate. But no more than 1 PE can fail in the array -- if so, chip fails.

The cortrol logic inputs F1 -F12 and outputs the Following signals W1-W3, X1- X3, Y1-Y3,Z1-Z3, C1=C12, and they are as follow

| W1=F1       | X1=F1+F2    | Y1=F1+F2+F3 | 3            |

|-------------|-------------|-------------|--------------|

| W2=F5       | X2=F5+F6    | Y2=F5+F6+F7 | 7            |

| W3=F9       | X3=F9+F10   | Y3=F9+F10+F | -11          |

| C1=W1       | C4=X1       | C7=Y1       | C10=Z1       |

| C2=W1+W2    | C5=X1+X2    | C8=Y1+Y2    | C11=Z1+Z2    |

| C3=W1+W2+W3 | C6=X3+X2+X1 | C9=Y1+Y2+Y3 | C12=Z1+Z2+Z3 |

And here are some example of how it works

Example of array data flow in case of a PE failure Let F2=1

Example of array data flow in case of a PE failure Let F7=1

## THE VIRTUAL ARRAY OF PE'S

### Realization of Sigmoid and Sigmoid Prime Functions

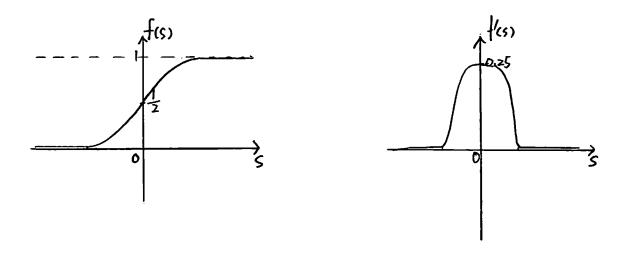

Sigmoid function f(x)=1/(1+exp(-x)) and its first derivative Sigmoid Prime  $f'(x)=exp(-x)/(1+exp(-x))^2$  can be generated by basically 2 methods

- (1) using analog circuits, but this requires A/D and D/A operations, which may complicate the design and the circuits are not reliable.

- (2) using table look-up which is a lot simpler and straight forward.

However, since both operands for multiplication are 8 bits 2's complement numbers, the resulting number must be 16 bits long. Therefore, ideally we need a RAM or ROM part that converts an16 bits input address number to a 8 bits data output. This is a 64kx8 memory capacity which is definitely too large for this application, especially many of them have to be used by this chip to achieve the pipeline operation.

Nevertheless, since both f(x) and f'(x) pretty much saturate beyond x=+5 and x=-5, with a little logic we can closely approximate these functions by using only a few of the 16 address bits.

As an example, if I only want to choose 16 points to approximate these functions, and the inputs and outputs of multiplication are as below:

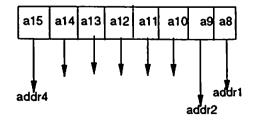

We can just choose the higher 8 bits for address generation of the 16 numbers as follows

if a15 =0 (positive number),addr3=1 if any of a10 to a14 =1.

if a15 =1 (negative), addr3=1 if all of a10 to a14 are 1

This selection makes any number less than -8 equal -8 and any number greater than 7 equal 7.

addr3= a15 (a10+a11+a12+a13+a14)+a15 (a10 a11 a12 a13 a14)

## and conceptually it looks like the following

and here are some data for this implementation

| input number  | addr4-addr1 | output for f      | outputfor f       |

|---------------|-------------|-------------------|-------------------|

| 7 and up      | 0111        | 0001.0000= 1      | 0000.0000= 0      |

| 6 to 7        | 0110        | 0001.0000= 1      | 0000.0000= 0      |

| 5 to 6        | 0101        | 0001.0000= 1      | 0000.0000= 0      |

| 4 to 5        | 0100        | 0001.0000= 1      | 0000.0000= 0      |

| 3 to 4        | 0011        | 0000.1111= 0.9375 | 0000.0001= 0.0625 |

| 2 to 3        | 0010        | 0000.1110= 0.875  | 0000.0010= 0.125  |

| 1 to 2        | 0001        | 0000.1100= 0.75   | 0000.0011= 0.1875 |

| 0 to 1 and -1 | 0000        | 0000.1000= 0.5    | 0000.0100= 0.25   |

| -1 to -2      | 1111        | 0000.0100= 0.25   | 0000.0011= 0.1875 |

| -2 to -3      | 1110        | 0000.0010= 0.125  | 0000.0010= 0.125  |

| -3 to -4      | 1101        | 0000.0001= 0.0625 | 0000.0001= 0.0625 |

| -4 to -5      | 1100        | 0000.0000= 0      | 0000.0000= 0      |

| -5 to -6      | 1011        | 0000.0000= 0      | 0000.0000= 0      |

| -6 to -7      | 1010        | 0000.0000= 0      | 0000.0000= 0      |

| -7 to -8      | 1001        | 0000.0000= 0      | 0000.0000= 0      |

| -8 and down   | 1000        | 0000.0000= 0      | 0000.0000= 0      |

# Graphs of f(x) and f'(x) showing quantization error

Sigmoid function prime

## Appendix 12

# multichip configuration

## One Chip Operation With Simplified Data Flow

## 2 chips can be used to realize a 2 hidden layers network

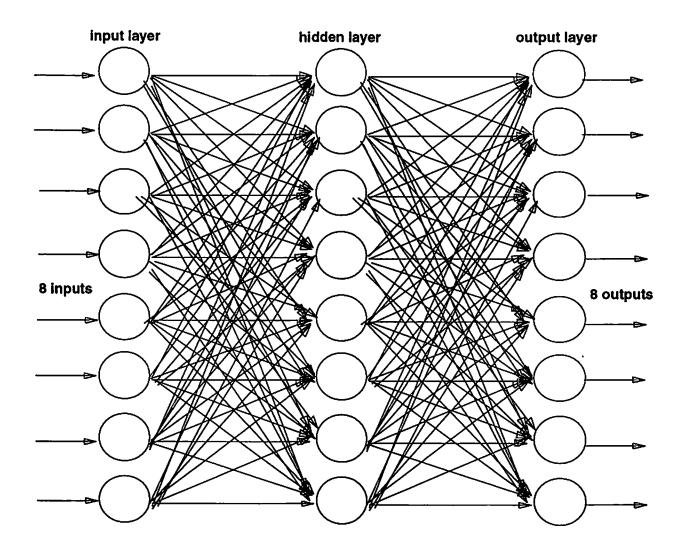

A 3-layer, 8-input, 8-output net work can be implemented by using 4 chips shown on the next page

A 3-layer, 8-input, 8-output net work can be implemented by using 4 chips shown below

## EE599 VLSI Neurocomputing Term Project

04/29/91

Name: OKADA, Hiroto

SS.# 602-38-7312

Title: A Study of an Application of the Back-propagation Network

for the Surface Reconstruction.

### 1. Abstract

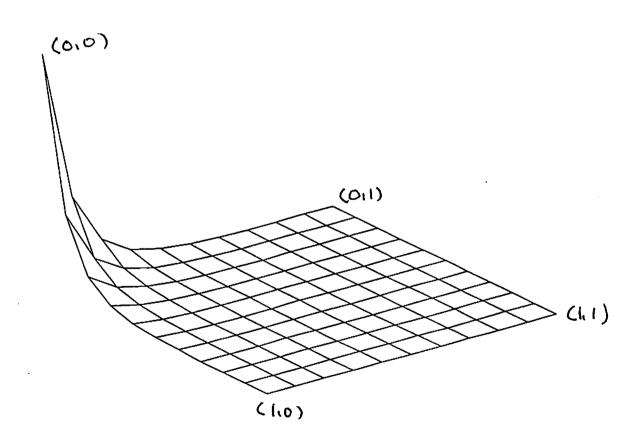

In this project, the software simulation of surface reconstruction using the back-propagation network has been reported. Surface reconstruction from sparse data has a lot of application because it can recover the 3 -D shapes of objects. For example, the inspection of products in a factory to distinguish no-good items from good items (\*), the robotic eyes to find obstacle shapes from sensory data. The Neural Network is considered to demonstrate its strong features for surface reconstruction, because the relationship between the output (surface) and the input data (ex. sensory data) can not been known clearly. The neural network can construct the relationship in its system by learning. (actually, the surface reconstruction using the neural network is getting popular.)(1) We have chosen the back-propagation network, because there is the theorem proven which guaranty that the back propagation network can appropriate any functions in real world. For practical implementation, the initial conditions (the initial weights, the number of the hidden layers, and hidden layer neurons) should be defined appropriately to get the global minimum. Through the simulation using Matlab, the network for XOR, AND, and OR functions has been discussed. An approach to general functions has also been discussed.

### 2. The background theorem

Surface reconstruction using the backpropagation network is supported by the following theorem.(2)

Theorem: Given any  $\varepsilon > 0$  and any  $L_2$  function f:  $[0,1]^n -> R^m$ , there exists a three-layer backpropagation neural network that can approximate f to within  $\varepsilon$  mean squared error accuracy.

Although "three layers are always enough" in solving real-world problems it is often essential to have four, five, or even more layers. We also realize that although the theorem guarantees the ability of a multilayer network with the correct weights to accurately implement an arbitrary  $L_2$  function, it does not comment on whether or not these weights can be learned using any existing learning law.

## 3. The back-propagation network

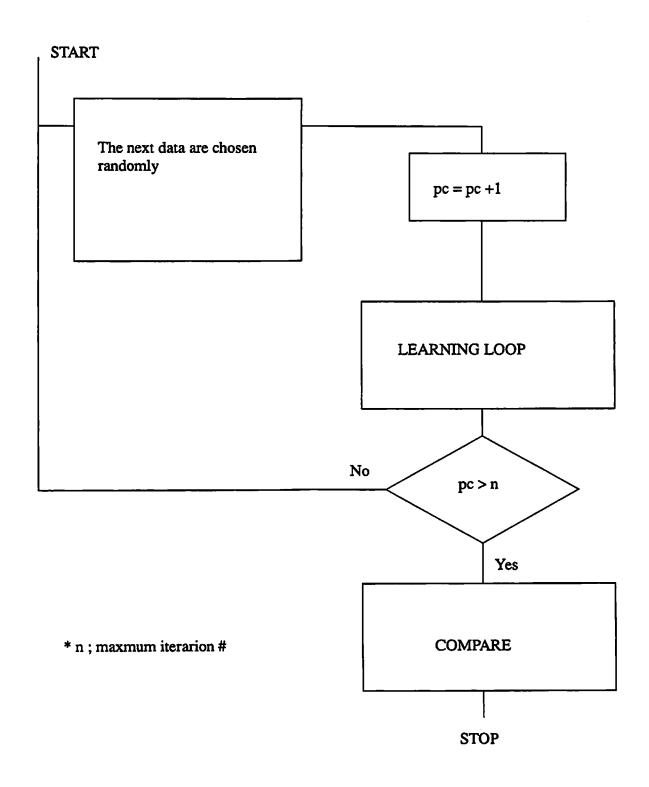

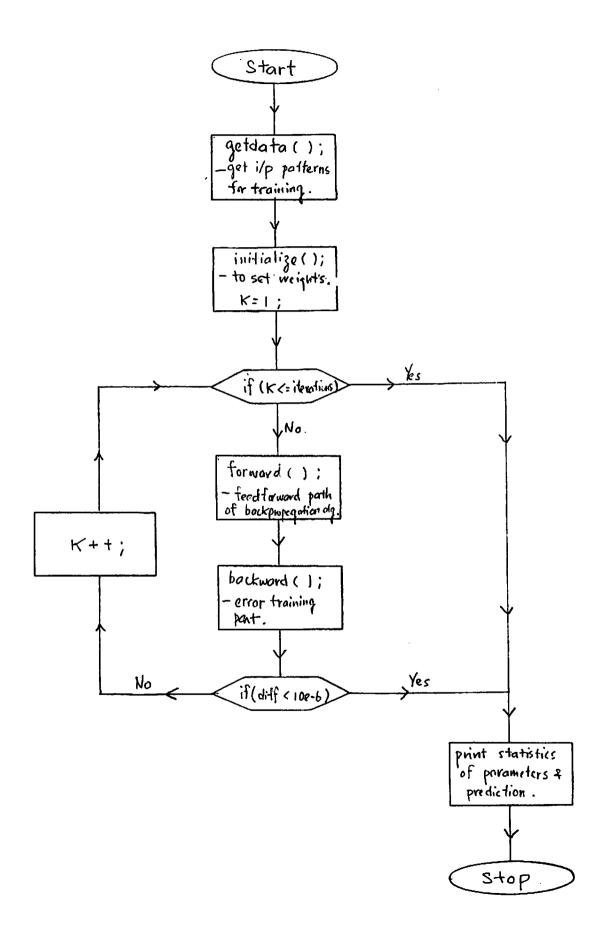

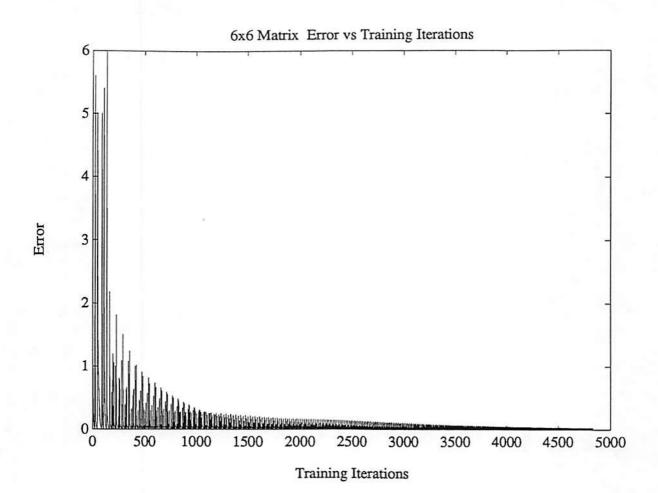

The back-propagation network, and algorithm shown in Fig. 1 (the one discussed in the class.)has been used.

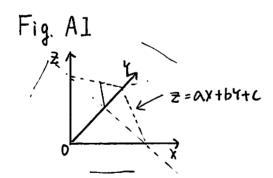

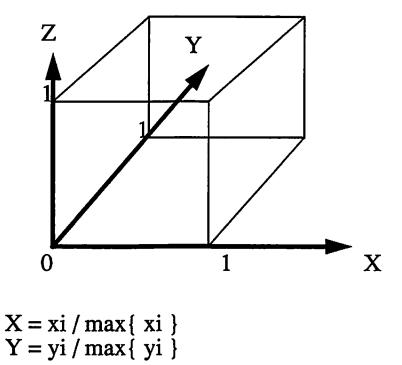

The input and output ranges are normalized to [0,1], because the output is limited by the output range of the sigmoid function, [0,1]. (Fig.2)

### 4. The simulation of XOR, AND, OR functions

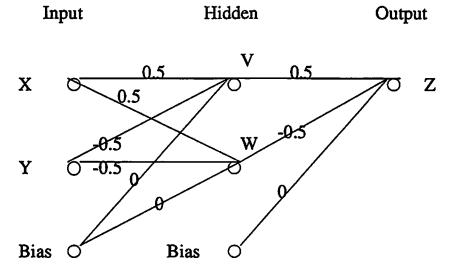

The simulation of XOR function (the one in Home work #4), AND, and OR functions are discussed as ones of simple cases. For each function, there are four input patterns. (Fig.3) The network used consists of the input layer of 2 input nodes and 1 bias node, 1 hidden layer which has 2 hidden nodes and 1 bias node, and 1 output node in a output layer. (Fig.4)

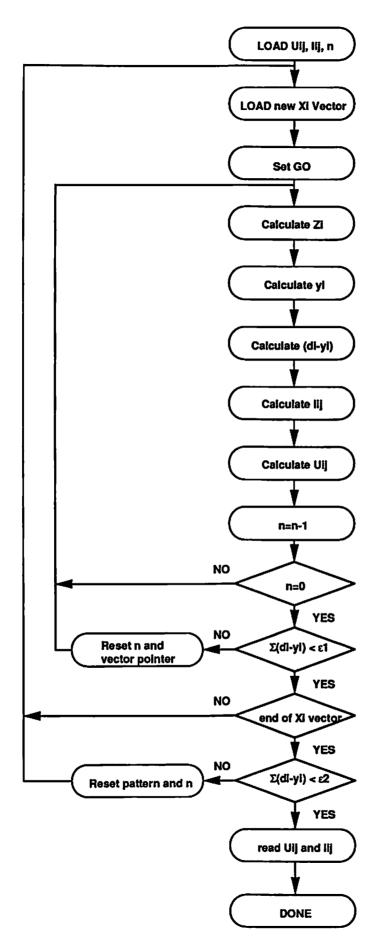

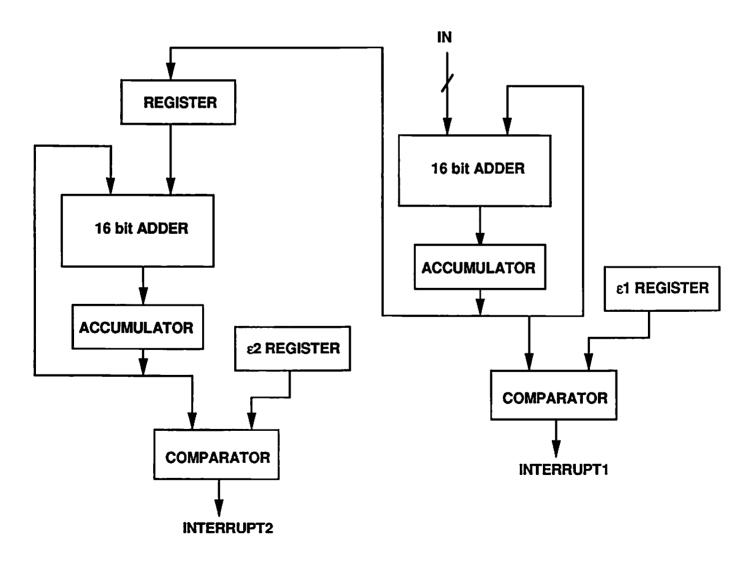

The initial weights have been chosen such that the outputs for all input patterns are the midpoint (0.5) of the expected output (0 or 1). (Fig.5)

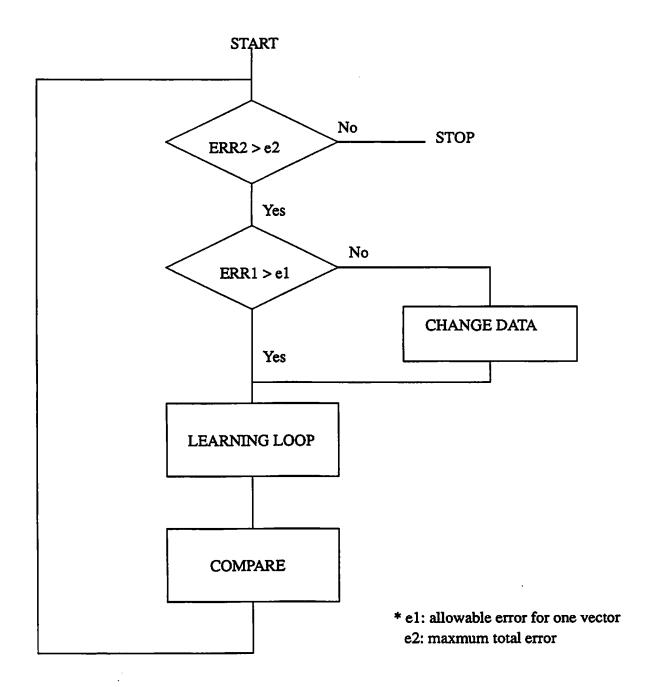

The training sequence: We tried the network for the four patterns, one by one, and then repeated the training, where the initial weights for a new pattern equal the final converged weights for the previous pattern. If the sum of absolute errors for a pattern is less than a threshold( $\varepsilon_1$ ), the training is changed to the next pattern, and if the sum of absolute errors for all the four patterns is less than another threshold ( $\varepsilon_2$ ), all training stopped. The pattern sequence to be trained is; x1,x2,x3,x4,x1, (3) (Fig.6)

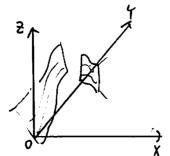

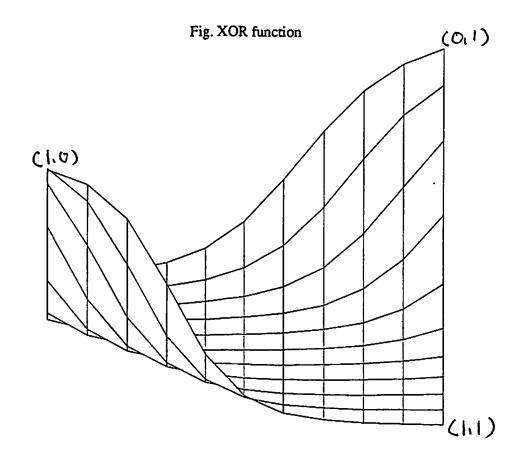

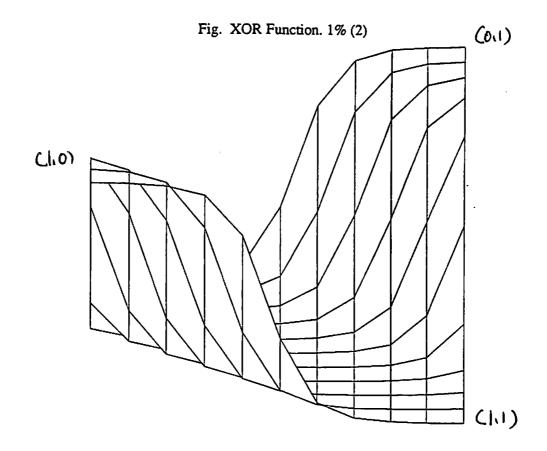

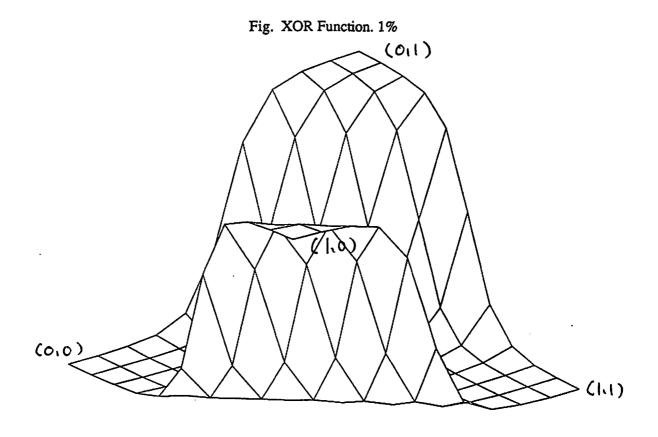

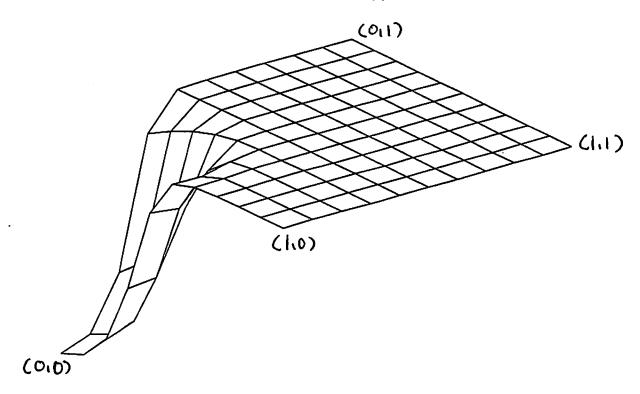

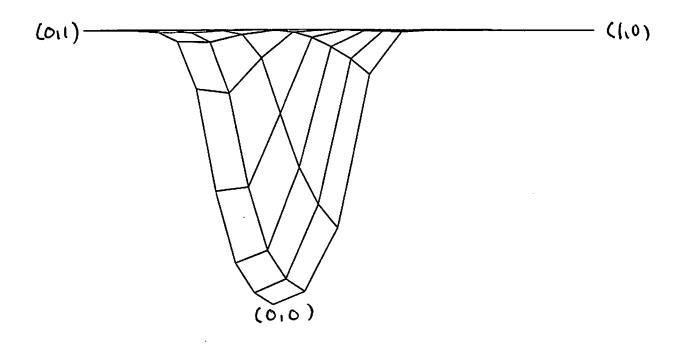

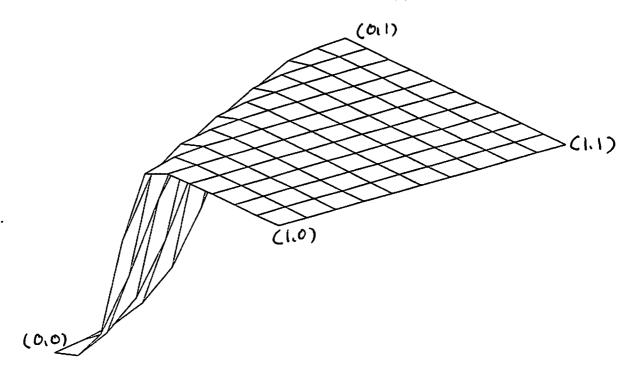

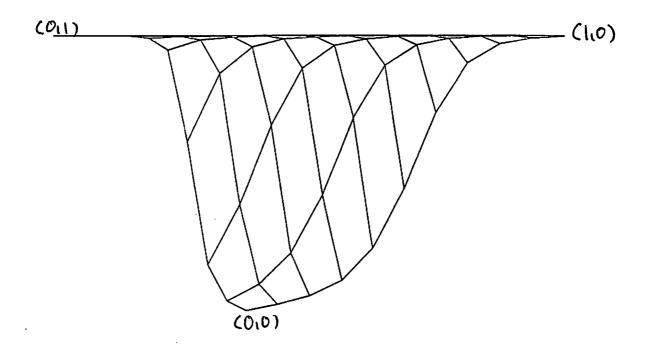

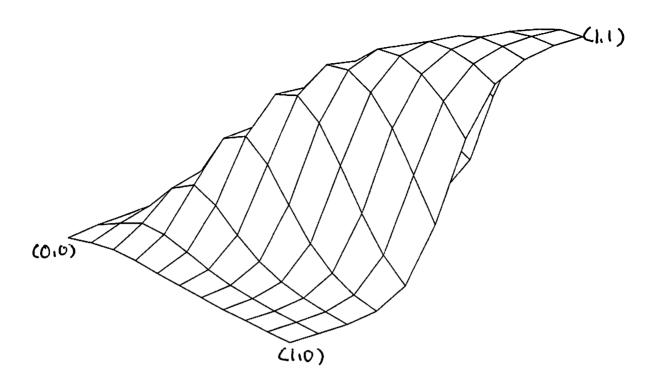

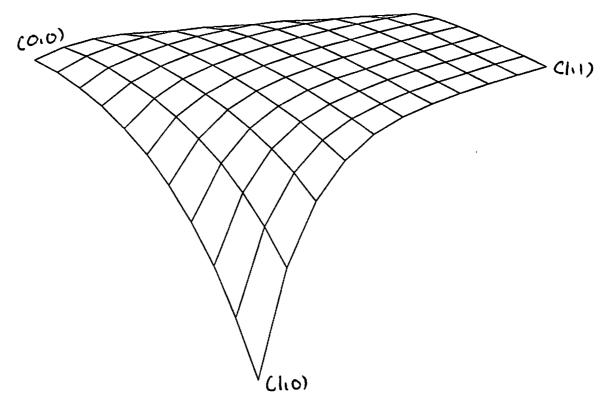

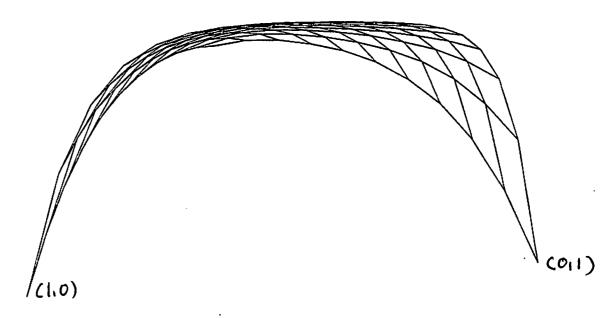

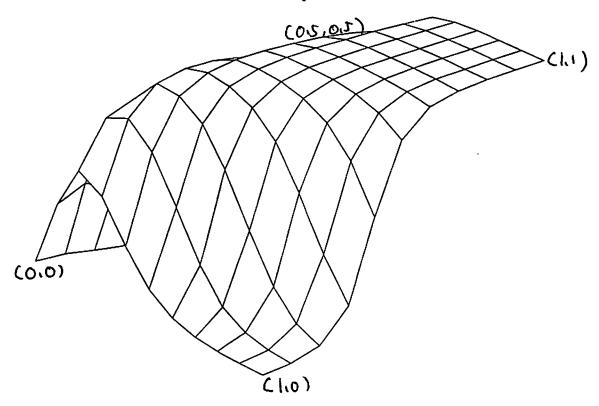

- (1) XOR function: We examined four patter sequence shown in Fig. 7. For all the sequence, the network was trained to perform XOR function, but with different iteration times, where 10% accuracy, i.e.  $_{1}\varepsilon = 0.1, \varepsilon_{2} = 0.4$  (Fig. 8) We can find the pattern sequence (1), (2), in which the patterns of the expected output of 0 are fed into the network before the patterns of expected output 1, can get convergence with smaller iteration times. The simulation with 1% accuracy, i.e.  $\varepsilon_{1} = 0.01, \varepsilon_{2} = 0.04$ , was done. For the both cases, the final weights and outputs are shown in Fig. 9 Using the final weight, the surface of XOR function are constructed for  $(x, y) = (0.1 \times i, 0.1 \times j)$ , where i, j = 0,1,2,...,10. The result graphs are shown in Fig. 10. From the results, we can find the surface for 1% accuracy is more symmetric and smooth than that for 10% accuracy. The Matlab simulation program for XOR function is listed in list. 1

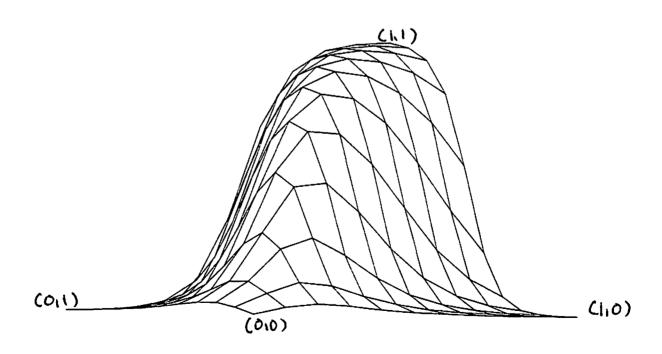

- (2) AND, OR functions: With 10% accuracy, the training for AND, OR functions are done successfully. The results of the final outputs and iteration time are listed in Fig. 11, and the reconstructed surfaces are shown in Fig.12.

### 5. A Consideration for general cases

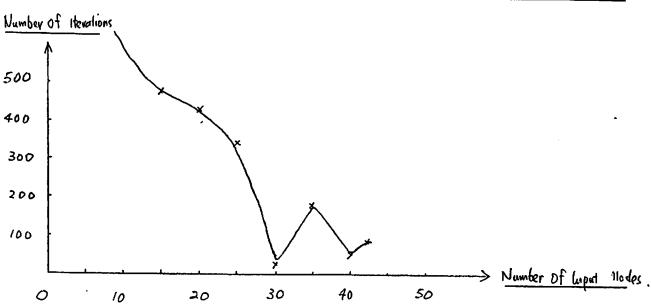

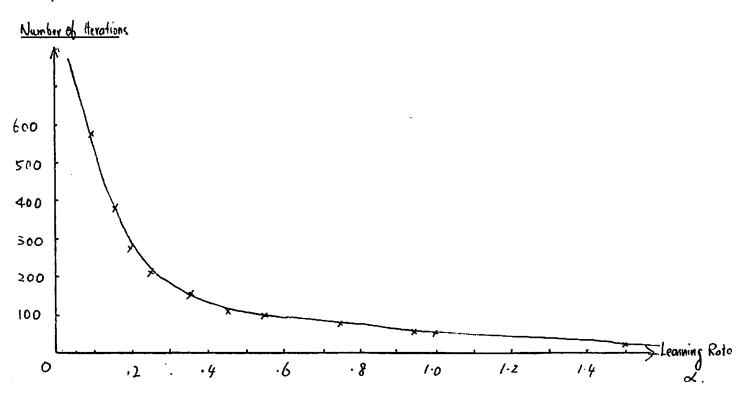

#### (1) The number of the hidden layer neurons:

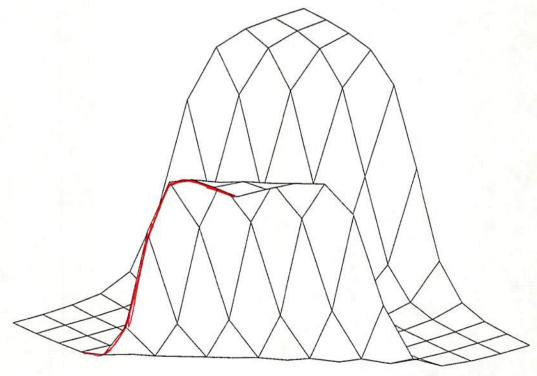

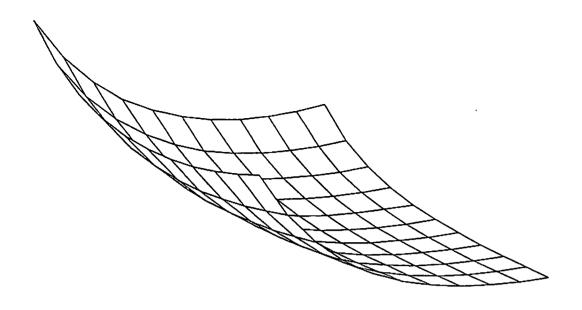

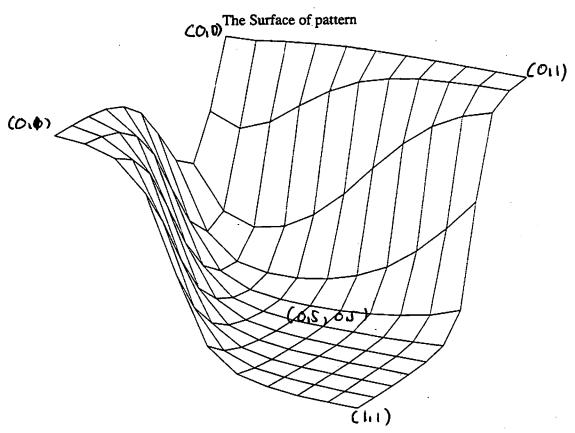

In the result graph of the previous part, we can find that the shape of the transient region from 0 to 1 are kinds of a sigmoid function. (Fig. 13) We named the distorted planes in Fig. 13 as the sigmoid planes, and we made an assumption which define the relationship between the number of hidden layer neurons and sigmoid planes in the reconstructed space. (Appendix 1)

Assumption: The number of sigmoid planes in the reconstructed space is equal or less than the number of the hidden layer neurons. The results of XOR, AND, OR functions follow the above assumption.

### (2) The initial weights

For systems for general cases (ex. ones have three neurons and more, or the inputs and outputs are no longer 0, nor 1.), we used the following initial weights, because the initial weight used for XOR function doesn't make the outputs the mean value of the expected outputs.

- 1) choose the weight such that they are uniformly distributed over (0,1).

- 2) choose the weights randomly.

### (3) The training sequence

Besides the training sequence mentioned in part 4, we also used another sequence. Instead of feeding data sequentially, we choose one pattern randomly and train the network with it once, and then change the input pattern for next training. we choose the patterns randomly every time. the initial weights are the same as the converged weights for the previous pattern. The training continues until a certain iteration time (ex. 3000).(Fig.14)

### (4) The simulation results

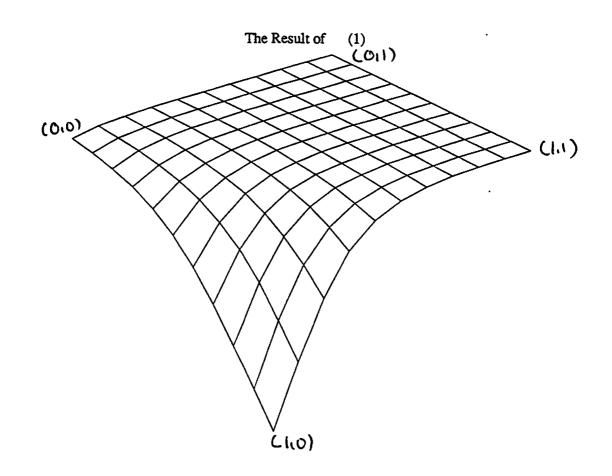

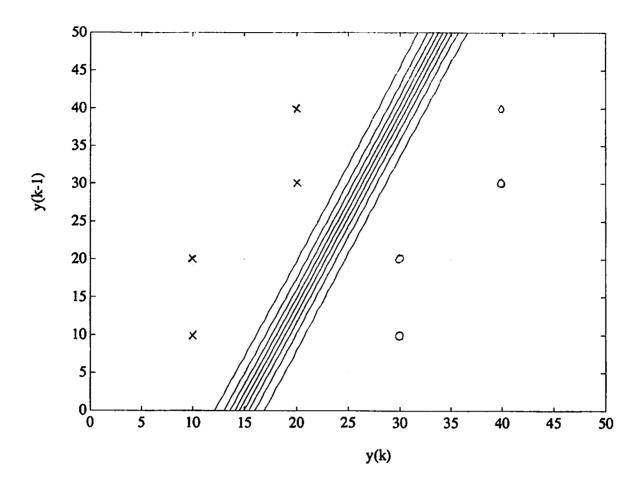

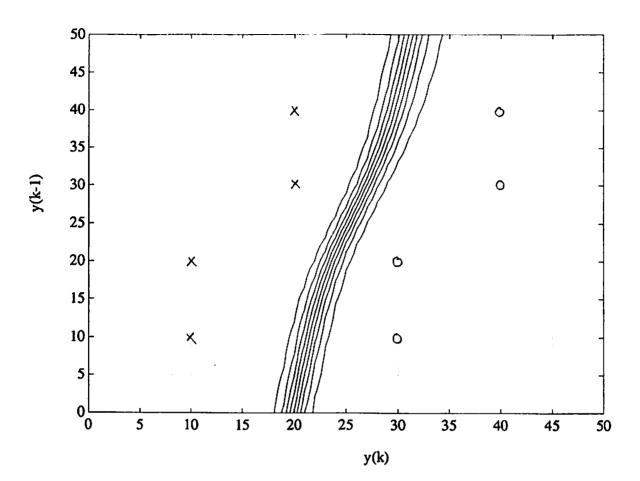

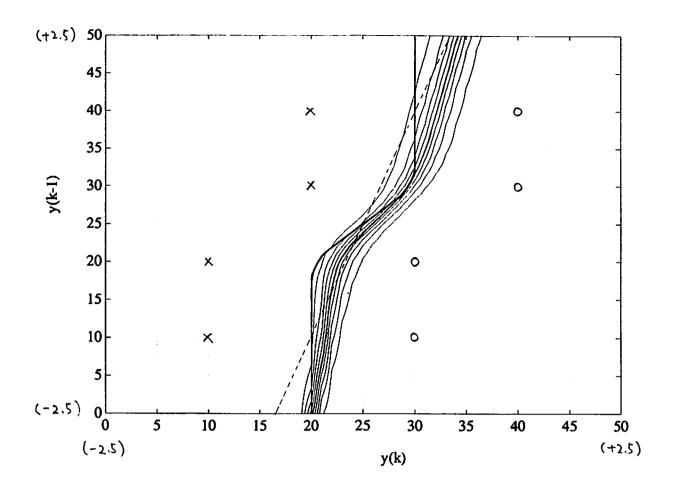

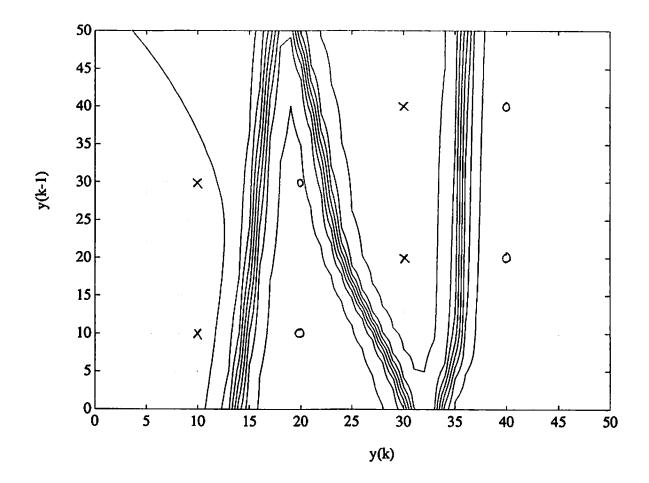

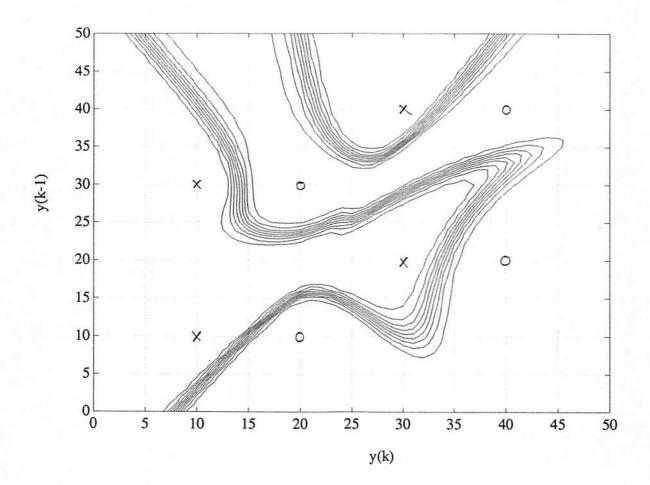

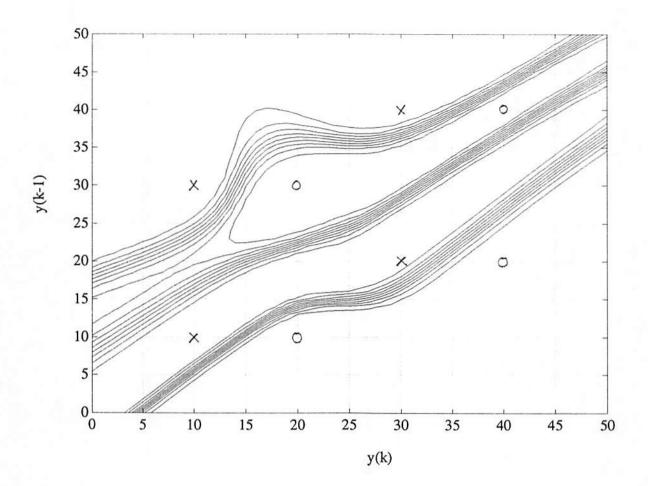

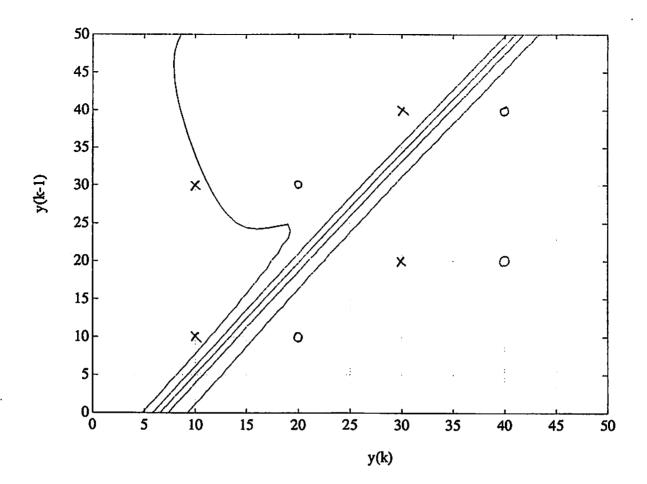

We tried to do simulation for the patterns shown in Fig.15 and 16 For the both case, the number of the hidden layer nodes are four. For Fig.15, we tried the simulations with several conditions. The conditions and results graphs are shown in Fig.17, 18. The results graph for Fig. 16 is shown in Fig. 19. We can't get the convergence for the both cases. It is considered the reason that the initial weights are wrong so that they leads a local minimums. With the correct initial weights for XOR function, we succeeded the simulation for the patterns in Fig.20 and 21, which have small difference from XOR, OR(NOR) functions with two hidden layer nodes. The results are shown in Fig.22 and 23. These results show the difference from these of XOR, OR(NOR) functions. The Matlab program list for Fig. 17 are listed in list. 2.

#### 6. Conclusions

In this project, we have constructed the back-propagation network which perform XOR, AND, OR functions by learning. From the results of these, we suggest the assumption regarding the number of hidden layer neurons, which gives a key to general cases. We also found the successful network can distinguish the difference of the input data.

We can't get the deterministic way to find the initial weights. The assumption is to be proven in mathematics

From the discussion of the sigmoid plane (Appendix 1), we suggest to use the function like the Gaussian function, which has a down slope as well as an up slope, as the transfer function instead of the sigmoid function. (4) Because it is considered to have more possibility that it can fix-dumps and dimple in the surface.

### Reference (1) Suggestion from Mr. . Ph.D student in the Department of Mathmatics, U.S.C

- (2) Robert Hecht-Nielsen. "Neurocomputing", Addison Wesley, pp132-133.

- (3)L. Wang, J.M.Mendal, Structured Trainable Networks For Matrix Algebra, SIPI, U.S.C

- (4) Suggestion from Mr. S. Shimoji. Ph.D student of the Department of Computer Science, U.S.C. (\*) RICOH ltd. Japan, has developed the system to inspect the products of lens using similar neral network.

### Appendix 1

### The sigmoid plane

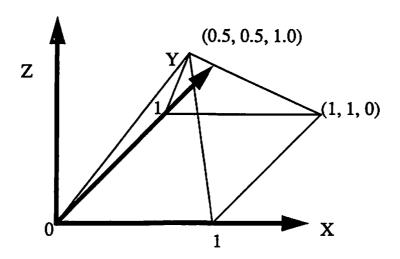

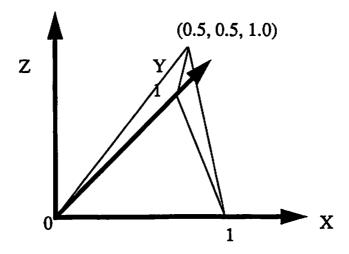

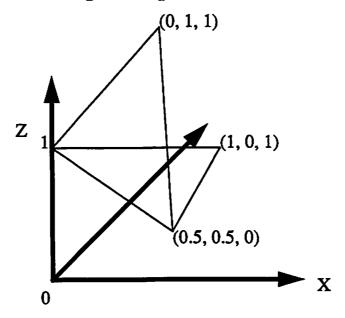

In the back-propagation network, the sum of a hidden layer neuron is given;

$Z = aX + bY + c \tag{1}$

where X, Y are the inputs, a,b,c are the weights for the hidden layer.

Eq. (1) represent a plane in the space (X,Y,Z). The output of the hidden layer, f(\*), can be considered to be a distorted plane by the sigmoid function. In this project, we call one the sigmoid plane. (Fig. A1)

As for the output neuron, the output (surface) is also considered as a sigmoid plane, where the inputs are the sum of the sigmoid plane for the hidden layer.

$W = \alpha Z + \beta V + \gamma$

The surface = f(W)

where Z,V are the output of the hidden layer neurons,  $\alpha$ ,  $\beta$ ,  $\gamma$  are the weight for the output layer.

Now we note that the sigmoid function is monotony increasing function. The surface consists of the factor of Z, and V in the sense of superimpose in a linear system.

Therefore, the surface reconstructed by the system with two hidden layer neuron is considered to have two portions made by sigmoid planes of the hidden layer neurons. And this is able to be expanded for general cases.

Z=axtbyte represents aplane

(I)

31 the input of the output neuron is the super imposed signal of blane

12) fiz)=f(axt bytc) represents

a hyper plan between z=0 tand z=1

"Sigmoid Plane"

Weighted by the weights. The dominant portions appear in the veconstructed surface

-69-

The Back-propagation Network Algorithm

- (1). Learning Rule:

- 1): Output layer:

weighted error

$$\delta_i = (t_i - a_i) f'(CS_i)$$

where  $t_i$  expected output value for neuron j

$a_i$  = actual output value for neuron j

$S_j$  = weighted sum to neuron j

$f(*)$  = neuron transfer function, =  $\frac{1}{1 + \exp(-CS_i)}$ , where c is a coefficient.

2): Hidden layer:

weighted error

$$= \left| \sum_{k} \delta_{k} W_{kj} \right| f'(CS)$$

where  $o_i$  = weighted error from the next layer  $v_k$  = synapse weight connecting neuron j to neuron k in the next layer

For the both layers,

$$W_{ii}^{\text{new}} = W_{ii}^{\text{old}} + \alpha a_i \delta_{ij}$$

where  $0 < 0.25 < \alpha < 0.75 < 1$

Fig.1 The Back-propagation Network Algorithm

Fig.2 The normalization of the input, output & sigmoid function

| X | 0 | 0 | 1 | 1 |

|---|---|---|---|---|

|   | 0 | 1 | 0 | 1 |

| Z | 0 | 1 | 1 | 0 |

Fig. 3 The true table of XOR function

# \* Initial Condition Input Hidden

Fig.4 The Initial Conditions

|--|

Fig. 5 The expected outputs for Fig.5

Fig. 6 The pattern sequence (1). Wang & mendal's method

|   | <b>X</b> 1        | X2  | <b>X</b> 3 | X4 |          | X1 | X2 | <b>X</b> 3 |  |

|---|-------------------|-----|------------|----|----------|----|----|------------|--|

| X | 0                 | 0   | 1          | 1  | X        | 0  | 1  | 0          |  |

| Y | 0                 | 1   | 0          | 1  | Y        | 1  | 0  | 0          |  |

| Е | 0                 | 1   | 1          | 0  | E        | 1  | 1  | 0          |  |

|   | 1) XOR 1 2) XOR 2 |     |            |    |          |    |    |            |  |

|   | X1                | X2  | X3         | X4 |          | X1 | X2 | <b>X</b> 3 |  |

| X | 0                 | 1   | 0          | 1  | X        | 0  | 0  | 1          |  |

| Y | 0                 | 1   | 1          | 0  | Y        | 1  | 0  | 1          |  |

| E | 0                 | 0   | 1          | 1  | Е        | 1  | 0  | 0          |  |

|   | 3)                | XOR | 3          |    | 4) XOR 4 |    |    |            |  |

Fig. 7 The Sequence Pattern for XOR

|       | Iterarion time x1, x2, x3, x4 | The final output results x1, x2, x3, x4 |

|-------|-------------------------------|-----------------------------------------|

| XOR 1 | 7, 4, 6, 3                    | 0.0447, 0.9057, 0.8254, 0.0352          |

| XOR 2 | 1087, 19, 130, 19             | 0.9717, 0.9950, 0.0385, 0.0533          |

| XOR 3 | 8, 6, 11, 4                   | 0.0008, 0.0217, 0.8527, 0.8805          |

| XOR 4 | 639, 366, 49, 86              | 0.9871, 0.0260, 0.0243, 0.9526          |

Fig. 8 The Training Results for Fig. 7

# 1) 10% accuracy

$$H = \begin{bmatrix} 0.5012 - 0.6370 - 0.2920 \\ 0.6586 - 0.6204 & 0.4009 \end{bmatrix}$$

$$O = [0.5637 - 0.6363 \ 0.2899]$$

$$Z = [0.0447 \ 0.9057 \ 0.8254 \ 0.0352]$$

# of iterations = 20

# 2) 1% accuracy

$$H = \begin{bmatrix} 0.7338 - 0.6634 - 0.3945 \\ 0.7489 - 0.8067 & 0.4588 \end{bmatrix}$$

$$O = [0.9916 - 0.9952 \ 0.4954]$$

$$Z = [0.0090 \ 0.9907 \ 0.9900 \ 0.0011$$

# of iterations = 2570

Fig. 9 The training Results for XOR function

Fig. XOR Function (2)

(0.1)

(0.0)

Fig. 10 The Constructed Surface of XOR

-76

(1) 10% Accuracy

Fig. 10 The Constructed Surface of XOR

-77- (2) 1% Accuracy

# (1) OR pattern -(1)

| _ | x1 | x2 | <b>x</b> 3 | x4 |

|---|----|----|------------|----|

| X | 0  | 0  | 1          | 1  |

| Y | 0  | 1  | 0          | 1  |

| E | 0  | 1  | 1          | 1  |

| The final Results | 0.3120, 0,9982, 0.9997, 1.000 |

|-------------------|-------------------------------|

| Iteration time    | 439, 12, 3, 3                 |

# (2) OR pattern -(2)

|   | <b>x</b> 1 | x2 | х3 | x4 |

|---|------------|----|----|----|

| х | 1          | 0  | 1  | 1  |

| Y | 1          | 1  | 0  | 0  |

| Е | 1          | 1  | 1  | 0  |

| The final Results | 0.9992, 0.9999, 0.9955, 0.0605 |

|-------------------|--------------------------------|

| Iteration time    | 15, 7, 55, 1022                |

# (3) AND pattern -(1)

|   | x1 | x2 | х3 | x4 |

|---|----|----|----|----|

| х | 0  | 0  | 1  | 1  |

| Y | 0  | 1  | 0  | 1  |

| Е | 0  | 0  | 0  | 1  |

| The final Results | NO CONVERGENCE |

|-------------------|----------------|

| Iteration time    | NO CONVERGENCE |

# (1) OR pattern -(1)

|   | x1 | x2 | х3 | x4 |

|---|----|----|----|----|

| X | 1  | 0  | 1  | 0  |

| Y | 1  | 1  | 0  | 0  |

| Е | 1  | 0  | 0  | 0  |

| The final Results | 08004, 0.0394, 0.0237, 0.0287 |

|-------------------|-------------------------------|

| Iteration time    | 124, 450, 20, 20              |

Fig. 11 The pattern sequence and the final outputs of OR, AND functions

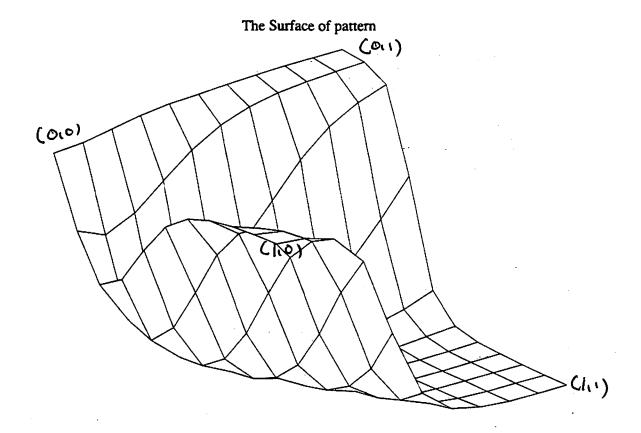

## The Surface of OR (3)

## The Surface of OR Function (4)

Fig. 12 The Constructed Surface of OR. AND function.

(a) OR pattern (1) in Fig. 11

-79-

## The Surface of OR Function (1)

## The Surface of OR Function (2)

Fig. 12 The Constructed Surface of OR, AND Function

(b) OR pattern (2) in Fig. 11

-80-

## The Surface of AND Function

## The Surface of AND Function (2)

Fig. 12 The Constructed Smuther of OR. AND function

(C) AND pattern in Fig. 11

-81-

Fig. XOR Function. 1% (2)

Fig. XOR Function. 1%

The contour can be considered to be sigmoid function

Fig. 13. Sigmoid function in the Reconstructed Surface.

Fig.14 The pattern sequence (2)

Fig. 15 Input Pattern (A)

Fig. 20 Input Pattern (B)

Fig. 21 Input Pattern (C)

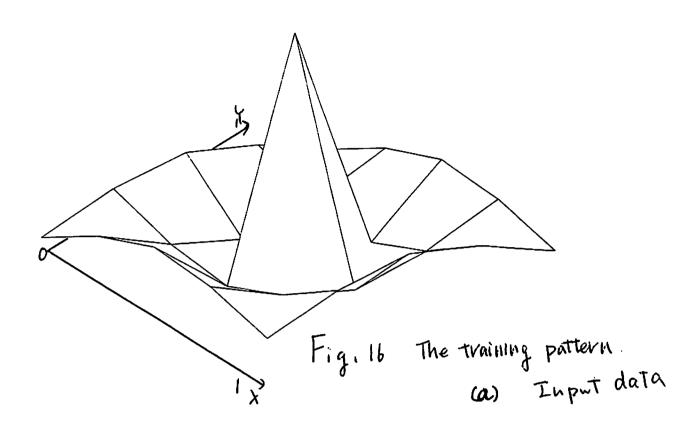

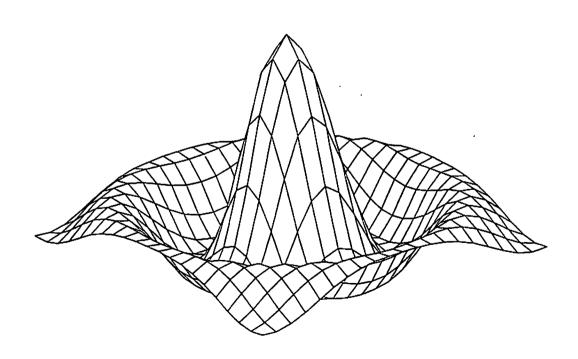

Fig. Z=0.5\*SIN(R)/R+0.3, R= $sqrt(X^2+Y^2)$

(b) Ideal output (Expected Reconstructed Sufface)

|   | Hidden l. The Initial Weights Output l.                 | The Pattern Sequence   | ≯<br>Matlab<br>File<br>Name |

|---|---------------------------------------------------------|------------------------|-----------------------------|

| 1 | H: The Same as those of XOR O: Random                   | Wang & Mendal's method | TT                          |

| 2 | H: The Same as those of XOR O: The Same as those of XOR | Wang & Mendal's method | SS                          |

| 3 | H: The Same as those of XOR O: Random                   | Random                 | Ram2                        |

| 4 | H: Random<br>O: Random                                  | Random                 | Ram3                        |

# vefer to list, 2

Fig. 17 The Conditions for the pattern of Fig. 15

Fig. 18. The Reconstructed Surface W, for the case of W in Fig. 17.

(NOT CONVEYORED)

The Result of (2,2)

Fig. 18. The Reconstructed Surface b), for the case of b1 in Fig. 17 (NOT CONVERGIED) -88-

Fig. 18(c) For the case in fig. 17(c)

(Not Converged)

Fig. 18(d) For the case in fig. 17(d)

(Not converged)

Fig. 19 The Adnal Reconstructed Surface for Fig. 16

The Surface of pattern

Fig. 22 The Reconstructed Syrface for Fig. 20 -90-

Fig. 23. The Reconstructed Surface for Fig. 21.

```

1

```

```

The Network Training for EX-OR function

88

88

88

88

ver. 1.2

The MATLAB program

03/29/91

by Hiro Oakada

The definition of the intial matrices

88

%clear

C = 10

The Input Vector X ( x1', x2', x3')

X = [ 0.5]

The initial weights

The Weight of the Hidden Layer H

& Input data

H = 1 0.5

-0.5

0.0

0.5

H1 = [ 8.0

-3.9

2.9

3.5

0.7

1

7.7

The Weight of the Output layer O

0 = 1 0.5

01 = [-5.5]

0.1

8888888

The Desired Output Vector D

D = [0

1

1

**********

THE INITIAL INTERNAL VALUES

zeros (D)

ERR1 = ones(D)

ones (D)

r = 0.25

888888

ERR2 = 0

for i = 1:ni

ERR2 = ERR2 + abs(D(i) - Z(i))

end

while

ERR2 > 0.1*ni

```

```

for

k = 1:ni

while ERR1(k) > 0.1

pc(k) = pc(k) + 1;

Caliculation of the sum of the hidden layer

S = H * X(:,k);

Caliculation of the output of the hidden layer

The caliculation

y(i) = 1 / (1 + exp(-S(i)*C));

of the hidden

y(1)

y(2)

Layer newon

Caliculation of the sum of the output layer

t = 0 * Y';

Caliculation of the output

z = 1 / (1 + exp(-t*C));

Estimation

For Output Layer

Derr1 = (D(k) - z) * C * exp (-t*C)/(1 + exp(-t*C))^2;

o update the weights

Repacement for the output layer

of the Ridden Cayer

0 = 0 + r * Derr1 * Y;

o The Caliculation of

For Hidden Layer

1:2 the pulp to f out put V,

Derr2(i) = Derr1 * C * O(i) * exp(-C * S(i) )/

for i = 1:2

1 + \exp(-S(i) \cdot C)^2;

oppdate the weights of the output neuron

end

Replacement for the Hidden layer

H - H + r * Derr2' * X(:,k)';

S = H * X(:,k);

Y(i) = 1 / (1 + exp(-S(i)*C));

end

Y(3) = [

1;

% Caliculation of the sum of the output layer

T - Y * O';

% Caliculation of the output

Z = 1 / (1 + exp(-T*C));

```

List, 1 The Matlat Program List

sim1.m

91/04/28 14:55:41

The caliculation

of the timel

weights &

weights. for j = 1:ni for i = 1:2 X(i,j) = 1 / ( 1 + exp( -S(i,j)\*C ) ); Caliculation of the sum of the hidden layer ERR1(k) = abs(D(k) - Z);\$ Caliculation of the output of the hidden layer

\$ \$

\$ Caliculation of the sum of the output layer

\$ if sum(pc) > 2000 break end Y(3,:) =ones(Y(2,:)); end X \* H = S end

$Z(i) = 1 / (1 + \exp(-T(i) *C))$  ERR1(i) = abs(D(i) - Z(i)) ERR2 = ERR2 + ERR1(i)\* Caliculation of the output ERR2 = 0 for i = 1:ni

end

T = Y' \* O';

```

LIST 1.2. The Hatlab Roghams to get the surface

```

```

by Hiro Oakada

for i = 1:nhln YE(i, j) = 1 / (1 + exp(-SE(i, j)*C));

W(i) = 1 / (1 + \exp(-TE(i)*C));

The Neural Network For Surface Reconstruction

for i = 1: ns

V(:,i) = [ W((i-1)*ns+ 1: (i-1)*ns+ ns)']

ver. 1.1

04/22/91

Caliculation of the sum of the hidden layer

SE = H * EX;

* Caliculation of the output of the hidden layer

| *

& Caliculation of the sum of the output layer

for j = 1:ns

for j = 1:ns

EX(:,m) = { XS(i); YS(j) };

YE(nhln+1,:) = ones(YE(1,:));

( Retriveing Phase)

% Caliculation of the output

V = zeros (ns, ns)

if sum(size(H(1,:))) >3

for i = 1:nd

TE = YE' * 0;

G = size(0)

if G(2) > G(1)

0 =0'

for i = 1:nd

for j = 1:nd

SE = H * EX;

s = 0: 1/(ns-1): 1;

XS =s;

YS = s;

for i = 1:ns

nd = ns * ns

end

end

```

est.m

91/04/27

```

tt.m

```

```

The Neural Network For Surface Reconstruction

88

88

88

88

88

ver. 2.1

88

The MATLAB program

88

04/21/91

by Hiro Oakada

88

88

88

The definition of the intial matrices

88

The Input Vector X ( x1', x2', x3')

X(3,:) = ones(X(2,:))

The Weight of the Hidden Layer H

for i = 1: 2: nhln;

= i / (nhln*3);

H(i,1)

uniformly distributed

weights generator

H(i+1,1) = -i/(nhln*3);

H(i,2) = i / (nhln*3 + 1);

H(i+1,2) = -i/(nh1n+3 + 1);

H(i,3) = i/(nh1n+3+2);

H(i+1,3) = -i/(nhln*3 +2);

O(i) = i / nhln*4;

00(i+1) = -i/nhln*4;

H(nhln+1,1) = [0];

H(:,2) = H(:,1);

H(:,3)

= H(:,1);

The Weight of the Output layer O

0 = HH(:,1);

0 = zeros(H(:,1));

00(nhln+1) = 0;

0 = 00'

for i = 1: nhln

H(i,1) = 0.5;

H(i,2) = -0.5;

H(i,3) = 0;

end

8

rand('uniform')

R1 = rand(nhln+1,1);

R2 = rand(nhln+1,1);

0 = R1-R2

The Desired Output Vector D

**********

THE INITIAL INTERAL VALUES

8

pc = zeros(1,ni);

ERR1 = ones(1,ni);

= zeros(1,ni);

```

```

end

r = 0.25;

MAXERR1 = 0.10

MAXERR2 = MAXERR1 * ni

9

888888

ERR2 = 0

for i = 1:ni

ERR2 = ERR2 + abs(D(i) - Z(i));

end

while

ERR2 > MAXERR2

k = 1:ni

for

while ERR1(k) > MAXERR1

pc(k) = pc(k) + 1;

Caliculation of the sum of the hidden layer

S = H * X(:,k);

Caliculation of the output of the hidden layer

for i = 1:nhln

Y(i) = 1 / (1 + \exp(-S(i) \cdot C));

Y(nhln+1) =

Caliculation of the sum of the output layer

t = Y * 0;

Caliculation of the output

z = 1 / (1 + exp(-t*C));

Estimation

For Output Layer

Derr1 = (D(k) - z) * C * exp (-t*C)/(1 + exp(-t*C))^2;

Repacement for the output layer

0 = 0 + r * Derr1 * Y';

%CC

For Hidden Layer

for i = 1:nhln

Derr2(i) = Derr1 * C * O(i) * exp( -C * S(i) )/(

1 + \exp(-S(i)*C))^2;

end

Replacement for the Hidden layer

H = H + r * Derr2' * X(:,k)';

S = H * X(:,k);

```

22

```

for i = 1:nhln

Y(i) = 1 / (1 + exp(-S(i)*C));

end

Y(nhln+1) = [ 1

% Caliculation of the sum of the output layer

T = Y \star O;

% Caliculation of the output

Z = 1 / (1 + \exp(-T^*C));

ERR1(k) = abs(D(k) - Z);

end

end

if sum(pc) > 3000

break

end

Caliculation of the sum of the hidden layer

S = H * X

% Caliculation of the output of the hidden layer

for j = 1:ni

for i = 1:nhln

YY(i,j) = 1 / (1 + exp(-S(i,j)*C));

end

YY(nhln+1,:) = ones(YY(1,:));

% Caliculation of the sum of the output layer

TT = YY' * O;

% Caliculation of the output

ERR2 = 0

for i = 1:ni

ZZ(i) = 1 / (1 + exp(-TT(i)*C));

ERR1(i) = abs(D(i) - ZZ(i));

ERR2 = ERR2 + ERR1(i);

end

Н

1

X

ZZ

pc

end

8

8

Н

0

```

88

88

88

88

88

```

************************

88

The Neural Network For Surface Reconstruction

88

88

ver. 2.1

The MATLAB program

88

04/21/91

by Hiro Oakada

22

The definition of the intial matrices

8

88

The Input Vector X ( x1', x2', x3')

X(3,:) = ones(X(2,:))

The Weight of the Hidden Layer H

for i = 1: 2: nhln;

= i / (nhln*3);

H(i,1)

H(i+1,1) = -i/(nhln*3);

H(i,2) = i / (nhln*3 + 1);

H(i+1,2) = -i/(nhln*3 + 1);

H(i,3) = i/(nhln*3 +2);

H(i+1,3) = -i/(nh1n*3 +2);

O(i) = i / nhln*4;

00(i+1) = -i/nhln*4;

%end

H(nhln+1,1) = [0];

H(:,2) = H(:,1);

H(:,3) = H(:,1);

% The Weight of the Output layer O

0 = HH(:,1);

0 = zeros(H(:,1));

00(nhln+1) = 0;

0 - 00'

for i = 1: nhln

H(i,1) = 0.5;

H(i,2) = -0.5;

H(i,3) = 0;

end

0 = H(1,:)'

0(4) = 0

% The Desired Output Vector D

********

THE INITIAL INTERAL VALUES

8

8

pc = zeros(1,ni);

ERR1 = ones(1,ni);

Z = zeros(1,ni);

end

r = 0.25;

MAXERR1 = 0.10

```

MAXERR2 = MAXERR1 \* ni

```

8

888888

ERR2 = 0

for i = 1:ni

ERR2 = ERR2 + abs(D(i) - Z(i));

end

while

ERR2 > MAXERR2

k = 1:ni

for

while ERR1(k) > MAXERR1

8

pc(k) = pc(k) + 1;

Caliculation of the sum of the hidden layer

S = H * X(:,k);

Caliculation of the output of the hidden layer

for i = 1:nhln

Y(i) = 1 / (1 + exp(-S(i)*C));

Y(nh1n+1) =

1

1:

Caliculation of the sum of the output layer

t = Y * 0;

Caliculation of the output

z = 1 / (1 + \exp(-t*C));

Estimation

For Output Layer

Derr1 = (D(k) - z) * C * exp (-t*C)/(1 + exp(-t*C))^2;

Repacement for the output layer

0 = 0 + r * Derr1 * Y';

%CC

For Hidden Layer

for i = 1:nhln

Derr2(i) = Derr1 * C * O(i) * exp(-C * S(i))/(

1 + \exp(-S(i) \cdot C))^2;

end

Replacement for the Hidden laver

H = H + r * Derr2' * X(:,k)';

S = H * X(:,k);

for i = 1:nhln

Y(i) = 1 / (1 + exp(-S(i)*C));

end

```

$Y(nhln+1) = \{ 1$

91/04/27

Z = 1 / (1 + exp(-T\*C));ERR1(k) = abs(D(k) - Z);& Caliculation of the sum of the output layer T = X \* 0; & Caliculation of the output end

if sum(pc) > 3000 break end

end

Caliculation of the sum of the hidden layer

S = H \* X

& Caliculation of the output of the hidden layer

for j = 1:ni

for i = 1:nhln

YY(i,j) = 1 / (1 + exp( -S(i,j)\*C ) );

end YY(nhln+1,:) = ones( YY(1,:) );

& Caliculation of the sum of the output layer

TT = YY' \* 0;

ZZ(1) = 1 / (1 + exp(-TT(1)\*C)); ERR1(1) = abs(D(1) - ZZ(1)); ERR2 = ERR2 + ERR1(1);& Caliculation of the output ERR2 = 0 for i = 1:ni

end

X 22 Pc end

```

88

The Neural Network For Surface Reconstruction

88

88

88

88

88

The MATLAB program

ver. 3.1

by Hiro Oakada

88

04/21/91

88

22

88

The definition of the intial matrices

nhln =3

88

The Input Vector X ( x1', x2', x3')

X(3,:) = ones(X(2,:))

The Initial Weight of the Hidden Layer H

rand('uniform')

R1 = rand(nhln, 2);

· Random Weizher

generator

R2 = rand(nhln, 2);

H = R1 - R2

for i =1: nhln

H(i,1) = 0.5;

H(i,2) = 0.5;

end

H(:,3) = zeros(H(:,1))

The Initial Weight of the Output layer O

R3 = rand(1, nhln +1);

R4 = rand(1, nhln +1);

0 = R3 - R4

88

THE INITIAL INTERNAL VALUES

for

i = 1:ni

pc(i) =

1;

1:

Z(i) =

end

r = 0.25;

888888

while

sum(pc) < 100000

o Pickup a pattern randomly.

R5 = rand * 10000;

R6 = fix(R5);

R7 = fix(R6/ni);

k = R6 - R7*ni +1;

pc(k) = pc(k) + 1;

Caliculation of the sum of the hidden layer

S = H * X(:,k);

```

```

Caliculation of the output of the hidden layer

for i = 1:nhln

Y(i) = 1 / (1 + \exp(-S(i) *C));

Y(nhln+1) =

[ 1

1:

Caliculation of the sum of the output layer

t = Y * 0';

*

Caliculation of the output

z = 1 / (1 + exp(-t*C));

Estimation

For Output Layer

Derrl = (D(k) - z) * C * exp (-t*C)/(1 + exp(-t*C))^2;

Repacement for the output layer

0 = 0 + r * Derr1 * Y;

&CC

For Hidden Layer

8

for i = 1:nhln

Derr2(i) = Derr1 * C * O(i) * exp(-C * S(i))/(

1 + \exp(-S(i)*C))^2;

end

Replacement for the Hidden layer

H = H + r * Derr2' * X(:,k)';

S = H * X(:,k);

for i = 1:nhln

Y(i) = 1 / (1 + \exp(-S(i) \cdot C));

Y(nhln+1) = [ 1

1;

% Caliculation of the sum of the output layer

T = Y * O';

% Caliculation of the output

Z = 1 / (1 + exp(-T*C));

ERR1(k) = abs(D(k) - Z);

end

Caliculation of the sum of the hidden layer

S = H * X

```

```

O.

```

ram2.m

91/04/27

end

-100-

ram3.m

```

* * * *

by Hiro Oakada

Y(i) = 1 / (1 + exp(-S(i)*C));

The Neural Network For Surface Reconstruction

Caliculation of the output of the hidden layer

ver. 3.1

04/21/91

pc(k) = pc(k) + 1j

Caliculation of the sum of the hidden layer

H

Initial Weight of the Hidden Layer

==

Initial Weight of the Output layer

S = H * X(:,k);

The definition of the intial matrices

for i = 1:nhln

The Input Vector X ( x1', x2', x3')

Y(nhln+1) =

00

H(:,3) = zeros(H(:,1))

= rand(1, nhln +1);

= R3 -R4

= rand(1, nhln +1);

The MATLAB program

X(3,:) = ones(X(2,:))

& THE INITIAL INTERNAL VALUES

R5 = rand * 10000;

R6 = fix(R5);

R7 = fix(R6/ni);

k = R6 - R7*ni +1;

= rand(nhln,2);

= rand(nhln,2);

rand('uniform')

sum(pc) < 1000

r = 0.25;

i = 1:ni

pc(1)

2(1)

R3

0

8888888

The

The

while

end

```

-101-

```

Derr1 = ( D(k) - z ) * C * exp ( -t* C )/( 1 + exp( -t*C ) )^2;

Derr2(i) = Derr1 * C * O(i) * \exp(-C * S(i)) / (

Y(i) = 1 / (1 + exp(-S(i)*C));

YY(i,j) = 1 / (1 + exp(-S(i,j)*C));

H = H + r * Derr2' * X(:,k)';

Z = 1 / (1 + exp(-T*C));

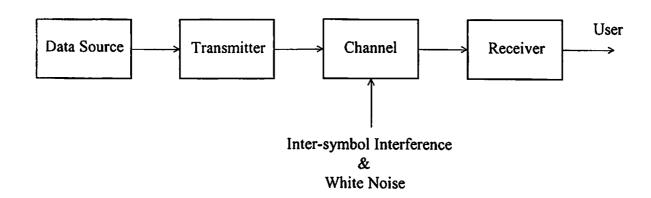

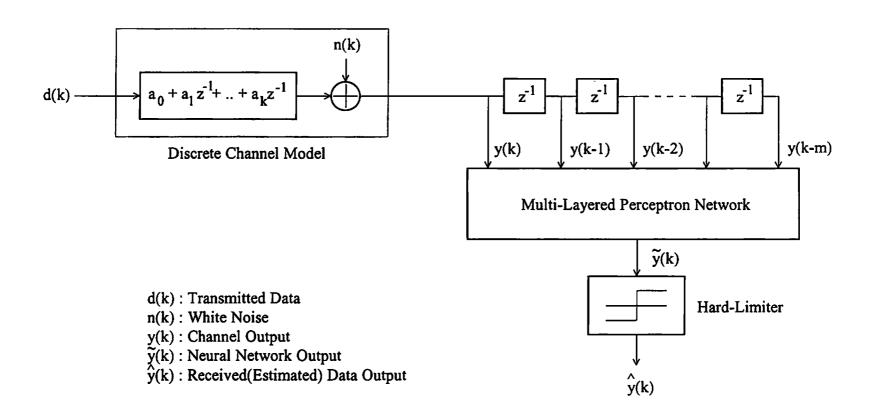

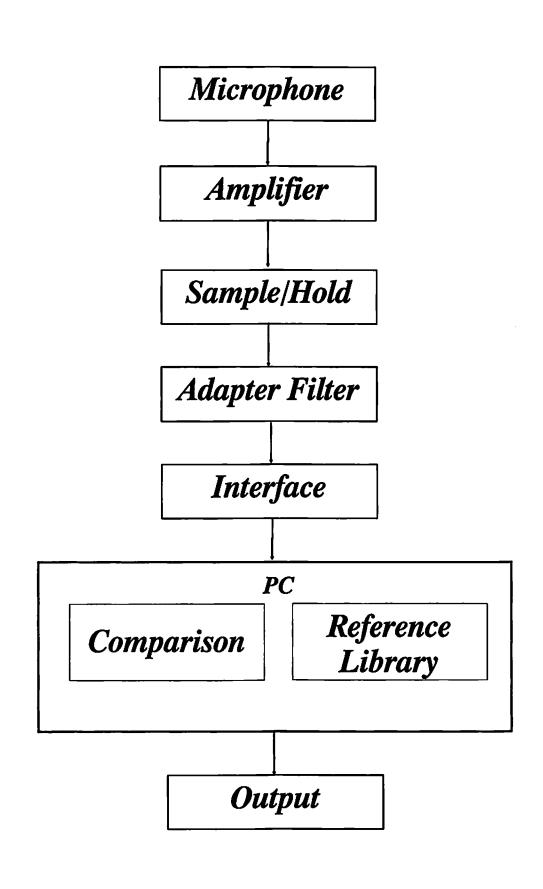

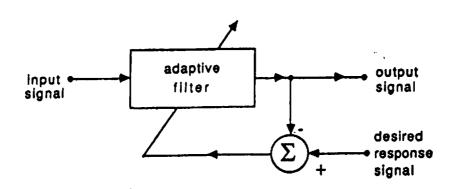

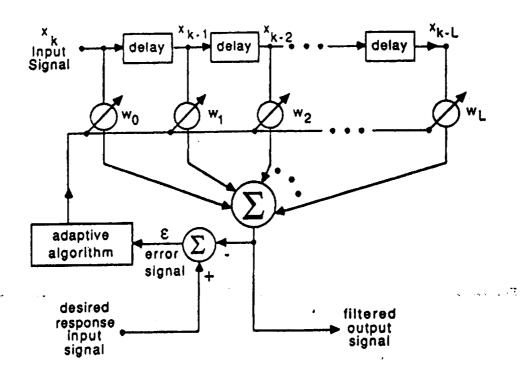

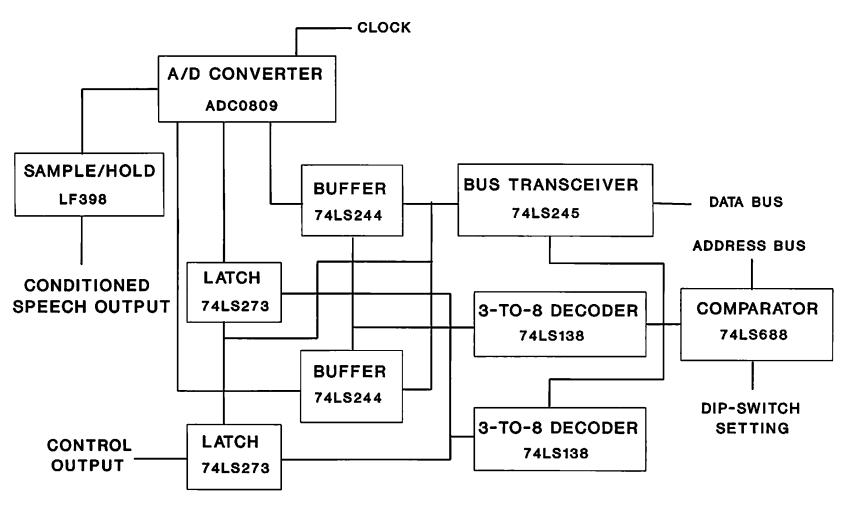

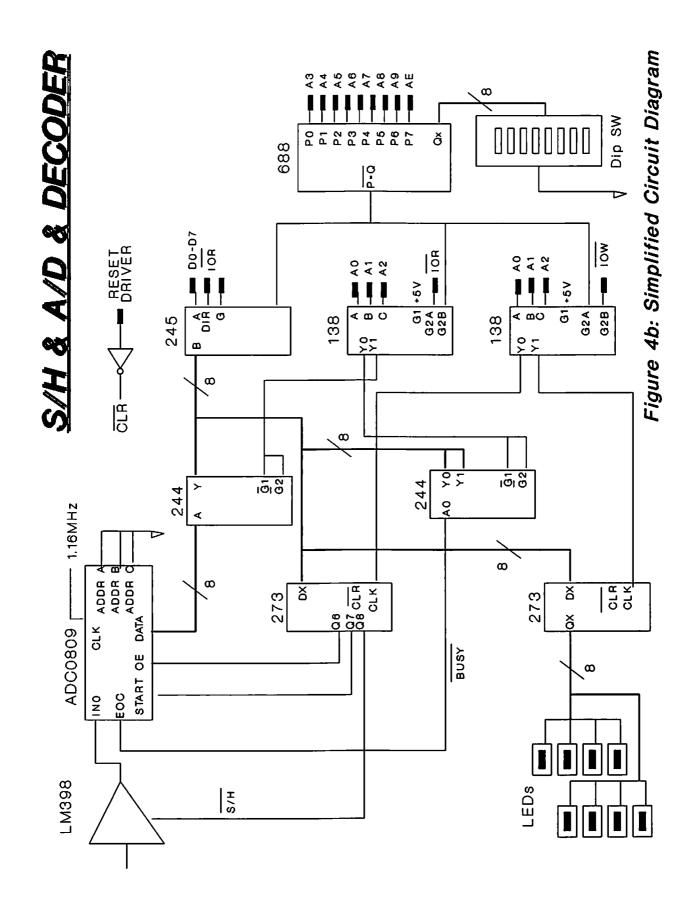

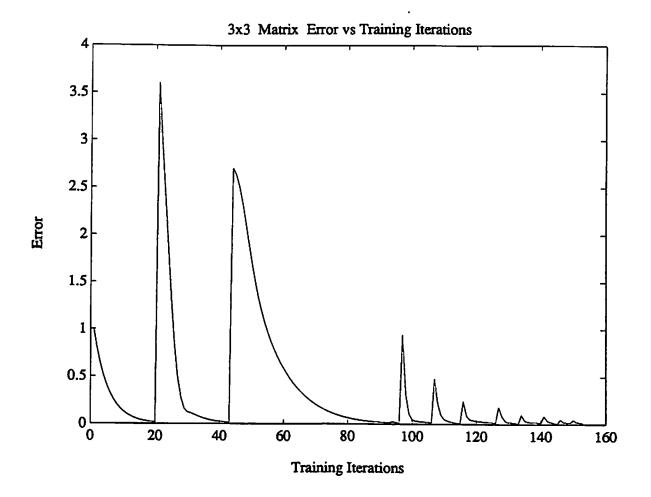

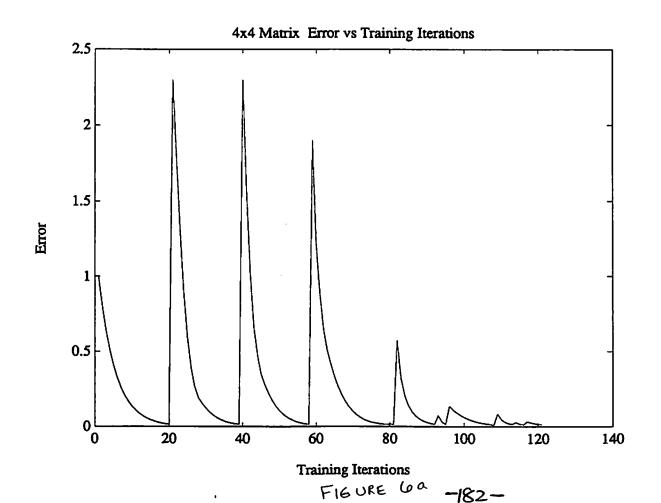

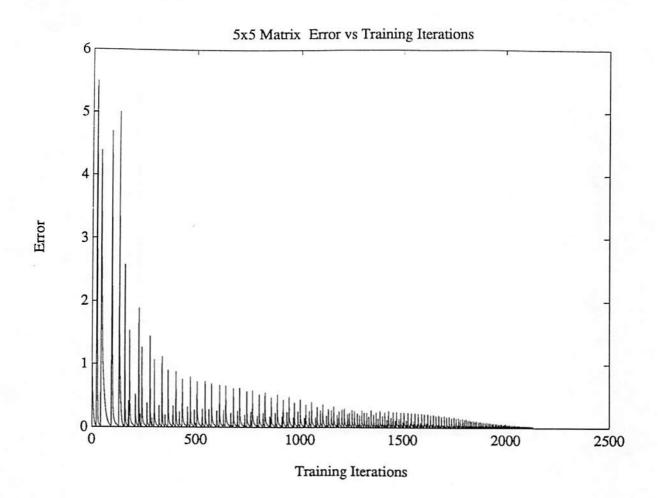

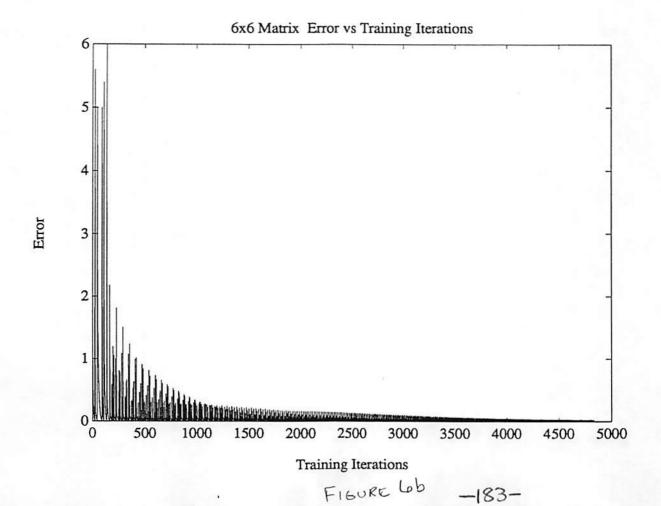

z = 1 / (1 + exp(-t*C));