#### **USC-SIPI REPORT #284**

Design For a Shared Memory Computer With a Combining Optical Interconnection Network Using External Routing

by

**Clare Waterson**

May 1995

Signal and Image Processing Institute UNIVERSITY OF SOUTHERN CALIFORNIA

Department of Electrical Engineering-Systems 3740 McClintock Avenue, Room 404 Los Angeles, CA 90089-2564 U.S.A.

# Acknowledgements

Dr. B. Keith Jenkins -(Advisor) for technical advice and guidance throughout the long process of research and writing that led to this dissertation

Air Force Office of Scientific Research and National Science Foundation — for support of my Ph.D. research

The Aerospace Corporation — for support of education and research

Bob Bolender — for extensive assistance, support, time, and encouragement; and for nice computer equip-

Michael Elkins —

for encouragement, motivation, patience,

time, and computer assistance

Adam Goldstein —

(my "Progress Advisor") for interaction is a good thing (hey, but extremes are bad), and for timely (and favorable) paper reviews

Adam Goldstein, Ching-Chu Huang,

Kuang-Yu Li, Sabino Piazzolla - for mutual support

Kuang-Yu Li — for timely suggestions

Bill Woody - for technical advice and suggestions

Brian Primeau — for gentle humor

Ed Meinel — for support and patience

Russell Kurtz — for empathizing

Ken Chan — for encouragement Jill Waterson — for keeping me sane?

Mucha, Tigger & Hobbes,

Tsunami & Typhoon, Amber & Mello — for inspiration  $(\mu!)$

John & John (They Might Be Giants) — for I will never say the word "procrastinate" again...

Johnette Napolitano (Concrete Blonde) — for Who did you think I would be? Hah! Well you got me instead!

Brian Dewan — for Feel the brain... slippery and smooth

Douglas Adams — for You've got to build bypasses

Bach and KROQ - for the perfect music by which to write luculent lucubrations full of sesquipedalian terminology.

Douglas Hofstadter — Hofstadter's Law: It always takes longer than you expect, even when you take Hofstadter's Law into account.

## Abstract

The design of a fine-grained MIMD computer architecture, the Shared Memory Optical/Electronic Computer (SMOEC), is presented. The SMOEC architecture consists of electronic processing elements and memory modules interconnected with a novel combining passive optical interconnection network which is controlled by a separate electronic routing processor. The hybrid system design emphasizes the strengths of the two technologies, using optics for communication and electronics for processing. Sample system implementation recipes exemplify the flexibility, realizability, and scalability of the SMOEC system architecture. The system-level focus on interrelated development of three main design facets—architecture, hardware, and control algorithms—has been crucial in designing a well-balanced high performance system.

The design of the optical interconnection network, the Free-space Interconnection with Externally-controlled Routing (FIER), is presented in detail. The network is implemented using exclusively passive optical elements, and it employs a shuffle-exchange topology. Each shuffle-exchange stage is optically cascadable. The FIER switch nodes are capable of broadcast and combine operations in additional to bypass and exchange. The FIER is designed to be circuit-switched by an external electronic routing processor. Although the FIER is designed to be used as a subsystem within the SMOEC, it may be used as a subsystem in other communication or computing architectures.

A review of Extended Generalized Shuffle (EGS) network theory is provided to give a solid theoretical background for the interconnection topology employed in the FIER and to prepare for presentation of a new routing algorithm.

A new algorithm, the Flexible Localized Algorithm for EGS-network Management (FLAEM), is presented. This algorithm was developed for circuit-switched combining regular simplified EGS networks (such as the FIER optical network); it parallelizes the routing process in a different way than the previously available method. The effectiveness of the FLAEM is illustrated by simulation results, which show that the algorithm time complexity is logarithmic in system size (N). The FLAEM extends the repertoire of routing techniques available for this class of EGS networks.

# Contents

| Ac  | knov  | vledgeme   | $_{ m nts}$    |        |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      | i    |

|-----|-------|------------|----------------|--------|--------------|-------|-------|------|----------------|-------|---|------------|---|----|---|---|----|---|---|-----|-------|---|------|------|

| Αŀ  | ostra | ct         |                |        |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      | iii  |

| Lis | st of | Figures    |                |        |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      | vii  |

| Lis | st of | Tables     |                |        |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      | х    |

| Lis | st of | Acronym    | s              |        |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      | xi   |

| Lis | st of | Notation   |                |        |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   | 97   | xiii |

| 1   | INT   | RODUC      | ΓΙΟΝ           |        |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      | 1    |

|     | 1.1   | Backgroun  | nd .           |        |              |       | 2 12  |      |                |       |   |            |   | 10 |   |   |    | 1 | 2 | 2 1 |       |   | 7888 | 3    |

|     | 1.2   | Motivation |                |        |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      | 6    |

|     | 1.3   | Design Ph  |                |        |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      |      |

| 2   | SYS   | TEM AR     | CHI            | rec'   | ГUF          | RE    |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      | 12   |

|     | 2.1   | SMOEC A    | Archite        | ecture | e Ove        | ervi  | ew    |      |                |       |   |            |   |    |   |   |    | : |   |     |       |   |      | 12   |

|     | 2.2   | Processing |                |        |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      |      |

|     | 2.3   | Memory N   |                |        | A CONTRACTOR |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      |      |

|     | 2.4   | Optical In |                |        |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      |      |

|     | 2.5   | Electronic |                |        |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      | 22   |

|     | 2.6   | Control Si |                | 0      |              |       |       | 200  |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      |      |

|     | 2.0   | Control    | gnari          | 715011 | Julic        | л     | , 111 | UCI. | iac            | ~ ( · |   | <i>D</i> 1 | , | •  |   | ٠ | ٠  | 0 | • | •   | •     | • | •    |      |

| 3   | INT   | ERCON      | VECT           | ION    | NE           | ETV   | vo    | RF   | ( )            | O     | P | ΟL         | O | G  | Y | A | N. | D |   |     |       |   |      |      |

|     | ROI   | JTING (1   | REVI           | EW)    | )            |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      | 25   |

|     | 3.1   | Shuffle-Ex |                |        |              | gy .  |       |      | 30 <b>.</b> 00 |       |   |            |   |    |   |   |    |   |   |     | ::•:: |   | •    | 27   |

|     |       |            | e Perf         |        |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      |      |

|     |       |            | Shuffle        |        |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      |      |

|     |       |            | .2.1           | b-Sh   |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      | 31   |

|     |       |            | .2.2           | Q-Sl   |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      | 31   |

|     |       |            | .2.3           | Q-Sl   |              |       |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      | 34   |

|     |       | 31.2       | ) 1000 E-500 E | U      |              | 33334 |       |      |                |       |   |            |   |    |   |   |    |   |   |     |       |   |      |      |

iv

|   |     | 3.1.3 Bypass/Exchange Switch                                  |

|---|-----|---------------------------------------------------------------|

|   | 3.2 | Shuffle-Exchange Networks                                     |

|   |     | 3.2.1 Ω Networks                                              |

|   |     | 3.2.2 Delta Networks                                          |

|   |     | 3.2.3 Nonblocking Shuffle-Exchange Networks 40                |

|   | 3.3 | Extended Generalized Shuffle Network Topology 41              |

|   |     | 3.3.1 EGS Definition                                          |

|   |     | 3.3.2 Regular Simplified EGS (RS-EGS) Definition 43           |

|   |     | 3.3.3 RS-EGS Theory                                           |

|   |     | 3.3.4 RS-EGS Design Parameter Analysis 47                     |

|   | 3.4 | Restricted-F RS-EGS Network Routing                           |

|   | 3.5 | Summary and Contributions                                     |

| 4 | OP  | FICAL INTERCONNECTION NETWORK HARDWARE 61                     |

|   | 4.1 | Passive Hardware Implications                                 |

|   | 4.2 | Optical Shuffle-Exchange Hardware Design 63                   |

|   |     | 4.2.1 FIER Input/Output                                       |

|   |     | 4.2.2 The LA⇔CP Format Converter 64                           |

|   |     | 4.2.3 Pixel Spacing Adjuster                                  |

|   |     | 4.2.4 The CP Unshuffle                                        |

|   |     | 4.2.5 The CP Exchange                                         |

|   |     | 4.2.6 Broadcasting and Combining using TSLMs 76               |

|   | 4.3 | Optical EGS Hardware Design                                   |

|   |     | 4.3.1 EGS "Fan-out" (demultiplexer) 87                        |

|   |     | 4.3.2 EGS $F$ -shuffle                                        |

|   |     | 4.3.3 EGS Fan-in                                              |

|   | 4.4 | Optical Implementation Issues                                 |

|   | 4.5 | Comparison                                                    |

|   | 4.6 | Summary                                                       |

| 5 | NE  | TWORK ROUTING ALGORITHM 101                                   |

|   | 5.1 | Interrelation of the MATSH Control Unit and Routing Algorithm |

|   |     | Design                                                        |

|   | 5.2 | The FLAEM Routing Algorithm                                   |

|   |     | 5.2.1 Motivation                                              |

|   |     | 5.2.2 Exposition                                              |

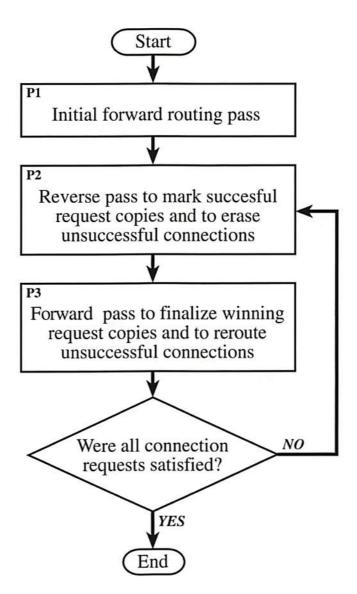

|   |     | 5.2.2.1 Initial Forward Routing Pass (P1) 110                 |

|   |     | 5.2.2.2 Reverse Marking/Erasing Pass (P2) 113                 |

|   |     | 5.2.2.3 Forward Finalizing/Rerouting Pass (P3) 113            |

|   |     | 5.2.2.4 The Enhanced-FLAEM Procedure 114                      |

|   |     | 5.2.3 Illustrative Example                                    |

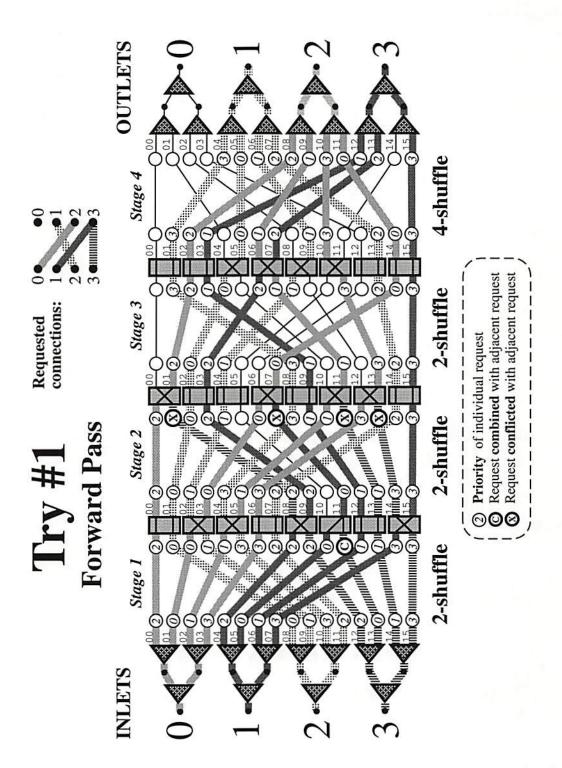

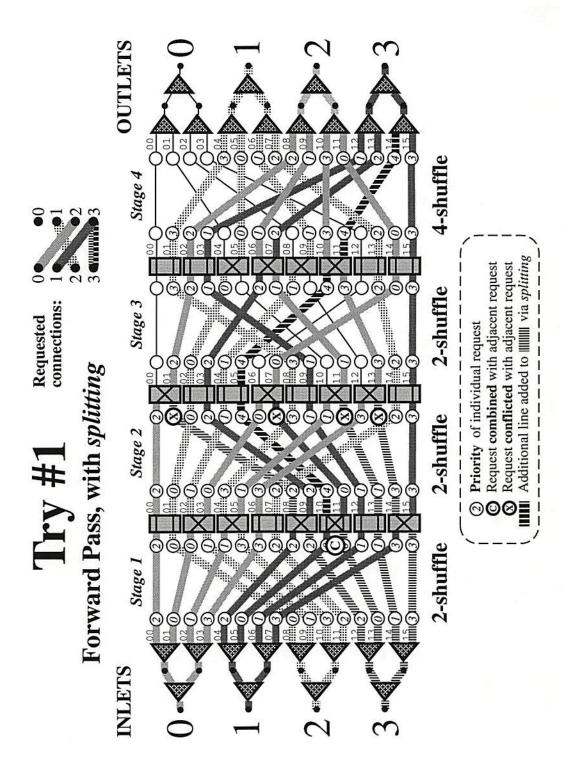

|   |     | 5.2.3.1 Try #1: Forward Pass (P1)                             |

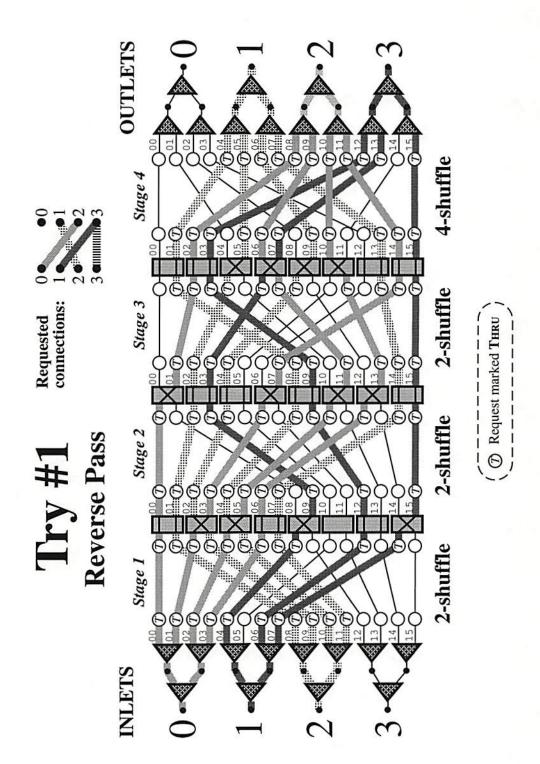

|   |              |                    | 5.2.3.2     | Try #1: Reverse Pass (P2) 121                 |

|---|--------------|--------------------|-------------|-----------------------------------------------|

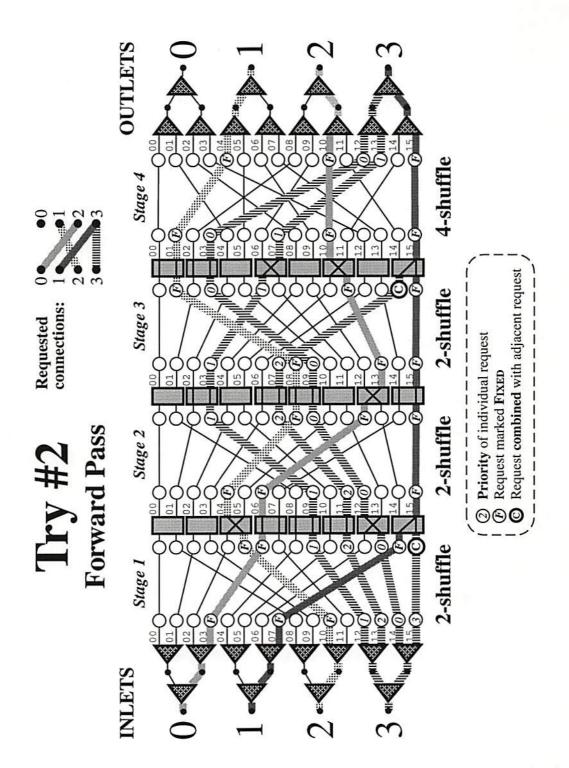

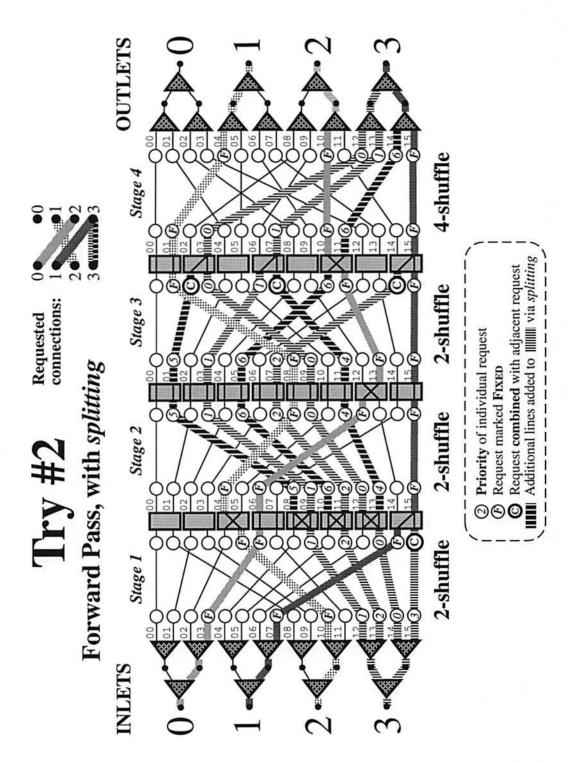

|   |              |                    | 5.2.3.3     | Try #2: Forward Pass (P3)                     |

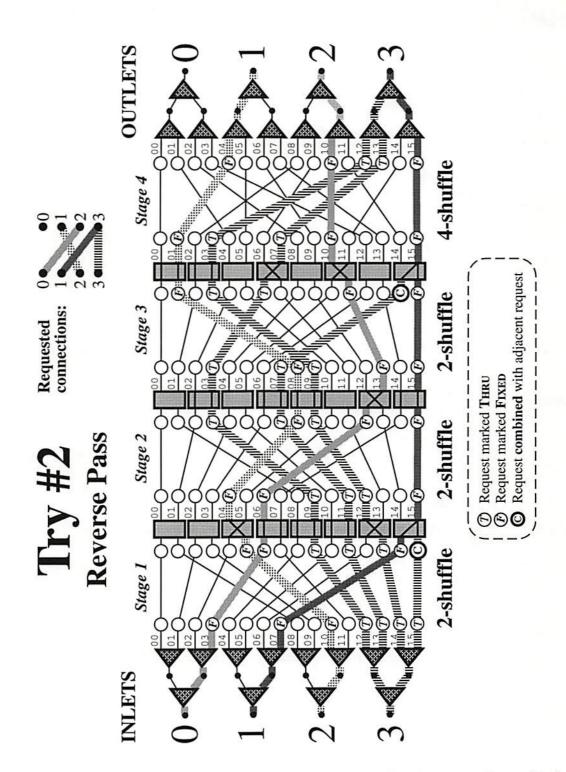

|   |              |                    | 5.2.3.4     | Try #2: Reverse Pass (P2)                     |

|   |              |                    | 5.2.3.5     | Final Forward Pass (P3)                       |

|   |              |                    | 5.2.3.6     | Enhanced-FLAEM procedure illustrations 129    |

|   | 5.3          | The F              | LAEM Si     | mulation                                      |

|   |              | 5.3.1              | Sim-FLA     | AEM Program Development                       |

|   |              |                    | 5.3.1.1     | The First Routing Program                     |

|   |              |                    | 5.3.1.2     | The Second Routing Program                    |

|   |              |                    | 5.3.1.3     | The Third Routing Program                     |

|   |              |                    | 5.3.1.4     | The Fourth Routing Program: Basic-FLAEM 134   |

|   |              |                    | 5.3.1.5     | The Fifth Routing Program: Enhanced-FLAEM 135 |

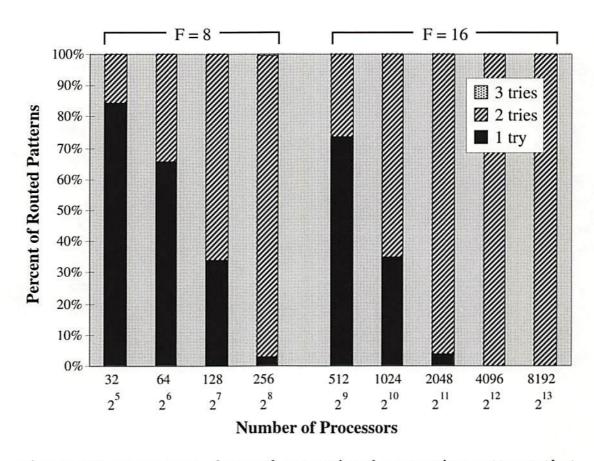

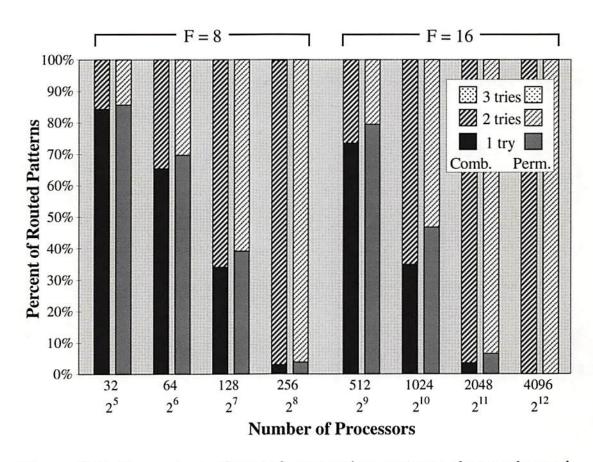

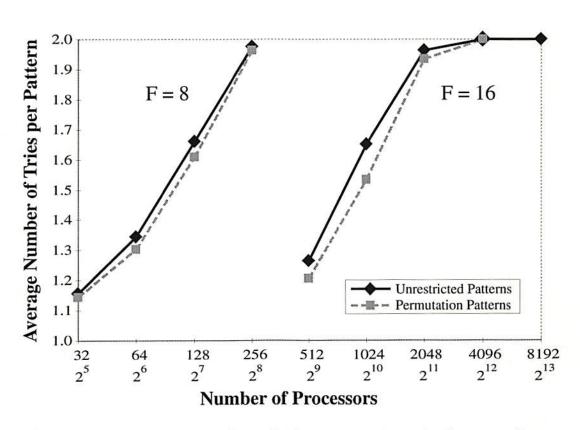

|   |              | 5.3.2              | Simulati    | on Results                                    |

|   |              |                    | 5.3.2.1     | Analysis of Simulation Data                   |

|   |              |                    | 5.3.2.2     | Conclusions From Simulation Data 142          |

|   | 5.4          | Summ               | ary         |                                               |

| 0 | GO.          |                    | NII CIA MIL | ON ALGORITHMS 146                             |

| 6 |              |                    |             |                                               |

|   | $6.1 \\ 6.2$ |                    |             | rithm                                         |

|   | 0.2          | 6.2.1              | _           | ite Technique Candidates                      |

|   |              | 0.2.1              | 6.2.1.1     | W1: Permutations Only                         |

|   |              |                    | 6.2.1.1     | W2: Arbitrate Write Requests                  |

|   |              |                    | 6.2.1.2     | W3: Combine Write Requests in FIER            |

|   |              |                    | 6.2.1.4     | W4: Combine Write Requests in MATSH 149       |

|   |              |                    | 6.2.1.4     | Write Algorithm Technique Conclusions 150     |

|   |              | 6.2.2              |             | alization Principle                           |

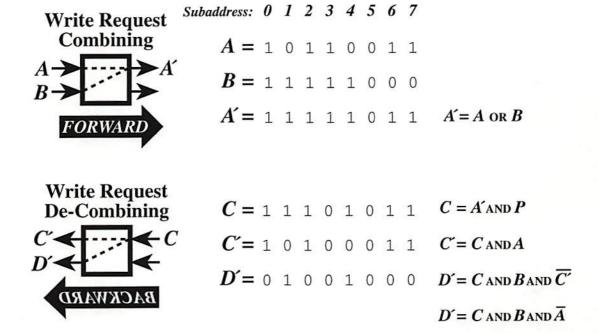

|   |              | 6.2.3              |             | equest Combining                              |

|   | 6.3          |                    |             | Add Algorithm                                 |

|   | 0.0          | 6.3.1              |             | plications                                    |

|   |              | 6.3.2              |             | istrations                                    |

|   |              | 6.3.3              |             | A works in the SMOEC                          |

|   | 6.4          | Specia             |             | Algorithms                                    |

|   |              | 6.4.1              |             | a Sort Algorithm                              |

|   |              | 6.4.2              |             | rix Transpose Facility                        |

|   |              |                    |             |                                               |

| 7 | and the same | September 11 to 12 |             | E PERFORMANCE 164                             |

|   | 7.1          |                    | mentation   |                                               |

|   |              | 7.1.1              |             | ture Implementation Considerations            |

|   |              | 7.1.2              |             | SMOEC Implementations                         |

|   |              |                    | 7.1.2.1     | Interconnection Network Communication Cycle   |

|   |              |                    |             | Composition                                   |

|    |      | 7.1.2.2 Development of Specific System Implementation              |    |

|----|------|--------------------------------------------------------------------|----|

|    |      | Recipes                                                            | 71 |

|    |      | 7.1.2.3 Three System Types: $I_C$ , $I_N$ , and $I_F$              | 72 |

|    |      | 7.1.2.4 Three System Sizes: $n = 10$ , $n = 15$ , and $n = 20$ 1   | 75 |

|    |      | 7.1.2.5 Nine System Recipes: Three Types With Three                |    |

|    |      | Sizes                                                              | 77 |

|    |      | 7.1.2.6 Loss Calculations for Implementation Examples 1            | 79 |

|    |      | 7.1.2.7 Completed Specific System Implementations with             |    |

|    |      | Varied Sizes                                                       | 83 |

|    |      | 7.1.3 Conclusions From Implementation Examples                     | 87 |

|    | 7.2  | Applications                                                       | 87 |

|    |      | 7.2.1 Simplified SMOEC Architectures For Specific Applications . 1 | 89 |

|    | 7.3  | Comparison with Other Shared Memory Computers                      |    |

| 8  | COI  | NCLUSIONS 19                                                       | 94 |

|    | 8.1  | Contributions                                                      | 97 |

| ΑP | PEN  | NDICES:                                                            |    |

| A  | wo   | LLASTON PRISM ANALYSIS 20                                          | 01 |

| В  | The  | Sim-FLAEM PROGRAM 20                                               | 05 |

|    | B.1  | Sim-FLAEM C Program Notes                                          | 05 |

|    | B.2  | Sim-FLAEM Program Correctness                                      |    |

|    | B.3  | Sim-FLAEM Trace Data Sample Output                                 |    |

|    | B.4  | Sim-FLAEM C Program Listing                                        |    |

| ΒI | BLIG | OGRAPHY 22                                                         | 21 |

# List of Figures

| 1.1<br>1.2 | The Shared Memory Model Computer. PE, Processing Element Hot Spot Formation (from [Kumar 86]). PE, Processing Element; | 5        |

|------------|------------------------------------------------------------------------------------------------------------------------|----------|

| 1.3        | MM, Memory Module                                                                                                      | 9        |

| 1.0        | sential design facets                                                                                                  | 11       |

| 2.1        | SMOEC: Block Diagram. Labels on arrows indicate number of com-                                                         |          |

| 2.2        | munication lines                                                                                                       | 13<br>17 |

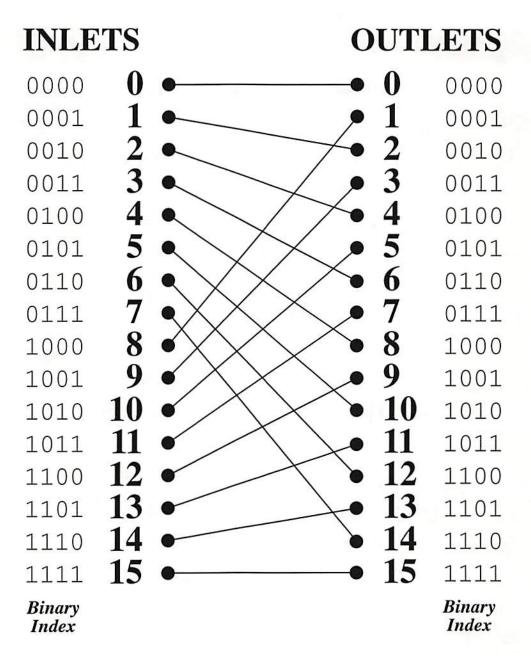

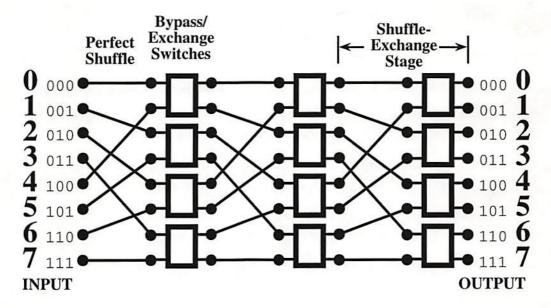

| 3.1        | A Perfect Shuffle                                                                                                      | 29       |

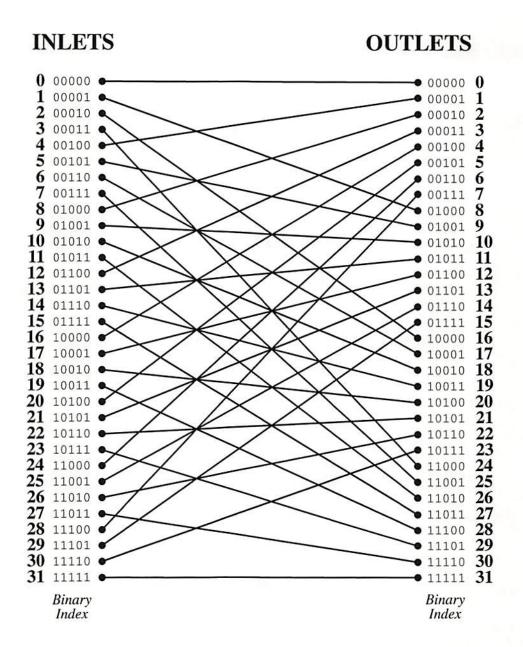

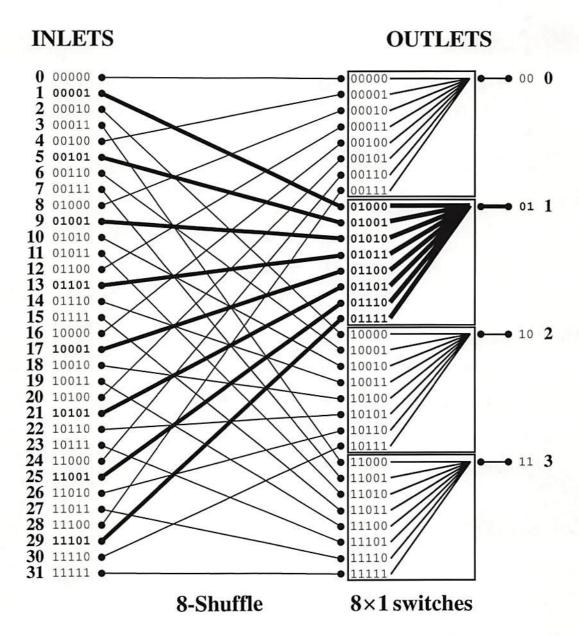

| 3.2        | An 8-shuffle on 32 nodes                                                                                               | 30       |

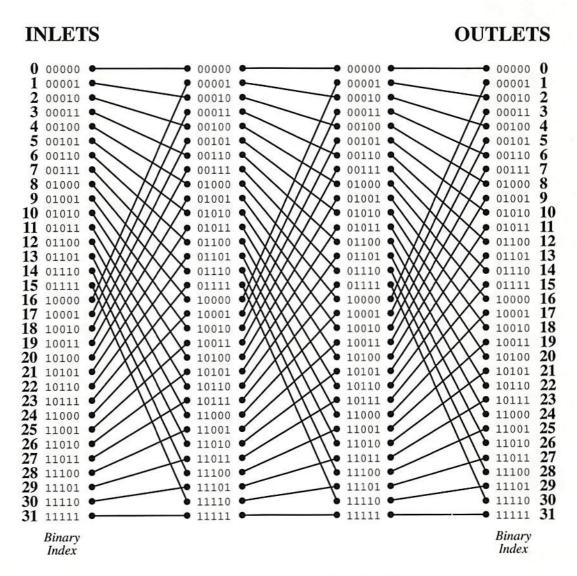

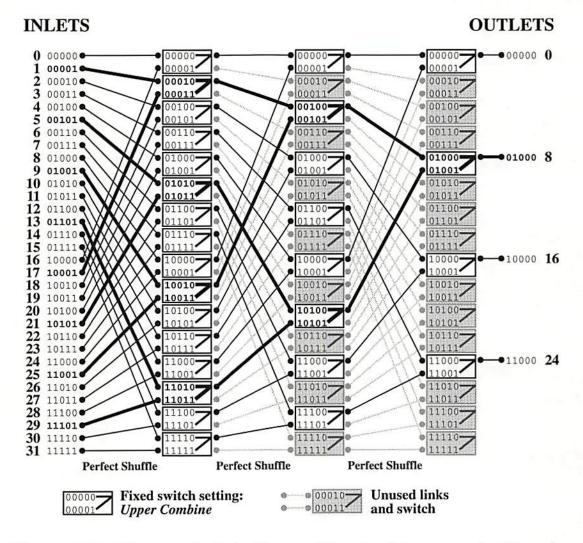

| 3.3        | Three consecutive perfect shuffles on 32 nodes                                                                         | 35       |

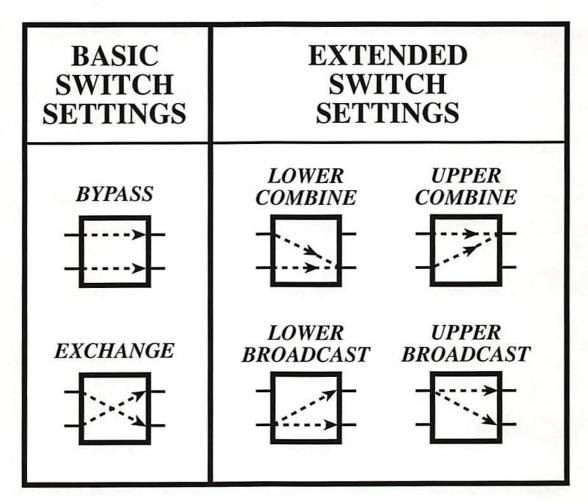

| 3.4        | Bypass/Exchange Switch Settings.                                                                                       | 36       |

| 3.5        | An Omega Network. Illustrated for $N = 8$ nodes                                                                        | 38       |

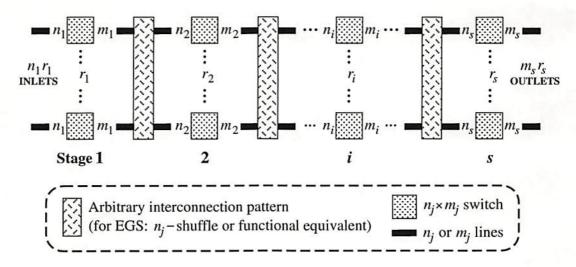

| 3.6        | Multistage Interconnection Network (MIN) general definition (in-                                                       | 00       |

| 5.0        | cluding EGS network definition)                                                                                        | 43       |

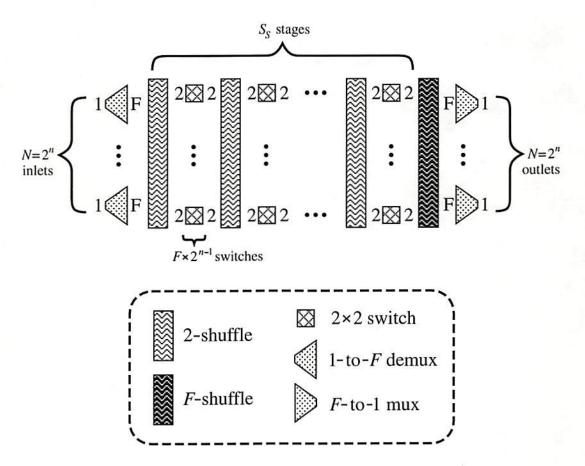

| 3.7        | Regular simplified class of EGS networks (RS-EGS networks)                                                             | 44       |

| 3.8        | RS-EGS network example: $N = 8 = 2^3$ , $F = 4 = 2^2$ , $S_S = 3$ , $W = 3$                                            |          |

| 5.0        | NF=32                                                                                                                  | 46       |

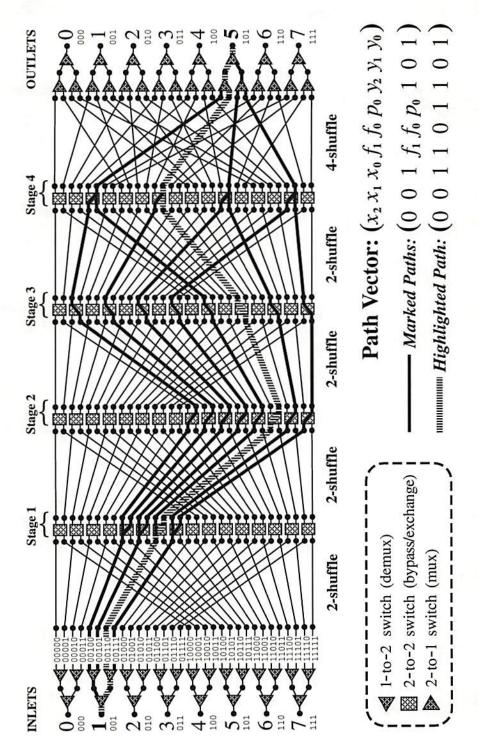

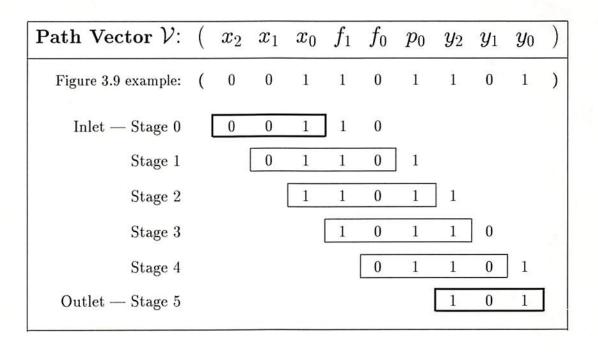

| 3.9        | Path vector illustration; $N=8$ , $F=4$ , $S_S=4$ , $P=8$                                                              | 56       |

| 0.0        |                                                                                                                        | 00       |

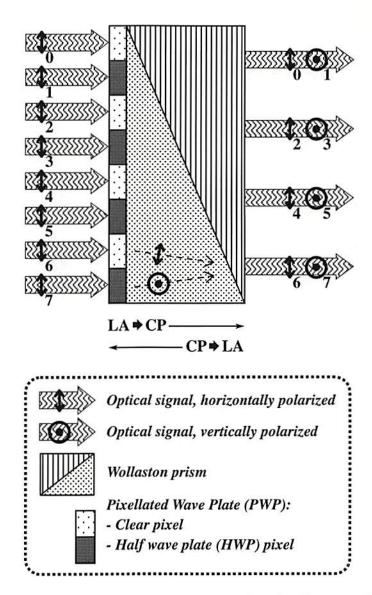

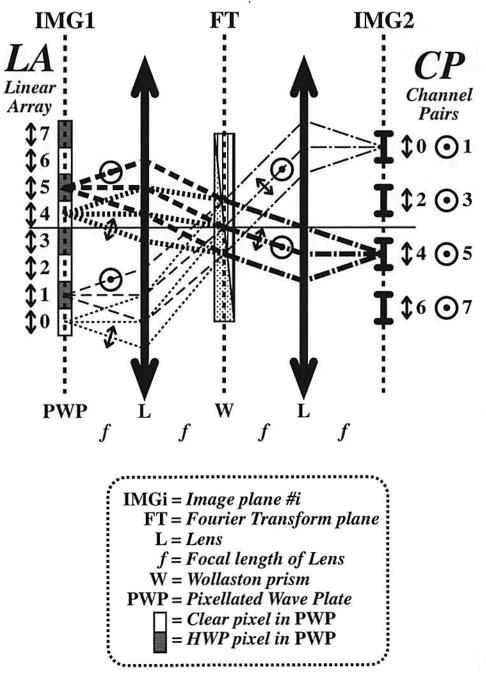

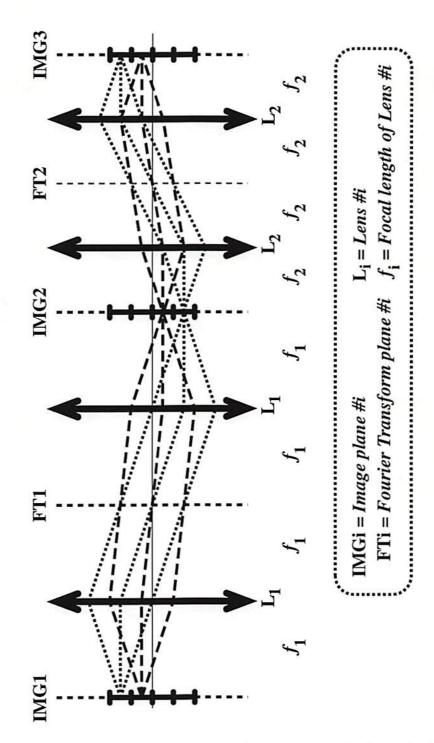

| 4.1        | Overview: Linear Array ↔ Channel Pairs Format Converter                                                                | 65       |

| 4.2        | Raytrace: LA $\leftrightarrow$ CP Format Converter                                                                     | 66       |

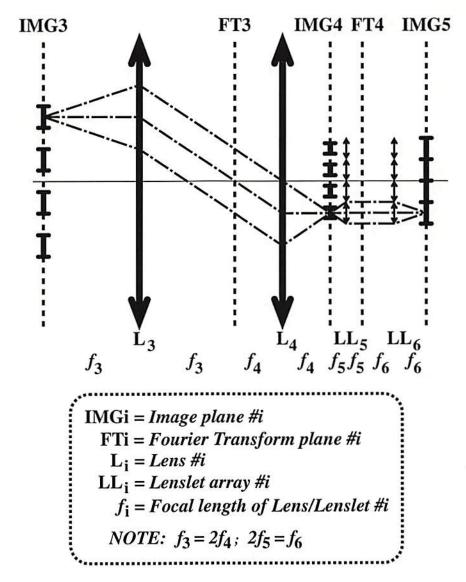

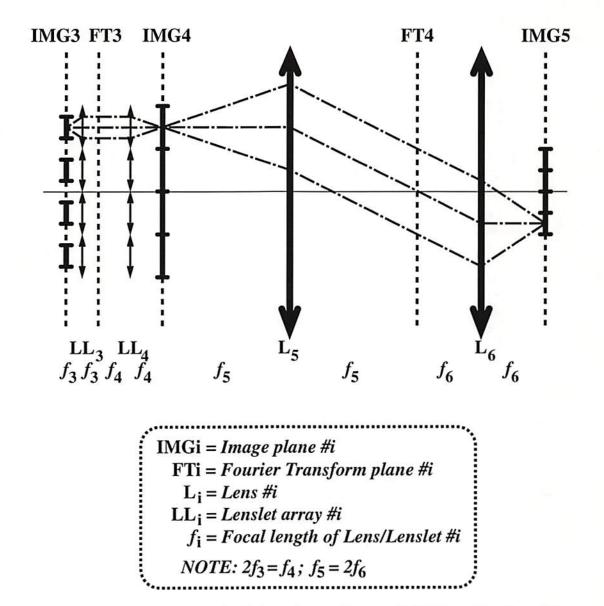

| 4.3        | Raytrace: Pixel Spacing Adjuster (PSA) — Design #1                                                                     | 69       |

| 4.4        | Raytrace: Pixel Spacing Adjuster (PSA) — Design #2                                                                     | 70       |

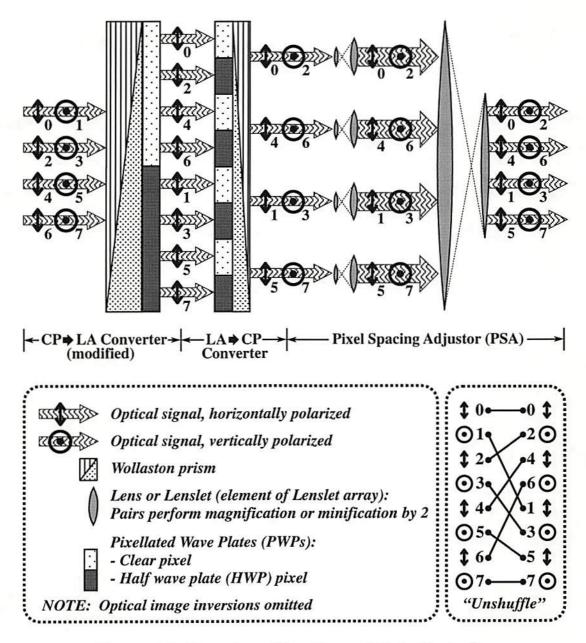

| 4.5        | Overview: The Channel Pair Unshuffle                                                                                   | 71       |

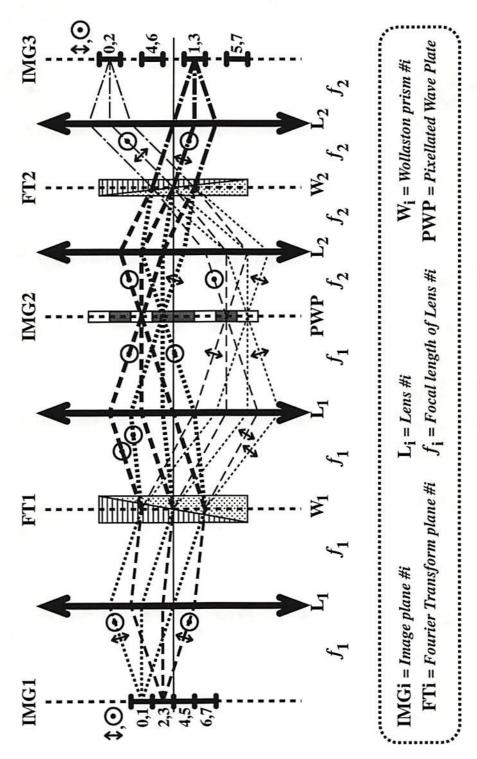

| 4.6        | Raytrace: CP Unshuffle w/o Wollaston Prisms (w/o PSA)                                                                  | 73       |

| 4.7        | Raytrace: CP Unshuffle with Wollaston Prisms (w/o PSA)                                                                 | 74       |

| 4.8        | Raytrace: CP Unshuffle (Complete)                                                                                      | 75       |

| 4.9        | Overview: The Channel Pair Exchange                                                                                    | 77       |

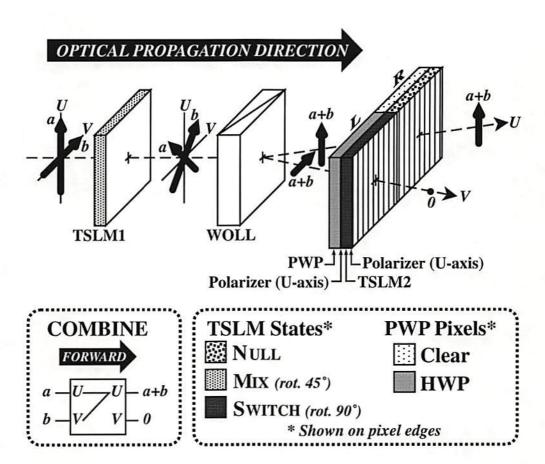

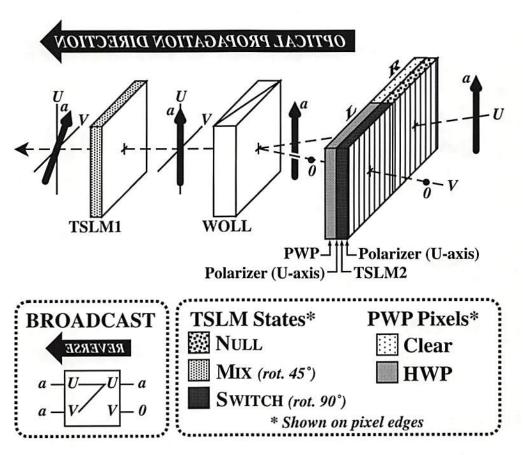

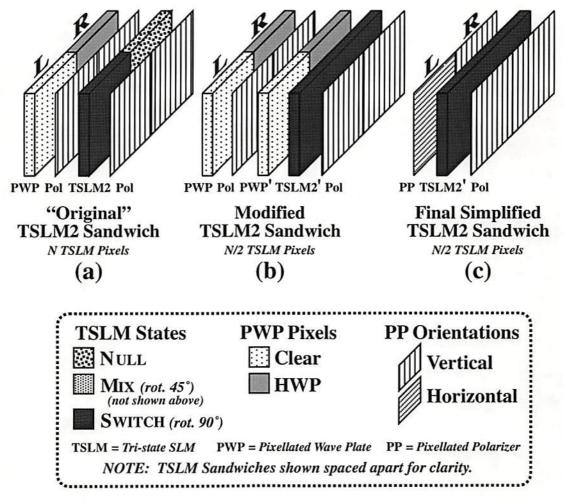

| 4.10       |                                                                                                                        | 80       |

| 4.11       | Overview: Shuffle-Exchange Stage Operation: Broadcast                                                                  | 82       |

|            |                                                                                                                        | viii     |

| 4.12 | Raytrace: An Unshuffle-Exchange Stage with Broadcast and Com-                  |

|------|--------------------------------------------------------------------------------|

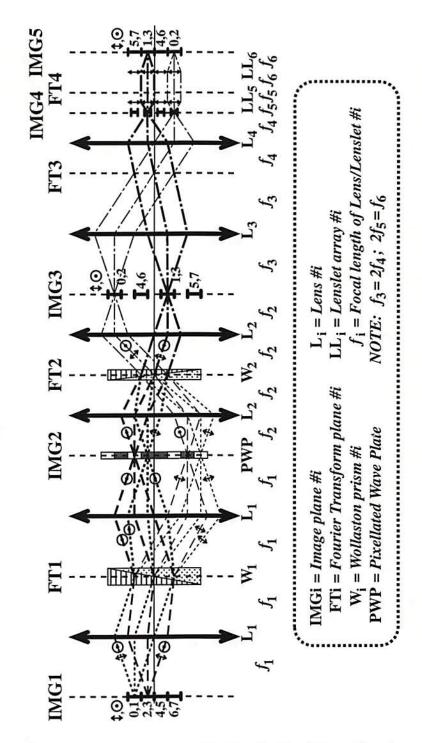

|      | bine Capability                                                                |

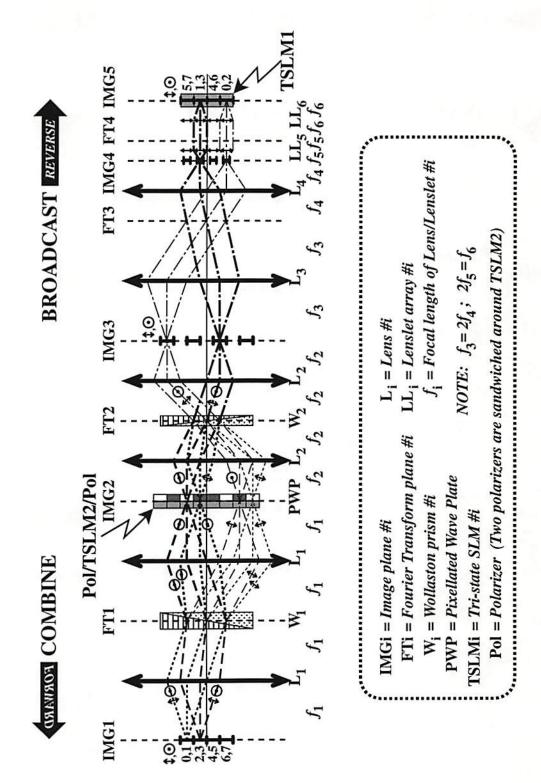

| 4.13 | Two Implementations for TSLM2                                                  |

| 4.14 | An LA-format 1×2 switch, used in "fan-out" implementation 88                   |

|      | An LA $\rightarrow$ CP-format 1×2 switch, used in "fan-out" implementation. 89 |

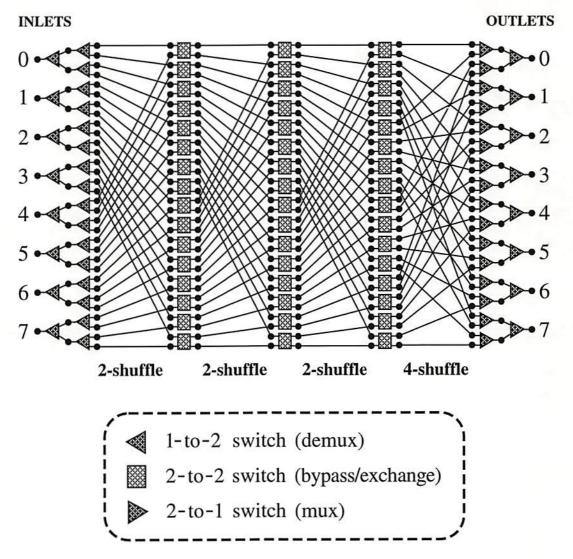

| 4.16 | A full 1×8 "fanout" (demultiplexer) stage 91                                   |

|      | An 8-shuffle on 32 nodes followed by an 8×1 fan-in switch 92                   |

|      | Three perfect shuffles on 32 nodes interspersed with pairwise com-             |

|      | bine switches                                                                  |

| 5.1  | FLAEM Flow Chart                                                               |

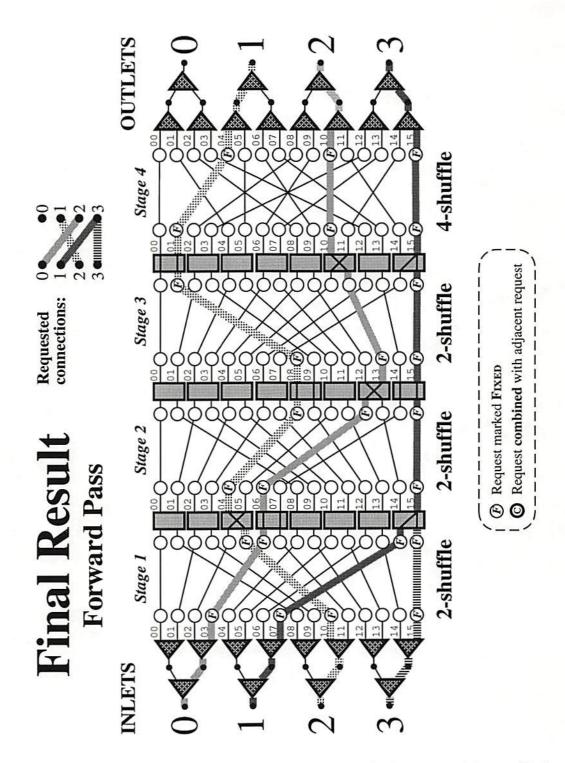

| 5.2  | The Basic-FLAEM procedure: Try #1: Forward Pass (P1) 120                       |

| 5.3  | The Basic-FLAEM procedure: Try #1: Reverse Pass (P2) 122                       |

| 5.4  | The Basic-FLAEM procedure: Try #2: Forward Pass (P3) 124                       |

| 5.5  | The Basic-FLAEM procedure: Try #2: Reverse Pass (P2) 127                       |

| 5.6  | The Basic-FLAEM procedure: Final Forward Pass (P3) 128                         |

| 5.7  | The Enhanced-FLAEM procedure: Combine-and-Split (S2) 130                       |

| 5.8  | The Enhanced-FLAEM procedure: Simple Split (S1) 131                            |

| 5.9  | Percentage of routed unrestricted connection patterns that took                |

|      | specified numbers of tries                                                     |

| 5.10 | Percentage of routed connection patterns that took specified num-              |

|      | bers of tries: comparison                                                      |

| 5.11 | Average number of tries per pattern, both cases shown                          |

| 6.1  | The Subaddress Field. First 8 bits illustrated                                 |

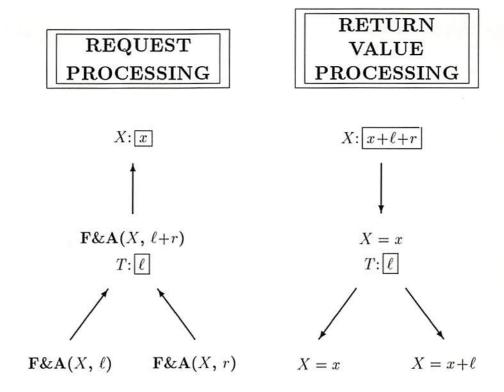

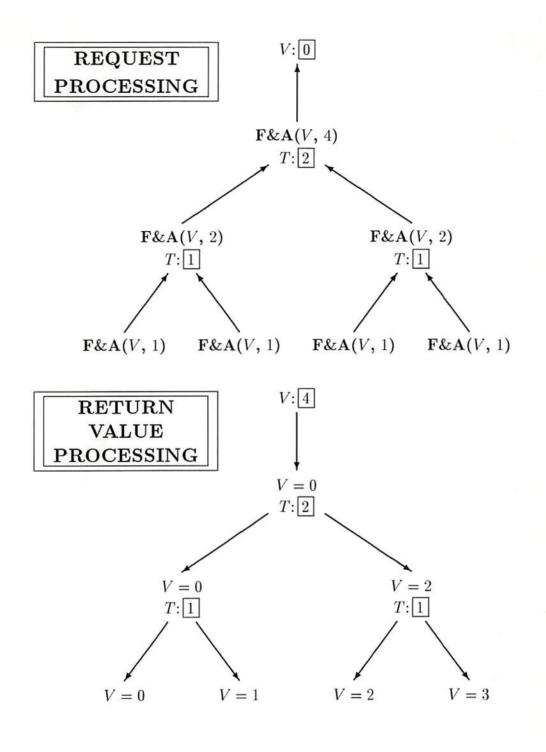

| 6.2  | Illustration of Fetch-and-Add (F&A)                                            |

| 6.3  | F&A Index Assignment Example                                                   |

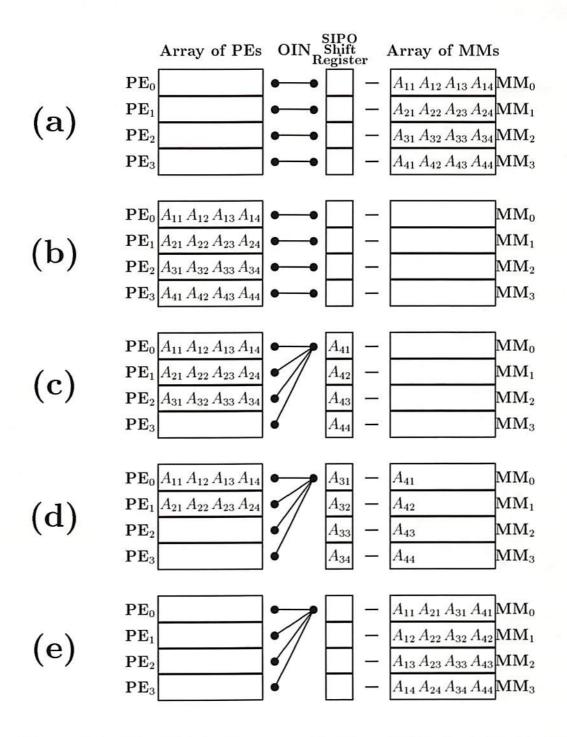

| 6.4  | The Matrix Transpose Facility. SIPO, Serial-In Parallel Out 163                |

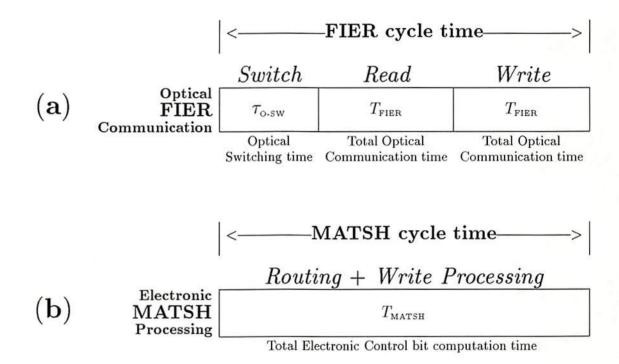

| 7.1  | Read/write phase components: (a) FIER communication; (b) MATSH                 |

|      | processing                                                                     |

| 7.2  | An optical repeater unit within the FIER optical network 182                   |

| A.1  | The Wollaston Prism                                                            |

# List of Tables

| 2.1 | Desired Features for the SMOEC                                                                       |

|-----|------------------------------------------------------------------------------------------------------|

| 3.1 | Richards' formulae: nonblocking conditions for $N \times N$ RS-EGS networks (from [Richards 93])     |

| 3.2 | Special cases of Richards' formulae                                                                  |

| 3.3 | RS-EGS network parameters for $n=2$ through $n=6$                                                    |

| 3.4 | RS-EGS network parameters for $n=7$ through $n=9$ 50                                                 |

| 3.5 | RS-EGS network parameters for $n = 10$ and $n = 11 \dots 51$                                         |

| 3.6 | RS-EGS parameters for two minimal device cost cases: $D$ , general case; $D'$ , restricted- $F$ case |

| 3.7 | Switch and link indices extracted from the path vector; $N=8$ , $F=4$ , $S_S=4$ , $P=8$              |

| 4.1 | TSLM settings                                                                                        |

| 5.1 | FLAEM simulation results                                                                             |

| 7.1 | SMOEC system implementation parameters for three system types 184                                    |

| 7.2 | SMOEC system implementation parameters for three system sizes . 185                                  |

| 7.3 | SMOEC system implementation parameters for three system types                                        |

|     | and three system sizes                                                                               |

| B.1 | Summaries of FLAEM simulation C program routines 206                                                 |

| B.2 | State variable correspondences                                                                       |

# List of Acronyms

#### Parallel Computer Architecture Acronyms

- MIMD Multiple Instruction streams over Multiple Data streams: Parallel computer model employing independent processing elements.

- **SMOEC** Shared Memory Optical/Electronic Computer: The parallel MIMD shared-memory computer system architecture presented herein.

- FIER Free-space Interconnection with Externally-controlled Routing: The passive optical interconnection network within the SMOEC.

- MATSH Multifunctional Arbitrator of Traffic for Shuffle-exchange Hardware: The single-stage recirculating electronic shuffle-exchange hardware used to control the FIER in a circuit-switched manner.

- FLAEM Flexible Localized Algorithm for EGS-network Management: The parallel algorithm used on the MATSH to compute the bypass/exchange switch settings for the FIER.

- CSDI Control Signal Distribution & Interface: The buffers and interface from the MATSH control unit to the FIER optical network.

- PE Processing Element: One of N individual processors.

- MM Memory Module: One of N modular blocks of the shared memory.

- MIN Multistage Interconnection Network: it A network with multiple stages of switching elements interconnected by an arbitrary interconnection pattern.

- EGS Extended Generalized Shuffle: A MIN with an interconnection topology invented by G. Richards [Richards 91a].

- RS-EGS Regular Simplified EGS: A particular set of additional restrictions on the general EGS definition, which are employed in the FIER.

- **E-SE** Electronic Shuffle-Exchange: The single electronic shuffle-exchange stage within the MATSH.

- O-SE Optical Shuffle-Exchange: One of the  $S_S$  passive optical shuffle-exchange stages within the FIER.

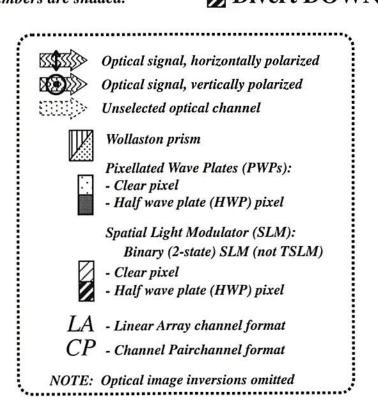

#### FIER Optical Network Acronyms

- LA Linear Array: An array of regularly spaced uniformly polarized individual optical channels.

- **CP** Channel Pairs: An array of superimposed pairs of orthogonally polarized optical channels.

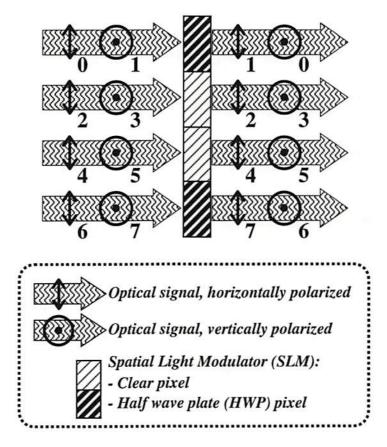

- SLM Spatial Light Modulator: A two-dimensional array of optical switching devices (pixels).

- **TSLM** Tri-state SLM: An SLM with tri-state optical swiching elements, designed for use in the FIER.

- PSA Pixel Spacing Adjuster: Optical setup designed for the FIER to adjust pixel spacings to enable cascadability of optical shuffle-exchange (O-SE) stages.

- HWP Half-Wave Plate: Optical device capable of (e.g.) rotating a linear polarization by 90° when oriented at 45° to the incoming linear polarization axis.

- QWP Quarter-Wave Plate: Optical device capable of (e.g.) turning linear polarization into circular polarization, and vice-versa.

- PWP Pixellated Wave Plate: Fixed wave plate divided into pixels of HWP and null effects.

- FLC Ferroelectric Liquid Crystal: Material from which polarization-switching SLMs (and TSLMs) may be constructed.

# List of Notation

#### General RS-EGS Network Parameters

| N     |                         | The number of inlets in a MIN. $N$ is also the number of outlets when the MIN under consideration is an RS-EGS network.                                                                                                                                      |

|-------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| n     | $= \log_2 N$            | The number of bits in an inlet address.                                                                                                                                                                                                                      |

| F     |                         | The amount of "fan-out" and "fan-in" in an RS-EGS network. $F=2^f$ for a restricted- $F$ network.                                                                                                                                                            |

| f     | $=\log_2 F$             | The number of stages of $1\times 2$ switches to implement a $1\times F$ "fan-out" section (or $2\times 1$ switches for a $F\times 1$ "fan-in" switch in an RS-EGS network; each stage is composed of a perfect shuffle and an array of $2\times 2$ switches. |

| W     | $= N \cdot F$           | The "width" (number of links) of the main section of an RS-EGS network.                                                                                                                                                                                      |

| $S_S$ | $= \mathcal{O}[\log N]$ | The number of stages in the "main section" of an RS-EGS network (the main section consists of all the perfect shuffles and $2\times 2$ switches, and excludes the "fan-out" and "fan-in" stages and the final $F$ -shuffle).                                 |

| $S_T$ | $=S_S+2$                | The total number of stages in an RS-EGS network, when the "fan-out" and "fan-in" sections are counted as one stage each.                                                                                                                                     |

| $S_F$ | $=S_S+2f$               | The total number of stages in a restricted- $F$ RS-EGS network, when the "fan-out" and "fan-in" sections are each composed of $f$ stages of $1\times 2$ or $2\times 1$ switches, respectively.                                                               |

#### Routing and Write Arbitration Parameters

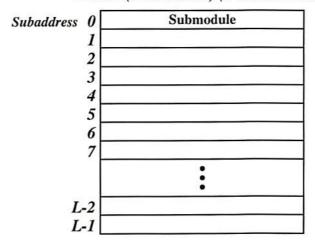

D Number of bits of data in an MM

B Number of bits per submodule (word) within an MM

L = D/B Number of submodules (words) in an MM

= Number of bits in a subaddress field

C Number of wires (or fibers) per MATSH (E-SE) node

K = L/C Number of submodules transmitted per MATSH wire

U Number of status bits for MATSH routing processing

$E = n + f + S_S$  Number of bits in a Path Vector

J = E + U Number of bits per read operation

#### FIER Optical Network Switching Parameters

$au_{ ext{o-sw}}$  Time to simultaneously load and switch the optical

switching components (FLC TSLMs, described in

Section 4.2.6)

= Time to simultaneously switch all the optical

bypass/exchange switches

= Optical reconfiguration time

$r_{\text{FIER}}$  Data rate through the FIER (bps)

$T_{\rm FIER} = D/r_{\rm FIER}$  Total optical communication time: time to access

(read from or write to) an entire MM

## FIER Optical Network Power and Loss Parameters

| $E_{ m min}^{{\scriptscriptstyle ({ m Det})}}$ |                                                                     | Minimum energy required for bit discrimination at a detector in the FIER                         |

|------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| $P_{ m min}^{ m (Det)}$                        | $= E_{\text{min}}^{\text{\tiny (Det)}} \cdot r_{\text{\tiny FIER}}$ | Minimum power required for bit discrimination at a detector in the FIER, for a given bit rate    |

| $P_{	ext{INPUT}}^{(	ext{LD})}$                 |                                                                     | Power from the laser diodes input into the FIER                                                  |

| $\mathcal{L}$                                  |                                                                     | Total optical loss factor throughout the entire FIER optical network                             |

| $\mathcal{L}_{	exttt{TOL}}$                    | $= P_{\text{INPUT}}^{\text{(LD)}} / P_{\text{MIN}}^{\text{(Det)}}$  | Tolerable optical loss factor in the FIER, without optical repeaters $$                          |

| $\mathcal{R}$                                  |                                                                     | Number of repeaters required to be included in the FIER to keep the loss above a tolerable level |

# MATSH Routing Processor Switching Parameters

| $r_{ m W}$                                                                | Wire (or fiber) data rate between E-SE stage cycles in the MATSH                                                          |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| $\overrightarrow{	au}_{	ext{xmit}}^{	ext{(read)}}$                        | Time to transmit routing bits between E-SE stage cycles within the MATSH (in the PE $\rightarrow$ MM "forward" direction) |

| $\overrightarrow{\mathcal{T}}_{\text{XMIT}}^{(\text{WRITE})}$             | Time to transmit routing and write arbitration bits between E-SE stage cycles within the MATSH (forward)                  |

| $\overrightarrow{\tau}_{	ext{PROC}}^{	ext{(READ)}}$                       | Time to process routing bits for one E-SE stage cycle within the MATSH (forward)                                          |

| $\overrightarrow{\tau}_{_{\mathrm{PROC}}}^{_{(\mathrm{WRITE})}}$          | Time to process routing and write arbitration bits for one E-SE stage cycle within the MATSH (forward) $$                 |

| $\overset{\leftarrow}{\mathcal{T}}_{_{\mathrm{XMIT}}}^{(\mathrm{READ})}$  | Time to transmit routing bits between E-SE stage cycles within the MATSH (in the MM $\rightarrow$ PE "reverse" direction) |

| $\overset{\leftarrow}{\mathcal{T}}_{_{\mathrm{XMIT}}}^{(\mathrm{WRITE})}$ | Time to transmit routing and write arbitration bits between E-SE stage cycles within the MATSH (reverse) $$               |

| $\overset{\leftarrow}{\mathcal{T}}_{\text{PROC}}^{(\text{READ})}$         | Time to process routing bits for one E-SE stage cycle within the MATSH (reverse) $$                                       |

| $\overset{\leftarrow}{\mathcal{T}}_{\text{PROC}}^{(\text{WRITE})}$        | Time to process routing and write arbitration bits for one E-SE stage cycle within the MATSH (reverse) $$                 |

| $	au_{	exttt{PROC}}^{(\star)}$                                            | Specially defined processing time: See Section 7.1.2.5 (forward or reverse)                                               |

| $\overset{\rightarrow}{\Psi}_{\text{read}}$                               | Number of forward read passes (routing bits only) in a routing cycle                                                      |

| $\overrightarrow{\Psi}_{	ext{write}}$                                     | Number of forward write passes (write arbitration bits) in a routing cycle                                                |

| $\overrightarrow{\Psi}_{\text{read}}$                                     | Number of reverse read passes (routing bits only) in a routing cycle                                                      |

| $\overset{\rightarrow}{\Psi}_{\text{write}}$                              | Number of reverse write passes (write arbitration bits) in a routing cycle                                                |

#### MATSH Routing Processor Switching Parameters (cont.)

$T_{\text{XMIT}}$  Time devoted to data transmission in the MATSH

$$= S_F( \qquad \stackrel{\rightarrow}{\Psi}_{\text{read}} \stackrel{\rightarrow}{\tau}_{\text{xmit}}^{(\text{read})} \ + \stackrel{\rightarrow}{\Psi}_{\text{write}} \stackrel{\rightarrow}{\tau}_{\text{xmit}}^{(\text{write})} \\ + \stackrel{\leftarrow}{\Psi}_{\text{read}} \stackrel{\leftarrow}{\tau}_{\text{xmit}}^{(\text{read})} \ + \stackrel{\leftarrow}{\Psi}_{\text{write}} \stackrel{\leftarrow}{\tau}_{\text{xmit}}^{(\text{write})} )$$

$T_{\text{PROC}}$  Time devoted to data processing in the MATSH

$$= S_F( \overrightarrow{\Psi}_{\text{READ}} \overrightarrow{\tau}_{\text{PROC}}^{(\text{READ})} + \overrightarrow{\Psi}_{\text{WRITE}} \overrightarrow{\tau}_{\text{PROC}}^{(\text{WRITE})} + \overleftarrow{\Psi}_{\text{READ}} \overleftarrow{\tau}_{\text{PROC}}^{(\text{READ})} + \overleftarrow{\Psi}_{\text{WRITE}} \overleftarrow{\tau}_{\text{PROC}}^{(\text{WRITE})} )$$

$T_{\text{MATSH}}$  Total electronic control bit computation time in the MATSH

$$= T_{\text{XMIT}} + T_{\text{PROC}}$$

$$= S_F \left[ \begin{array}{ccc} \overrightarrow{\Psi}_{\text{READ}} & (\overrightarrow{\tau}_{\text{PROC}}^{(\text{READ})} & + \overrightarrow{\tau}_{\text{XMIT}}^{(\text{READ})} ) \\ + \overrightarrow{\Psi}_{\text{WRITE}} & (\overrightarrow{\tau}_{\text{PROC}}^{(\text{WRITE})} & + \overrightarrow{\tau}_{\text{XMIT}}^{(\text{WRITE})} ) \\ + \overleftarrow{\Psi}_{\text{READ}} & (\overleftarrow{\tau}_{\text{PROC}}^{(\text{READ})} & + \overleftarrow{\tau}_{\text{XMIT}}^{(\text{READ})} ) \\ + \overleftarrow{\Psi}_{\text{WRITE}} & (\overleftarrow{\tau}_{\text{PROC}}^{(\text{WRITE})} & + \overleftarrow{\tau}_{\text{XMIT}}^{(\text{WRITE})} ) \right]$$

# Chapter 1

## INTRODUCTION

In past years, optical computing research has often focussed on the design of individual computer hardware subsystems implemented with optical devices. However, integration of these subsystems into a complete computer system has often proven to be impractical since the hardware was often designed without consideration for system design requirements. For example, several optical interconnection networks were designed that looked attractive, yet lacked practical control mechanisms. In more recent years there has been a growing realization among designers of optical hardware that system concerns are essential to the usefulness of any proposed optical subsystem, so optical engineers are beginning to pay more attention to hitherto neglected (or postponed) aspects of computer system design such as interconnection network control techniques.

Over the course of the past decade, there has been a dawning realization among optical computing researchers that a hybrid combination of electronic computing and optical communication holds the most promise for powerful practical systems [Jenkins 92, Lohmann 95, Schenfeld 95]; i.e., the trend is away from "optical computing" and toward "optics in computing." Thus the research presented herein reflects a system-level orientation to design decisions, incorporating electronic processing and optical communication subsystems that were conceived from the beginning to work together.

The hybrid shared memory computer system described in the following pages was designed to incorporate a passive optical interconnection network as an essential central component. The system was designed to emphasize the strengths and balance the weaknesses inherent in a passive optical design. Explicit routing algorithms and communication techniques were developed in concert with the system architecture and interconnectin network design so that these important system aspects would not limit performance. The intent was provide a detailed design for a general-purpose MIMD computer system architecture that exhibits flexibility, realizability, and scalability.

Parts of this work have been previously published as follows. Chapter 1 (Introduction), Chapter 2 (System Architecture), and Chapter 6 (Communication Algorithms) are primarily drawn from [Waterson 91] and [Waterson 94a]. Chapter 4 (Optical Interconnection Network Hardware) is taken from [Waterson 94b], except for Section 4.3 (Optical EGS Hardware Design) which is entirely new. An overview of Chapter 5 (Network Routing Algorithm) was published as [Waterson 95]. Chapter 3 (Interconnection Network Topology and Routing [Review]) and Chapter 7 (Architecture Performance) are newly presented here, and Chapter 8 (Conclusions) draws from all these sources.

#### 1.1 Background

Parallel processors have been receiving a great deal of research interest largely because many desired computational applications continue to greatly exceed the capabilities of current uniprocessor computers [Beetem 85, Butler 93, Hwang 93]. Parallel processors may provide increased performance at the cost of increased hardware complexity. The ultimate goal of parallel computer design is to use N processing elements to reduce the execution time by a factor of N relative to that of a comparable uniprocessor. In general the speedup actually achieved by a parallel processor can be significantly less than N due primarily to data dependencies and communication contention [Stone 73]. Furthermore, the theoretical speedup obtained in an abstract parallel computation model may be significantly higher than in a parallel computer architecture (a realization of the model) [Jenkins 86].

Several abstract models of parallel computation have been developed and studied by the computer science and parallel processing communities [Fortune 78, Schwartz 80]. The shared memory models are among the most computationally powerful of these models. They benefit from substantial theoretical foundations, and many algorithms have been mapped onto these models in order to characterize theoretically optimum parallel performance [Schwartz 80, Borodin 85]. Thus, parallel machine architectures based on shared memory models should share these benefits. However, achieving fine-grained parallelism (very large numbers of relatively simple processing elements) based on a shared memory model is a difficult goal primarily due to the complexity of the interconnection network hardware and its associated control.

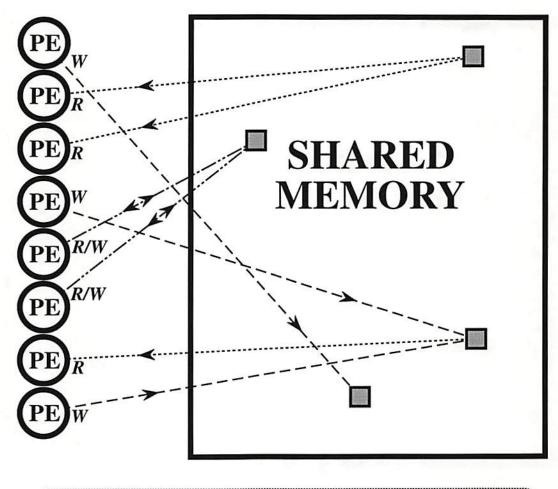

The shared memory model of computation [Fortune 78, Schwartz 80, Vishkin 83, Borodin 85, Jenkins 86] consists of a set of processing elements (PEs) that can all communicate (read and/or write) simultaneously with a shared memory in a single time step (Figure 1.1). Each PE is a uniprocessor capable of carrying out an independent program, so that the set of PEs can operate in a MIMD (Multiple Instruction stream over Multiple Data stream) manner. The shared memory comprises a set of memory cells. In this ideal model any PE can communicate with any memory cell in one time step. Therefore, all PEs can simultaneously access different cells of the shared memory. In addition, in the strongest version of the shared memory model (CRCW = Concurrent Read, Concurrent Write) multiple PEs can simultaneously access (read from and/or write to) the same individual memory cell [Hwang 93].

Several compromises of the shared memory model ideal must be made in order to allow a physical realization. For example, the interconnection network is a particularly critical element, and usually the limiting factor, of parallel architectures based on a shared memory computation model. Therefore, focusing design effort on the optimization of this element is essential.

Parallel access to memory is a key feature of a physical realization of a shared memory machine. By reducing addressing bottlenecks compared to a conventional von Neumann architecture a substantial improvement in performance can be achieved. This parallel memory access is commonly approximated by dividing the shared memory into memory modules (MMs), and providing an interconnection network between the PEs and MMs. This interconneciton network is used to perform read and write (and other) operations, requiring an amount of time which

W = Write

R = Read

R/W = Inseparable Read and Write (such as fetch-and-add)

Figure 1.1: The Shared Memory Model Computer. PE, Processing Element.

is dependent on N, the number of PEs and MMs. Typically (as in the architecture proposed here) the number of PEs and the number of MMs are set to be equal to balance PE and MM communication requirements.

Highly parallel electronic processing architectures are primarily limited by the characteristics of their electronic interconnection network [Guha 90]. Unfortunately, complex global interconnection topologies can be extremely difficult to implement electronically due to complexity limitations of two-dimensional VLSI layouts or three-dimensional wire layouts (or even proposed three-dimensional VLSI layouts) [Giles 86, Feldman 88]. Therefore it is worth considering the use of optics in implementing the interconnection network in the proposed shared memory machine.

#### 1.2 Motivation

The imaging, superposition, and three-dimensional nature of optics allow complex interconnection topologies to be implemented optically with reduced complexity from electronic implementations [Giles 86, Barakat 87]. Optical imaging allows massive parallelism when interconnecting from pixel to corresponding pixel, without requiring fabrication of a separate physical path for each connection. Optical superposition allows light beams to pass essentially unaffected through each other, allowing reduced hardware complexity by eliminating the necessity to reserve separate physical space for each data path in a network [Jenkins 88]. The three-dimensional nature of optics allows further reduced complexity over the planar constraints of VLSI [Giles 86]. Optical hardware also has the advantage of

being capable of operation at extremely high bandwidths [Guha 90, Feldman 88, Hartman 86].

Although optical superposition is used in optical interconnection networks to reduce complexity, it is precisely this difficulty of getting optical beams to interact that makes optical switching a less mature technology than electronic switching. Thus the trend in recent years has been away from designing all-optical computer systems and instead towards designing hybrid computer systems with electronic processing and optical interconnecitons [Jenkins 92, Lohmann 95, Schenfeld 95]. Therefore, in the design of the parallel computer architecture presented herein, all nonlinear processing operations (computations) will be performed electronic cally. Similarly, although optical memory is somewhat further developed, electronic memories will also be used. A novel optical interconnection network is designed to satisfy the communications requirements for this computer system.

Since the interconnection network is critical to the overall machine performance, its design and control is central to the design of a shared memory computer. However, specifying an efficient high performance complex interconnection network as an integral part of a parallel computer architecture does not provide sufficient basis for believing the architecture to be an improvement over other computers with less capable interconnection networks. A valid comparison cannot be made between architectures or networks without careful consideration of the associated control algorithms. Whereas an apparently "more powerful" network might be capable of great flexibility in its routing (with perhaps even redundant paths available for fault tolerance), such a network can prove to be undesirable due to the associated cumbersome and slow control algorithms. In fact, it is quite possible for a control

algorithm to have worse time complexity behavior than the total time delay of data transfer through the network.

One important aspect of interconnection network control is the method of resolving routing conflicts. Buffered networks (typically used in electronic networks) provide one very common type of conflict resolution. In a buffered network conflicts in a switching node are resolved by routing one message and buffering (saving in a local memory stack) the other message, which is sent later. However, a major drawback of buffering is the possibility of network performance degradation due to "hot spot" formation [Pfister 85b, Kumar 86, Lee 86, Thomas 86, Yew 86]. Hot spots in a buffered network are formed when a large number of simultaneous references are made to the same "hot" memory location. Requests may stack up and overflow the buffer sizes, with backups propagating backward through the interconnection network in a tree pattern, until the backup affects the flow through most or all of the network (see Figure 1.2.)

Non-buffered networks eliminate the possibility of hot spot formation, but require the problem of routing conflict resolution to be dealt with in some other manner. A non-buffered network is employed in the interconnection network presented here, and allows passive optical switching to be used for its implementation. The resulting network can achieve greater throughput and can incorporate a novel conflict resolution technique implemented in a centralized controller (discussed in Chapter 5).

# Propagation of Saturated Queues & Buffers from Hot MM PP PP Path or device blocked by "hot spot" effect Clear path Queue Hold Buffer Saturated Queues & Buffers Bypass/Exchange Switch

Figure 1.2: Hot Spot Formation (from [Kumar 86]). PE, Processing Element; MM, Memory Module.

#### 1.3 Design Philosophy

Tradeoffs between control algorithm complexity and interconnection network characteristics must be an integral part of the design process. Control algorithm design must be undertaken simultaneously with interconnection network design to obtain true performance improvement. Similarly, hardware implementation must also be considered (at least at a high level) simultaneously with computer design so that the design may be physically realized. Control algorithm design also affects the hardware decisions, and vice versa, since control signals must be able to reach the actual control sites. Therefore this paper presents the design of the Shared Memory Optical/Electronic Computer (SMOEC) as a design consisting of three essential facets: architecture, control algorithm, and hardware. These three facets are like the three legs of a tripod; if one leg is weak, the whole tripod is weak (see Figure 1.3).

For example, the triple focus of the design philosophy allowed the choice of a passive optical interconnection network to impact the control algorithm and system architecture design. In this way, the SMOEC was designed with an optical interconnection network as an integral element of the design. This method is in contrast to taking the idea of an optical network and inserting it in a preexisting electronic parallel computer design that was intended to be used with a fundamentally different electronic interconnection network.

The triple focus of this research on architecture, hardware, and control is part of a trend towards systems design among those designing hybrid optical/electronic systems which incorporate novel optical subsystems. Some recent work in the "optics in computing" field explicitly advocates attention to system-level design

Figure 1.3: System Design Tripod: System viability is supported by three essential design facets.

concerns for hybrid systems [e.g. Pinkston 92, Schenfeld 95]. Part of the research presented herein, published previously in [Waterson 91], was an early proponent of a system-level design focus. This dissertation, along with other previously published parts of this work [Waterson 94a, Waterson 94b, Waterson 95], contribute further support and advocacy of a system-level design emphasis for hybrid optical/electronic systems.

# Chapter 2

## SYSTEM ARCHITECTURE

Optimizing the balance of compromises required for physical implementation of a shared memory model machine is the driving force behind the Shared Memory Optical/Electronic Computer (SMOEC) architecture. The SMOEC is designed to satisfy a number of desired features, as summarized in Table 2.1. These desired features were chosen knowing that a passive optical interconnection network would be employed in the SMOEC. Thus the characteristics of the optical interconnection network can be maximally exploited by the overall SMOEC architecture, and at the same time the overall architecture accommodates the weaknesses of the optical interconnection network with minimal effect on computational performance.

#### 2.1 SMOEC Architecture Overview

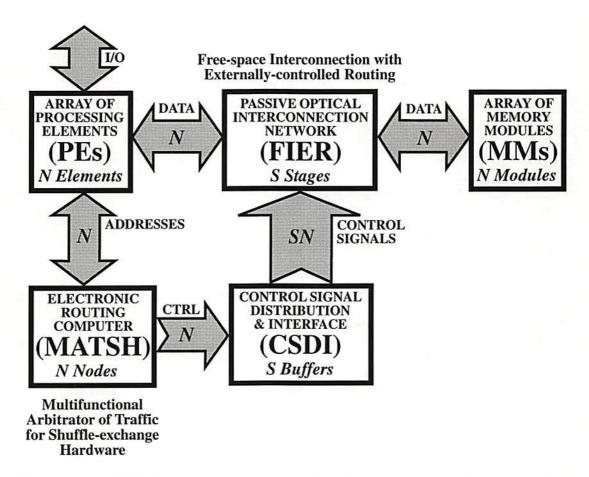

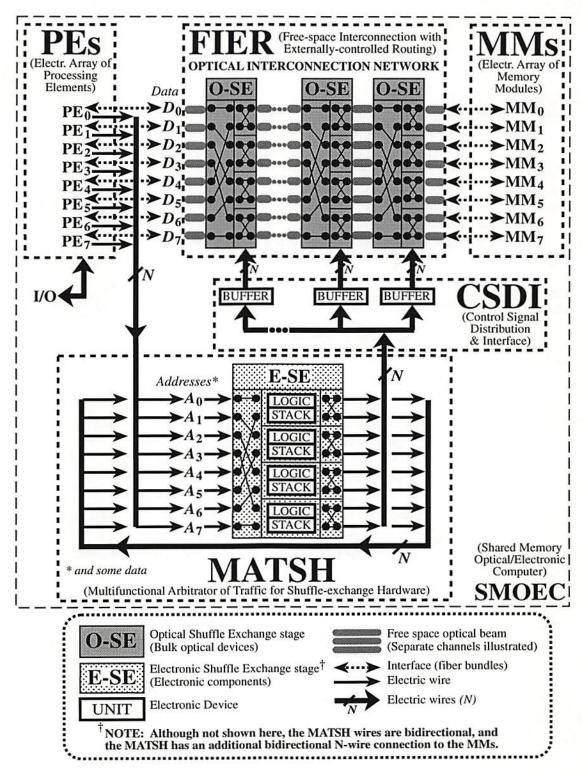

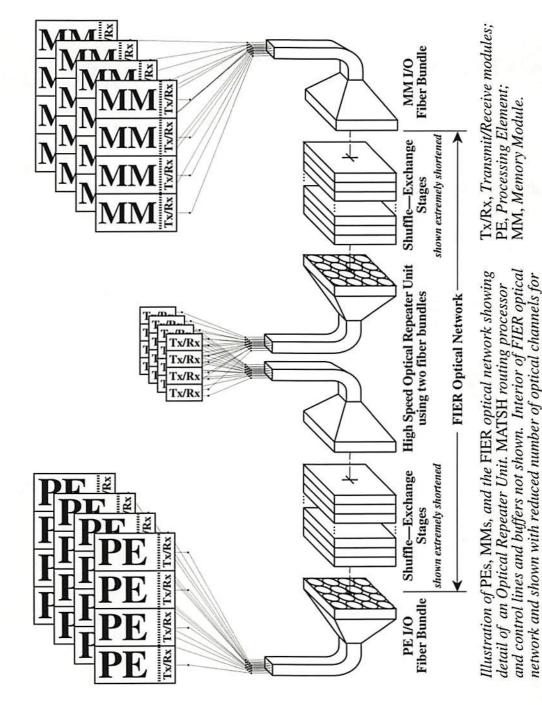

The functional architecture of the SMOEC is shown in Figure 2.1. It consists of a bank of N processing elements (PEs) connected to a bidirectional optical

Figure 2.1: SMOEC: Block Diagram. Labels on arrows indicate number of communication lines.

- ▶ Shared memory computation model as architectural basis

- ▶ MIMD (Multiple Instruction, Multiple Data stream) operation

- ▶ Physically parallel (not buffered), simultaneous memory reads and writes

- ▶ Memory access completion within  $\mathcal{O}[1]$  passes through the network (A network pass may take  $\mathcal{O}[\log N]$  time)

- ▶ High throughput between any PE (or set of PEs) and MM

- ▶ Parallel fetch-and-add (see Appendix 6.3) capability (to restricted MM cells)

- ▶ Prevention of hot spot formation

- ▶ Fine-grained parallelism  $(N \sim 10^3 10^6)$

Table 2.1: Desired Features for the SMOEC.

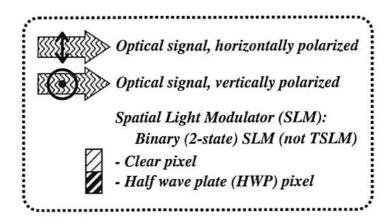

interconnection network called the Free-space Interconnection with Externally-controlled Routing (FIER), which is connected at its other end to a bank of N Memory Modules (MMs). The FIER optical network consists of a sequence of S shuffle-exchange stages, where  $S = \mathcal{O}[\log N]$ . The bank of PEs is also connected to the inlet links of a single recirculating electronic shuffle-exchange stage. This is the Multifunctional Arbitrator of Traffic for Shuffle/exchange Hardware (MATSH) which processes address bits from the PEs to compute the control settings for the FIER switches. The Control Signal Distribution & Interface (CSDI) buffers the control bits until it is time to switch the FIER optical network to accommodate new routing paths. The optical switches are then all set at the same time, opening the FIER for bidirectional communication between connected PEs and MMs. In order to achieve high bandwidth data transfer, the FIER is designed to be optically

passive, and to use near-term optical technology. The choice of passive optical hardware has substantial architectural and control implications.

To illustrate a typical mode of operation and to introduce how the SMOEC subsystems interact, a simplified overview of the handling of simultaneous read requests is provided. Communications in the SMOEC are handled in separate phases, each consisting of a single type of request (such as read or write) to facilitate conflict resolution. Because of these globally coordinated communication phases, the SMOEC is not a pure MIMD (Mulitple Instruction, Multiple Datastream) computer in the most strict sense, but is considered a "primarily MIMD" computer. During the read phase, each PE that requires information from a MM forms a read request consisting of the MM index (address) it desires to read from. These addresses are fed in parallel to the MATSH control unit. Using the routing algorithm (explained in Chapter 5), the MATSH sequentially computes the appropriate switch settings for the FIER optical network and passes them to the CSDI buffering unit. When all settings are computed, all bits are sent simultaneously from the CSDI to the appropriate FIER switches. Once the FIER switches are set, two way communication channels are established between the PEs and the desired MMs (though only one way communication is used for reading). The MMs then each simultaneously transmit their entire contents serially as a stream of intensity modulated light. The optical signals pass through the FIER network, with fan-out as necessary, to the requesting PEs. Fan-out is required to satisfy multiple PE requests of the same MM.

The specific types of hardware selected to implement the SMOEC were chosen with the intention of feasible implementation in the near term. As previously discussed, the hardware is divided into five subsystems: electronic Processing Elements (PEs), electronic Memory Modules (MMs), an optical interconnection network (FIER), an electronic routing control unit (MATSH), and an electronic Control Signal Distribution & Interface (CSDI). Units listed as electronic actually include an electronic/optical interface, and thus must be considered as having a partially hybrid composition. The architecture of this system is shown in Figure 2.2. An overview of the functionality of each of the units is presented in the following sections. Later chapters will examine the theory and design of the major subsystems in greater detail.

#### 2.2 Processing Elements (PEs)

The PEs are intended to be simple electronic processors, such as a basic microprocessor. The complexity of individual PEs is a design parameter for the SMOEC; the architecture permits flexibility in this aspect. Located with each PE is a local memory at least equivalent to the size of a MM.

Each processor must have two types of Input/Output (I/O): electrical and optical. The optical I/O to the PEs is implemented by fiber optic techniques, one transmitter and receiver per PE. Since no addressing or multiplexing of resources (I/O signals) is needed, a common interface bottleneck is avoided. Optical I/O (laser sources and detectors) is used to send data to and receive data from the FIER optical network. The electrical I/O is used to send addresses (and sometimes small amounts of data; see Appendix 6.3) to the MATSH control unit to compute the switch settings for the FIER.

Figure 2.2: SMOEC: Architecture.

#### 2.3 Memory Modules (MMs)

The size of the electronic MMs is somewhat dictated by the architecture. Since the read and write processes operate on the entire MM contents, the MM size must not be too large. However, they must be of sufficient size for useful computation to be practical. MM size has a strong impact on the selection of values for other design parameters (as discussed in Section 7.1.1). The Memory Modules will work best if each is conceived of as a large recirculating shift register, capable of reading and writing data quickly in sequence throughout its entire capacity. A small amount of random-access memory is also included in each MM, to provide locations for fetch-and-add operations (see Appendix 6.3). In the same manner as for PEs, the MMs also have both optical and electronic I/O to the FIER optical network.

Although electronic MMs are envisioned in the near term, optical technologies may provide improved performance in the longer term. Examples include optical disk memory with multiple write heads and parallel optical readout [Lee 88, Psaltis 90], as well as volume holographic media [Lee 88, Li 92, Li 95]. However, in the current design, optical intensity is sent into the FIER optical network after being serially modulated by the electronically-stored information in the MMs.

#### 2.4 Optical Interconnection Network (FIER)

The optical interconnection network, called the Free-space Interconnection with Externally-controlled Routing (FIER), is a novel design based on passive optical switching using polarization-based routing. The FIER optical network features a broadcast/combine capability and employs an external circuit-switched control

system. The topology and theoretical underpinnings of the FIER are elaborated in Chapter 3, and the optical design of the FIER and the combination of optical hardware used to implement it are explained in detail in Chapter 4. The self-contained nature of the FIER means that it may also be used as a component in systems other than the SMOEC.

A fundamental choice in the design of an optical interconnection network is active vs. passive switching. In an active switch, the switch state must be physically set upon the arrival of each data bit. Therefore a switch delay is incurred before the corresponding output data bit is generated. In a passive switch, the switch state is set beforehand by a separate control signal, then data arriving at the switch pass through to the preselected outlet link without any switching delays. Passive switch connections effectively act as if a direct wire from inlet link to outlet link had been installed inside the switch. Passive optical switching was selected for the FIER to permit high speed data throughput in the network. Passive switching also enables circuit-switched (see Section 2.5) control of the network, which permits additional functionality to be incorporated in the control algorithms. However, decreased optical power after each stage in the FIER is a tradeoff that must be considered when implementing a passive network. This limits the number of optical stages that may be cascaded without regeneration of the optical power.

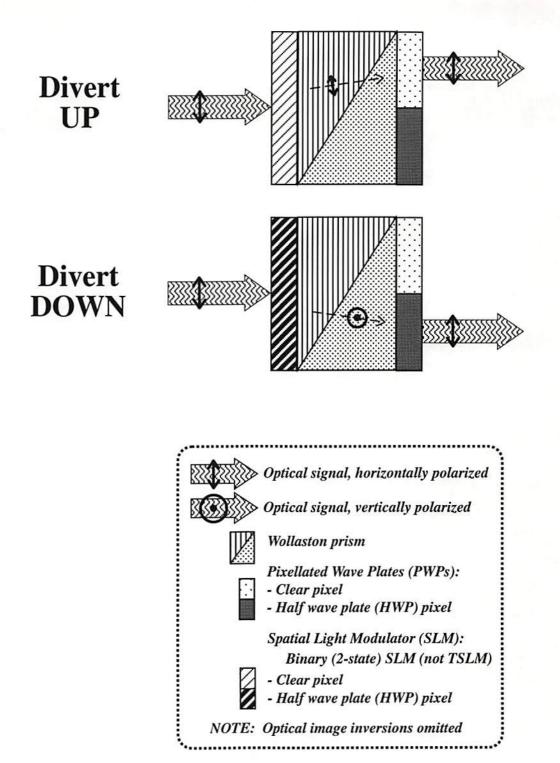

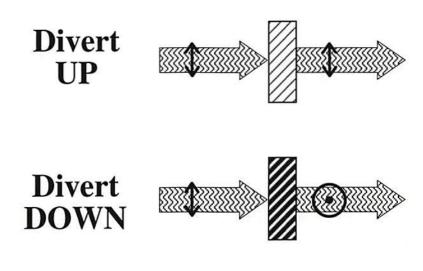

A shuffle-exchange interconnection network topology [Stone 71, Parker 80] was chosen for the FIER since it provides hardware simplicity (ease of optical implementation) while still exhibiting sufficient topological generality. The shuffle-exchange stages are incorporated in an Extended Generalized Shuffle (EGS) network [Richards 91a] which was chosen because of its ability to provide nonblocking

access between the sets of PEs and MMs. The bypass/exchange switches designed for use in the FIER are capable of the usual "bypass" and "exchange" settings, as well as the extended "combine" and "broadcast" settings. The extended switch settings are not often used by other shuffle–exchange network designs. In the FIER, these extended settings are used to allow data to be routed together when appropriate. Because of this enhanced switch capability, write request combining and broadcast of MM contents to multiple requesting PEs may be performed by the FIER.

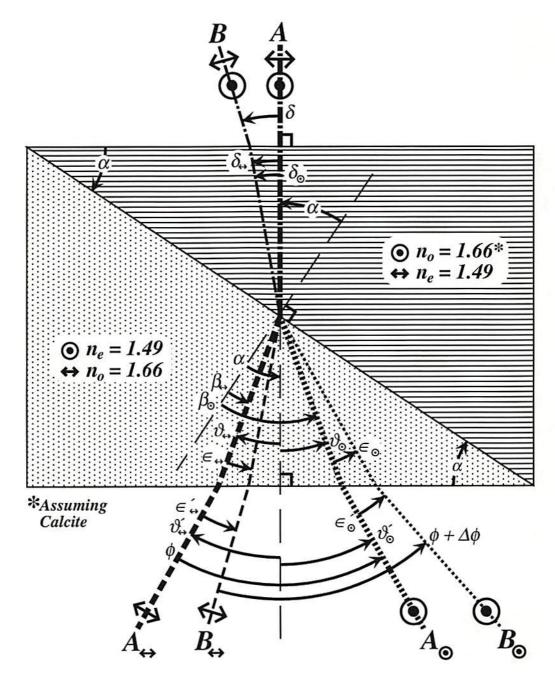

The FIER is implemented using classical free-space optics with cascaded shuffle-exchange stages consisting of polarizing prisms, fixed waveplates, bulk lenses, lenslet arrays, and optically addressed polarization-switching ferroelectric liquid crystal Spatial Light Modulators (SLMs). The write beams to the SLMs carry the control bits to set the SLM pixels (individual optical switches) to individually modify the polarization of individual incoming optical data channels. These SLM write beams are shown as electonic in Figure 2.2, however, they could instead be optical write beams. The read beams (data channels) carrying intensity-modulated data receive a polarization change (or no change) which allows the data channels to be sent in different directions (routed) using polarizing prisms. The CSDI buffering unit sends its control bits either electronically or optically in parallel to the SLMs in the FIER, so that the network is reconfigured by switching all pixels in all the SLMs simultaneously. The optical switch states in the FIER may be maintained by utilizing bistability of some SLM devices, or by using the memory in the CSDI buffering unit to refresh the SLM states.

The interfaces between the optical and electronic signals are designed to be fully parallel (no addressing schemes) to avoid bottlenecks at these conversion points. Optical fibers are used to transfer signals from the FIER to the PEs and MMs, and vice versa. Bundles of optical fibers are used to format the signals into pixel arrays for entry and exit to the FIER. These bundles allow the fibers to be unbundled at their opposite end (connecting to the PEs or MMs) to allow I/O to individually controlled, physically separate devices. In this manner, the PEs (and MMs) may be located on separate electronic component boards, with one or more PEs (or MMs) per board, and with each PE (or MM) having its own laser diode and detector. Thus the data rate through the passive FIER is primarily limited by the speeds of the lasers and detectors. However, noise sources due to the various optical components may be additional limiting factors on the data throughput rate. The actual data rate through the FIER may be treated as a design parameter.

Several elements in the list of desired parallel computer features (Table 2.1) motivate the choice of the optically-implemented FIER over an electronic interconnection network for the SMOEC. The passive nature of the FIER permits high speed PE $\leftrightarrow$ MM throughput. The ability of the FIER to combine and broadcast messages permits physically parallel simultaneous memory reads and writes at these high data rates, which contributes strongly to its utility as the central subsystem (when teamed with the MATSH, described below) of a shared memory architecture. Fine-grained parallelism is facilitated through the use of bulk optics and optical devices with simple replicated structures such as lenslets, and through the reduced complexity (as compared with electronics) due to the three-dimensional nature and superposition principle of optics (optical beams may pass

through each other unaffected). Electronic interconnection networks designed for shared memory machines were not designed with physically parallel data throughput as a goal, nor is their complexity well suited for application to fine-grained parallelism. The SMOEC was designed to incorporate the FIER as an essential element from the very beginning of its design, so that a novel type of shared memory machine with different strengths and improvements based on the advantages of optics would be the result.

# 2.5 Electronic Routing Control Unit (MATSH)

Passive switching elements require control bit computation to be carried out physically separate from data passing through the switches. Non-buffered networks may not store any data within a switching node. Therefore, the FIER is circuit switched. Circuit switching consists of setting a dedicated communication channel between a source and destination pair for the duration of a communication cycle. All switches in a circuit-switched network are set simultaneously. In contrast, in packet switching there is no dedicated channel; switches are individually set (using only local information within the switch) upon the arrival of a data block at each intermediate switching node.

The Multifunctional Arbitrator of Traffic for Shuffle-exchange Hardware (MATSH) was designed to implement circuit switching control for the FIER optical network. It was also designed to perform additional data combining and arbitration functions that the passive optical data paths cannot.

Within the MATSH is an electronic implementation of a single shuffle pattern and an array of bypass/exchange switches, forming a single Electronic Shuffle—Exchange stage (E-SE). This single stage, with the addition of bidirectional feedback connections that connect its outlet and inlet links, can mimic the operation of the FIER optical network. Electronic I/O to this single stage is provided to the PEs, the CSDI buffering unit (and the MMs). (The MATSH  $\leftrightarrow$  MM I/O is used solely for implementing fetch-and-add, as described in Appendix 6.3.) This setup allows the MATSH to mimic the operation of the FIER optical network, albeit at a lower bandwidth, as described in Chapter 5.

The bypass/exchange boxes in the MATSH are required to be capable of performing write request combining and arbitration (as discussed in Section 6.2) in addition to computing control bits for the FIER. Write request combining and arbitration require that each electronic node be capable of performing a "process-and-exchange" function, in which the action performed during the "process" part involves additional computation steps that are dependent on which communication phase is being carried out. Each bypass/exchange switch node in the MATSH therefore incorporates additional logic hardware and some local memory to allow it to perform such operations as data comparisons, data additions, bit cycling, AND, OR, and storage of a limited amount of data. The data storage is provided by a register stack of depth  $\mathcal{O}[\log N]$ .

# 2.6 Control Signal Distribution & Interface (CSDI)

The Control Signal Distribution & Interface (CSDI) is responsible for sending the optical switch settings to the appropriate locations in the FIER optical network at the appointed time. Electronic buffers store the control information until all control signals are present, then it is transmitted simultaneously to the FIER so that the optical devices may all switch at once. Simultaneous setting of all optical switches reduces the amount of delay introduced by the optical array (SLM) switching times (which are relatively slower than electronic switching times).

# Chapter 3

# INTERCONNECTION NETWORK TOPOLOGY AND ROUTING (REVIEW)

The interconnection network employed in the SMOEC is required to be capable of performing arbitrary connection patterns between the inlets and outlets of the network. The connection patterns required by the SMOEC involve many-to-one connections in the PE→MM direction, which perform conversely as one-to-many connections in the MM→PE direction. This chapter elucidates the topology underlying the FIER optical network, and provides its theoretical underpinnings. Although this chapter is primarily a review of relevant work by other research groups, a few new points and results are introduced.

Note on notation: Many interconnection parameters are frequently used both directly and as logarithms. To facilitate the presentation and use of these parameters, this report employs the convention that lowercase parameters are the

logarithm (usually base 2) of the corresponding uppercase parameters. Occasionally uppercase script letters will be used to differentiate related parameters that do not follow this convention.

When discussing interconnection networks it is important to consider their capability to satisfy multiple connection requests. This capability is discussed in terms of the blocking of network connections. This terminology varies somewhat in its usage, so the particular terminology employed herein (adapted from [Hinton 93a]) is summarized below, in order of increasing capability.

- Partial Access Networks have limited function; larger networks are often built from smaller, partially connected network pieces.

- Full Access Networks provide the connectivity such that any inlet can be connected to any outlet. These networks can be blocking. In these networks there is at least one path from any inlet to any outlet.

- Rearrangeably Nonblocking Networks are those in which any idle inlet may be connected to any idle outlet provided that we may rearrange existing connections. They are capable of any permutation of inlets to outlets.

- Wide-Sense Nonblocking Networks have some paths available through the network that may block other connections, but if certain rules are adhered to, the network may operate as if it were strictly nonblocking. For example, crossbar networks may be wide-sense nonblocking (instead of strictly non-blocking) due to the existence of "pathological" paths, which are paths that snake through multiple switching nodes and consequently may block other connections.

Strictly Nonblocking Networks are those in which any idle inlet may be connected to any idle outlet, regardless of how many other connections are already established and regardless of the specific paths used by the other connections.

Redundant Strictly Nonblocking Networks have more than enough elements to be strictly nonblocking; these networks are designed to maintain an acceptable level of connectivity even when elements within the network fail.

# 3.1 Shuffle-Exchange Topology

As previously mentioned, a shuffle–exchange interconnection network topology [Stone 71, Parker 80] was chosen for the FIER optical network since it provides hardware simplicity (ease of optical implementation) while still exhibiting sufficient topological generality. A basic shuffle–exchange network is a multistage cascadable network, where each stage consists of a "perfect shuffle" followed by an array of bypass/exchange switches. More general shuffle–exchange networks may be composed of  $a \times b$  switching nodes interconnected by a generalized version of the perfect shuffle, called a Q-shuffle. The resulting "shuffle–exchange" stage is a building block for several types of networks. The parts of shuffle–exchange networks are detailed below.

# 3.1.1 The Perfect Shuffle

The perfect shuffle is named after the common riffle shuffle used when playing cards in which a deck of cards is divided in half and combined by interleaving cards from each deck half. A "perfect" shuffle is therefore one in which the deck is first divided precisely in half, and then single cards are exactly interleaved. Examination of this process on a linear array of nodes with binary indices (see Figure 3.1) reveals that information is sent to the node whose index is the left cyclic shift of the source node. That is, given  $N = 2^n$  inlet nodes, if the index of an inlet node i is represented as a sequence of n binary digits (bits)  $b_j$ , as:

$$i = (b_{n-1} \ b_{n-2} \ \cdots \ b_1 \ b_0), \qquad 0 \le i \le N-1$$

(3.1)

where

$$i = \sum_{j=0}^{n-1} b_j 2^j$$

, with  $b_j \in \{0, 1\}$ , (3.2)

then the perfect shuffle performs the operation  $SH_N(i)$ , where:

$$SH_N(i) = (b_{n-2} \cdots b_1 b_0 b_{n-1}) \tag{3.3}$$

$$= LEFT-CYCLICAL-SHIFT(i)$$

(3.4)

# 3.1.2 Q-Shuffles