## **USC-SIPI REPORT #357**

Optoelectronic-VLSI System Integration For Digital Information Processing

by

**Sunkwang Hong**

December 2002

Signal and Image Processing Institute UNIVERSITY OF SOUTHERN CALIFORNIA

Department of Electrical Engineering-Systems 3740 McClintock Avenue, Room 400 Los Angeles, CA 90089-2564 U.S.A.

## **Dedication**

To my parents

## Acknowledgements

I am deeply thankful to my advisor, Prof. Alexander A. Sawchuk, for his advice, guidance, encouragement, and financial support throughout my years at USC. He has always guided me with understanding, patience, and insight. I have truly enjoyed working with him.

I also like to thank Prof. Robert W. Hellwarth for valuable discussions and ideas during my research. I was very lucky to be working for him during my first year at USC. Since then he has always encouraged me with inspiration. I also would like to thank my dissertation committee members, Prof. William Steier and Prof. Stephan Hass, for their constructive suggestions and comments.

Special thanks goes out to Dr. Charlie Kuznia for his help on Transpar and UTSi projects. I would also like to thank people in our research group: Dr. Eddie Pansatiankul, Hyukjune Chung, Changki Min, Barge Intharasombat, Zahir Alpaslan, and David Ho. I have enjoyed working with them and sharing many valuable ideas, discussions, and friendship.

I am in debt to many people during this work. I like to thank Prof. Alan Willner and his student Asaf Sahin for their help on high-speed testing, Matthew Frank of Schott Optovance for fiber image guides samples, Matthew Robinson of RSoft for BeamPROP simulation, Yue Liu of Honeywell for VCSEL/MSM chips, and the people at Q-Tech for their help on wirebonding.

I would also like to thank Dr. Allan G. Weber and Seth Scafani for their help on computer and network support. I also like to thank Toy Mayeda for his invaluable help on electronics. I also thank Gloria Halfacre, Gerrielyn Ramos, Regina Morton, Linda Varilla, and Ramona Gordon for their tremendous administrative help.

Finally, I am deeply grateful to my parents, Seong Ahn Hong, and Jung Hyun Kang for their love and encouragement. My sisters, Kum-Hee Hong, Sun-Hee Hong, and my brother, Deog-Ki Hong also have been great supports with love in my life.

## Contents

| Dedication                                                               | i    |

|--------------------------------------------------------------------------|------|

| Acknowledgements                                                         | ii   |

| List of Tables                                                           | vii  |

| List of Figures                                                          | ix   |

| Abbreviations                                                            | xii  |

| Abstract                                                                 | xvi  |

| Chapter 1 Introduction                                                   |      |

| 1.1 Motivation and Objective                                             |      |

| 1.2 Contributions of the Research                                        |      |

| 1.3 Organization of the Dissertation                                     |      |

| Chapter 2 Optical Interconnects for Electronic Systems                   | 9    |

| 2.1 Advantages of Optical Interconnects over Electrical Interconnects    |      |

| 2.2 Optical Interconnects to Silicon CMOS: Design Issues                 |      |

| 2.2.1 Strategy                                                           | 14   |

| 2.2.2 Component Requirements and Design                                  | 16   |

| Chapter 3 A Modular Testbed for Optical Interconnects                    | 20   |

| 3.1 Transpar                                                             | 20   |

| 3.2 Transpar-Token-Ring Network                                          | 23   |

| Chapter 4 Transpar Modular System Components and Experimental Setu       | ıp30 |

| 4.1 Printed Circuit Board (PCB)                                          |      |

| 4.2 VCSEL and MSM Detector Array                                         | 32   |

| 4.3 VCSEL Measurements                                                   | 35   |

| 4.4 Transimpedance Amplifier (TIA) Receivers                             | 36   |

| 4.5 Field Programmable Gate Array (FPGA)                                 |      |

| 4.6 Power Setup                                                          |      |

| Chapter 5 Free Space Optical Interconnection Systems                     | 41   |

| 5.1 Introduction                                                         | 41   |

| 5.2 Free Space Optical interconnection Experiment Setup: Refractive Lens |      |

| 5.3 Optical Alignments                                               | 45  |

|----------------------------------------------------------------------|-----|

| 5.4 Test Results                                                     | 46  |

| 5.5 Diffractive Optical Elements (DOEs)                              | 47  |

| Chapter 6 Fiber Image Guides (FIGs)                                  | 54  |

| 6.1 FIGs.                                                            |     |

| 6.2 FIGs Experiments                                                 |     |

| 6.3 VCSEL Output Uniformity                                          |     |

| 6.4 Test Results.                                                    |     |

| 6.5 Interconnect Performance                                         |     |

| Chapter 7 FIG Modeling and Simulation                                | 67  |

| 7.1 Introduction.                                                    |     |

| 7.2 Simulation Limitations                                           | 68  |

| 7.3 Simulation Setup                                                 | 69  |

| 7.3.1 Fiber Array                                                    | 69  |

| 7.3.2 Calculation Parameters                                         | 70  |

| 7.3.3 Launching Laser                                                |     |

| 7.4 Results and Discussions                                          |     |

| 7.4.1 Waveguides in Fiber Arrays                                     |     |

| 7.4.2 Launch at Center of Fiber Core                                 |     |

| 7.4.3 Launch at Center of Background                                 |     |

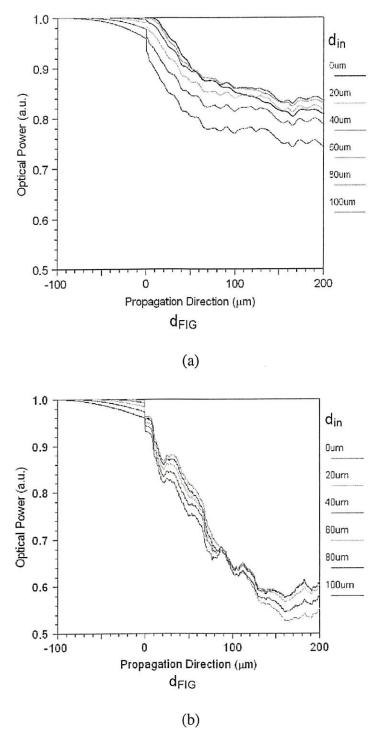

| 7.4.4 Optical Output Power                                           | 78  |

| Chapter 8 An Integrated Approach for Optical Interconnects: UTSi     | 85  |

| 8.1 Integration of Optical Interconnects to Silicon                  |     |

| 8.2 Flip-Chip Bonding Technology                                     |     |

| 8.3 Silicon-on Insulator (SOI)                                       | 88  |

| 8.4 Ultra-Thin Silicon-on-Sapphire (UTSi) Technology                 |     |

| 8.4.1 Sapphire (Al <sub>2</sub> O <sub>3</sub> ) Physical Properties |     |

| 8.4.2 UTSi Advantages                                                |     |

| 8.5 Optoelectronic Integration on UTSi                               | 93  |

| Chapter 9 System Design and Testing of UTSi CMOS                     | 96  |

| 9.1 UTSi CMOS System Design                                          |     |

| 9.2 UTSi 2000 Chip #1                                                |     |

| 9.2.1 Testing of UTSi 2000 Chip #1                                   |     |

| 9.3 UTSi 2000 Chip #2                                                |     |

| 9.3.1 Testing of UTSi 2000 Chip #2                                   |     |

| 9.4 UTSi 2001 Chip #1                                                | 106 |

| 9.4.1 Testing of UTSI 2001 Chip #1                                   |     |

| 9.5 UTSi 2001 Chip #2                                                | 112 |

| 7. J. LENUIS OF UTOLEUUT CHID #4                                     |     |

| Chapter 10 Conclusions and Future Work  | 117 |

|-----------------------------------------|-----|

| 10.1 Summary                            | 117 |

| 10.4 Future Work                        | 119 |

| References                              | 122 |

| Appendix: Beam Propagation Method (BPM) | 129 |

#### Abstract

Optoelectronic-VLSI systems can provide high-bandwidth multimedia applications and real-time parallel processing using the complementary properties of electronics and optics. Optics has many advantages in high-speed data transfer including inherent low crosstalk and low power, while electronics is more suitable for logic functions and integrated circuitry. In this research, we present designs and demonstrations of optoelectronic-VLSI systems based on two different approaches: a modular integration, and a monolithic integration. Both approaches deal with the optimal integration of optoelectronic devices for high-speed, high-throughput network communications and data processing.

We have designed and tested a modular optoelectronic-VLSI system called Translucent Smart Pixel Array (Transpar). The system includes a field-programmable gate array (FPGA), a transimpedance amplifier (TIA) receiver, and an interlaced array of 4 × 4 vertical-cavity surface-emitting lasers (VCSELs) and metal-semiconductor-metal (MSM) detectors. The FPGA allows for reconfigurable networks and processors, thus Transpar can implement dynamic novel network protocols. The components are mounted on a printed circuit board (PCB) for testing of various optical interconnection techniques. Bulk lenses, diffractive optical elements (DOEs) and fiber image guides (FIGs) were tested and compared as interconnection techniques for the Transpar system. A detailed wave-propagation simulation for the FIGs is presented and compared with

experimental results. The effect of optical crosstalk and minimization of the overall power dissipation are also considered.

One technique for the monolithic integration of mixed-signal integrated circuits with optoelectronics is Ultra-thin Silicon-on-Sapphire (UTSi) technology. UTSI has low parasitic capacitance and enables different optical and electrical components to be integrated with ordinary complementary metal-oxide semiconductor (CMOS) circuits using standard fabrication processes. It is well suited for low-cost and high-performance optical data communication systems. The sapphire substrate of UTSi is highly transparent to the propagation of light from VCSELs and simplifies the packaging. We have designed and tested four different UTSi chips for evaluation and testing of integration of optoelectronic components. These chips contain VCSEL drivers, receiver circuitry, clock generators, frequency dividers, and voltage controlled oscillators. Flipchip bonding is used to combine VCSEL and detector arrays with the UTSi CMOS circuits. The architecture and system performance of each chip is tested and discussed.

## **List of Tables**

| Table 2-1 | Comparisons of data communications and telecommunications10 |

|-----------|-------------------------------------------------------------|

| Table 4-1 | Honeywell VCSEL/MSM characteristics                         |

| Table 4-2 | Power setup for the Transpar system40                       |

| Table 6-1 | Characteristics of Schott FIGs                              |

| Table 7-1 | FIGs simulation parameters69                                |

| Table 7-2 | Calculation parameters71                                    |

| Table 9-1 | Summary of 2000 and 2001 UTSi chips97                       |

| Table 9-2 | Emcore 1 × 4 PIN array properties                           |

| Table 9-3 | Emcore 1 × 4 VCSEL array properties                         |

# List of Figures

| Figure 1-1                      | Optical interconnection hierarchy as a function of distance                                                                                                                                                                                                                                                   |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| chip clock rate<br>(b) delay of | Copper interconnection with 1 $\mu$ m $\times$ 1 $\mu$ m cross-section as a function of on length [47]. LC and RC lines are with 1 $\mu$ m unrepeatered lines. One is 3.5 GHz for 0.1 $\mu$ m technology. (a) Bandwidth of copper interconnect copper interconnect, the line labeled C for the case of optics |

| Figure 2-2. the actual cross    | A comparison of typical optical and electrical communication energies sover point is system dependent [44]                                                                                                                                                                                                    |

| Figure 2-2.                     | Two most common photodetector types                                                                                                                                                                                                                                                                           |

| Figure 3-1. right between       | Two Transpar nodes and free-space optical packets flowing from left to them                                                                                                                                                                                                                                   |

| Figure 3-2.                     | Transpar token-ring network                                                                                                                                                                                                                                                                                   |

| Figure 3-3.                     | Block diagram of Transpar TR logic functions                                                                                                                                                                                                                                                                  |

| Figure 3-4.                     | Two Transpar packet communications                                                                                                                                                                                                                                                                            |

| Figure 4-1.                     | Transpar PCB31                                                                                                                                                                                                                                                                                                |

| Figure 4-2.                     | Cross-sectional view of Honeywell VCSEL/MSM chip34                                                                                                                                                                                                                                                            |

| Figure 4-3.                     | 4 × 4 array of Honeywell VCSEL/MSM photodetector array34                                                                                                                                                                                                                                                      |

| Figure 4-4.                     | Honeywell VCSEL output power performance [69]36                                                                                                                                                                                                                                                               |

| Figure 4-5.                     | Block diagram of the TIA used in our experiments                                                                                                                                                                                                                                                              |

| Figure 4-6.                     | FPGA operation voltage and its current output                                                                                                                                                                                                                                                                 |

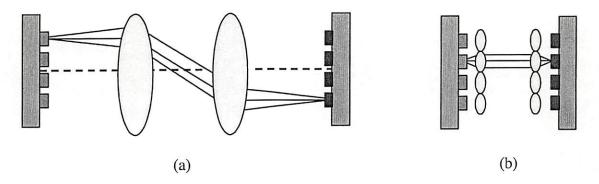

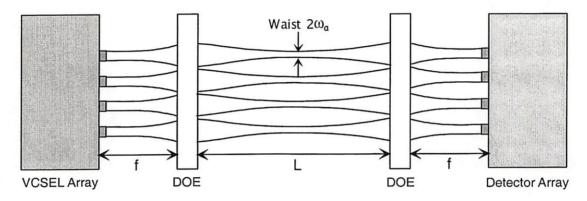

| Figure 5-1                      | Free-space optical interconnection using (a) macrolens, (b) DOEs42                                                                                                                                                                                                                                            |

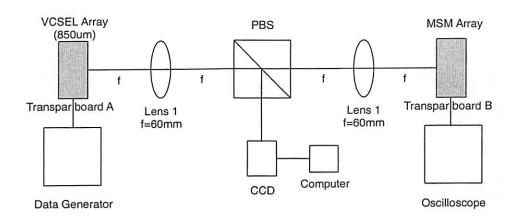

| Figure 5-2.                     | Setup for free space interconnection using bulk lenses44                                                                                                                                                                                                                                                      |

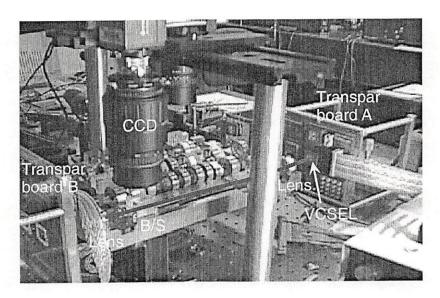

| Figure 5-3.               | Picture of free-space optical interconnection experiment setup44                                                                                         |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

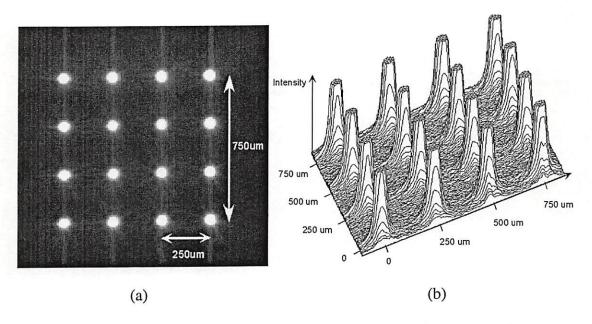

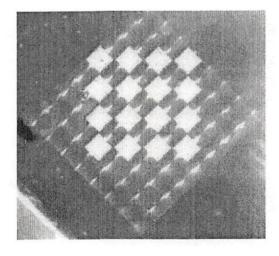

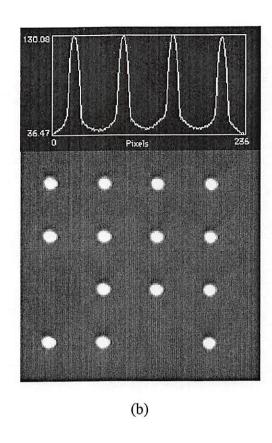

| Figure 5-4. profile       | 4 × 4 VCSEL output power uniformity. (a) CCD output, (b) the output                                                                                      |

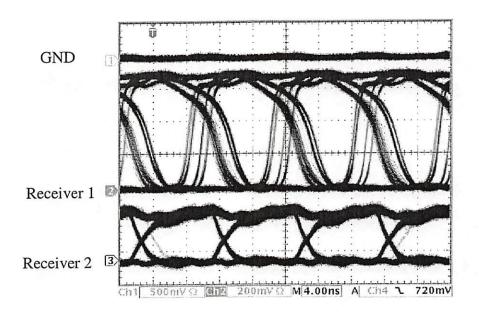

| Figure 5-5.               | Eye diagrams at 100 Mbps47                                                                                                                               |

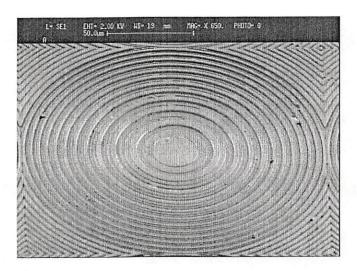

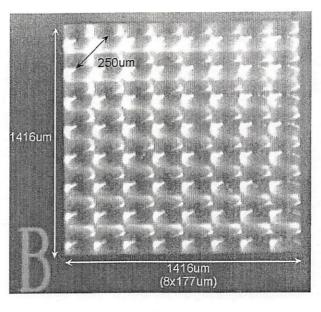

| Figure 5-6.               | DOE. (a) SEM picture of type A DOE. (b) $8 \times 8$ array of type B DOE48                                                                               |

| Figure 5-7.               | Interconnection setup using DOEs50                                                                                                                       |

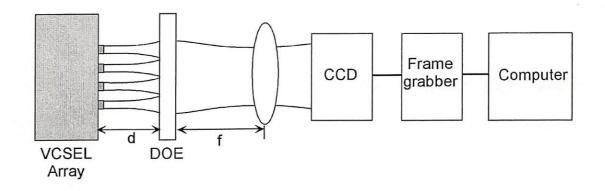

|                           | DOE and VCSEL alignment. (a) The VCSEL beams after passing OEs. (b) Collimated VCSEL beam and the intensity profile for the first CSEL array             |

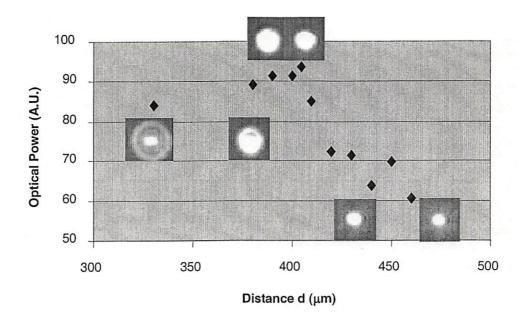

| Figure 5-9.               | Experimental Setup for Fig. 5-1053                                                                                                                       |

| Figure 5-10.              | Power and VCSEL changes along z-direction53                                                                                                              |

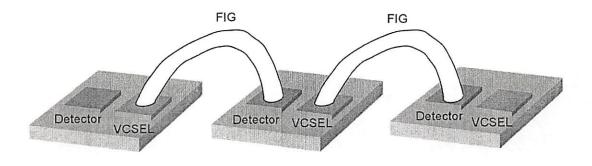

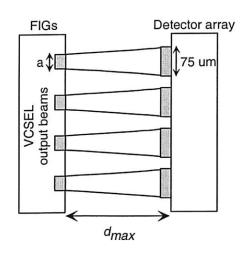

| Figure 6-1.               | FIG interconnects                                                                                                                                        |

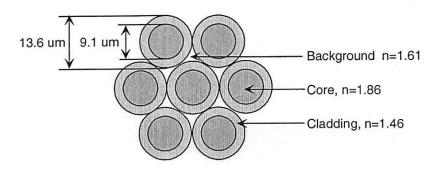

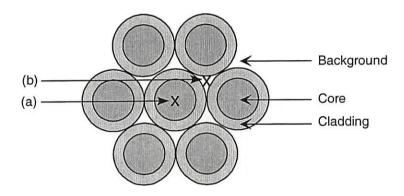

| Figure 6-2.               | FIGs structure55                                                                                                                                         |

| Figure 6-3.               | FIGs56                                                                                                                                                   |

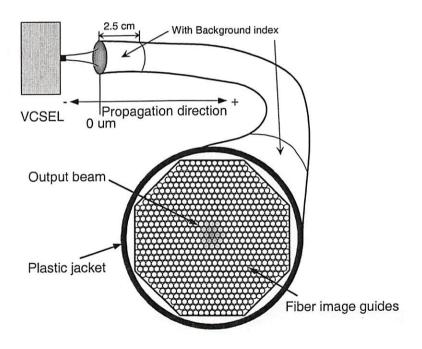

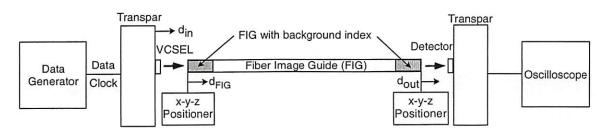

| Figure 6-4.               | FIGs experimental setup                                                                                                                                  |

| Figure 6-5.               | Picture of FIGs setup on Transpar59                                                                                                                      |

| Figure 6-6.               | FIG output image of Honeywell VCSEL-MSM chip60                                                                                                           |

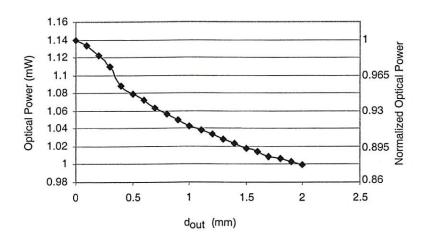

| Figure 6-7.               | Optical power output through 0.3 m FIGs at various $d_{out}$ for $d_{in} = 0$ 60                                                                         |

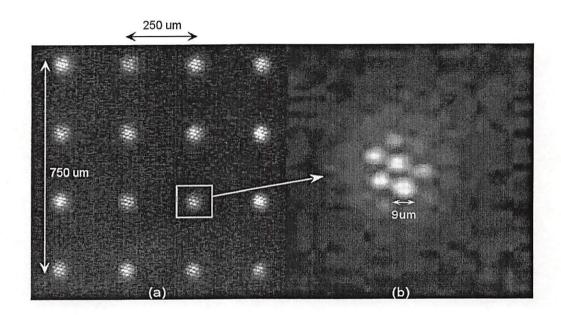

| Figure 6-8. close-up imag | (a) 4 x 4 VCSEL guided image output of 0.3 m FIGs for $d_{in} = 0$ , (b) a e of one of the VCSELs                                                        |

| Figure 6-9.               | The maximum distance between FIGs and detectors62                                                                                                        |

|                           | Launch positions (a) core center position, (b) background center63                                                                                       |

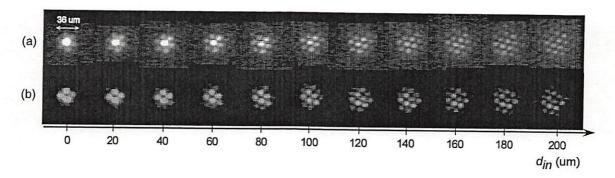

| position (a) co           | VCSEL output as a function of different $d_{in}$ . The top row is for launch ore, and the bottom row is for launch position (b) background center launch |

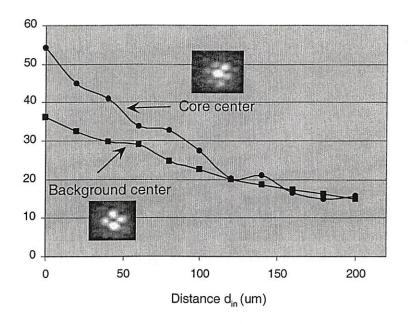

| Figure 6-12. $d_{in}$                      |                  |                       |            |                       |                       |                      |         |           |        |      |

|--------------------------------------------|------------------|-----------------------|------------|-----------------------|-----------------------|----------------------|---------|-----------|--------|------|

|                                            |                  |                       |            |                       |                       |                      |         |           |        |      |

| Figure 6-13. Mbps                          |                  |                       |            |                       |                       |                      |         |           |        |      |

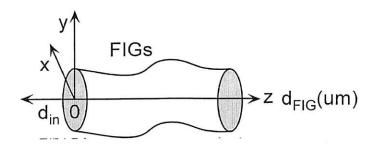

| Figure 7-1.                                | x, y, z          | directions is         | n FIG sim  | nulation              |                       |                      |         |           |        | 71   |

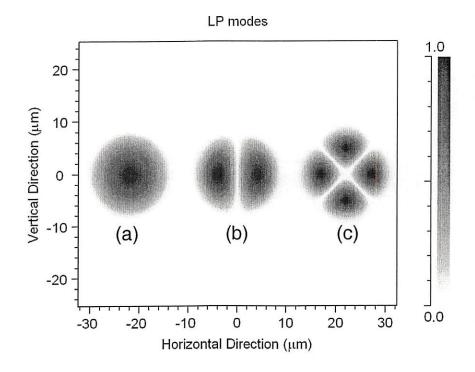

| Figure 7-2.                                | Differ           | ent laser mo          | odes (a) L | $P_{01}$ , (b) $LP_1$ | <sub>11</sub> , (c) I | $\mathbb{L}P_{21}$ . |         |           |        | 73   |

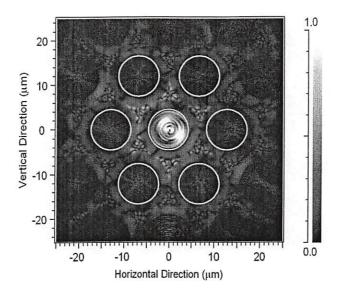

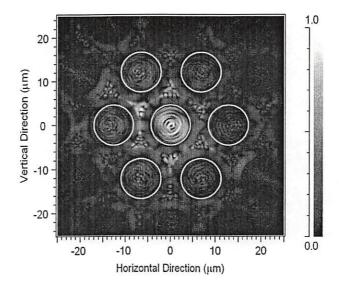

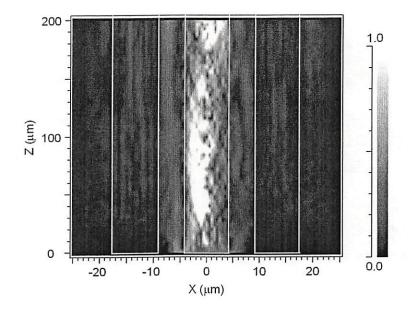

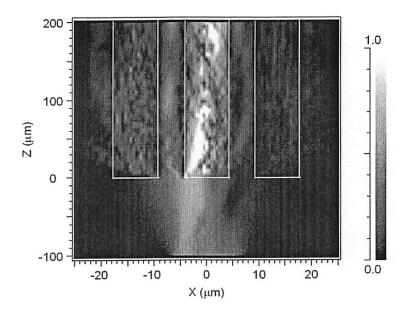

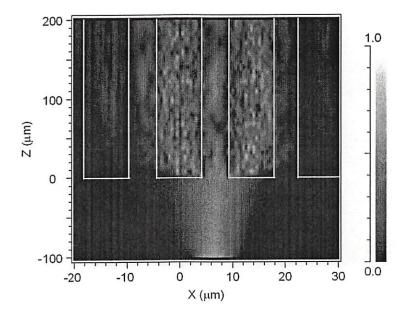

| Figure 7-3. with (a) $d_{FIG}$ = 0 $\mu$ r | = 0 μm           | , (b) $d_{FIG} =$     | 200 μm;    | launched a            | t the c               | enter                | of the  | backgro   | ound ' | with |

| Figure 7-4.<br>the center of c             |                  |                       |            |                       | _                     |                      |         |           |        |      |

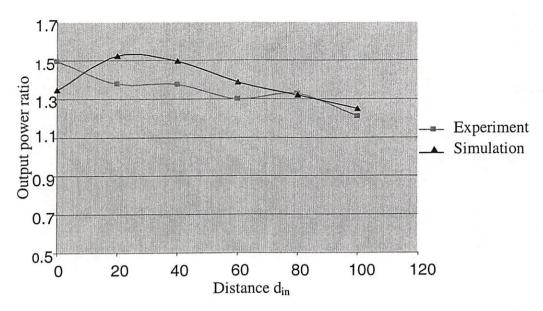

| Figure 7-5.                                | Optica           | al power cor          | nparison   | of experime           | ent and               | l sim                | ulation | along d   | in···· | 81   |

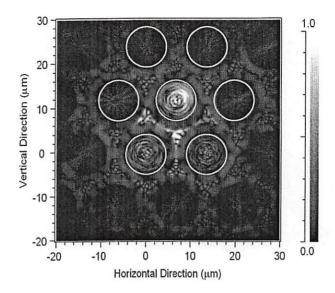

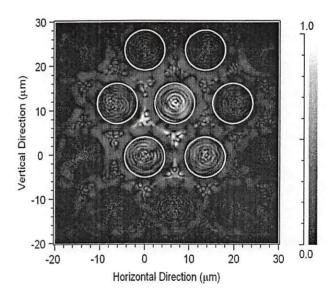

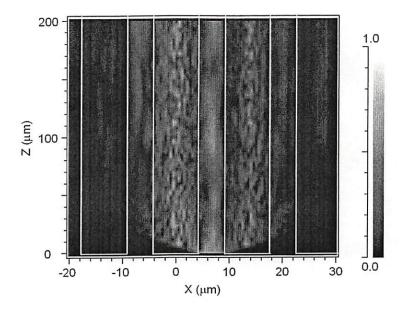

| Figure 7-6. core with (a) $d_{in} = 0$     | $d_{in} = 0 \mu$ | $u$ m, (b) $d_{in}$ = | = 200 μm;  | laser launc           | ched at               | the o                | center  | of the ba | ckgro  | ound |

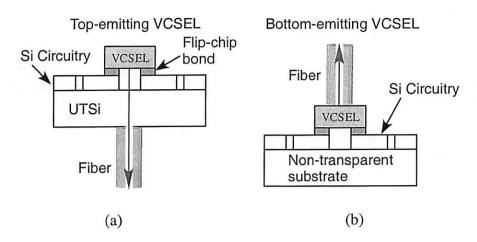

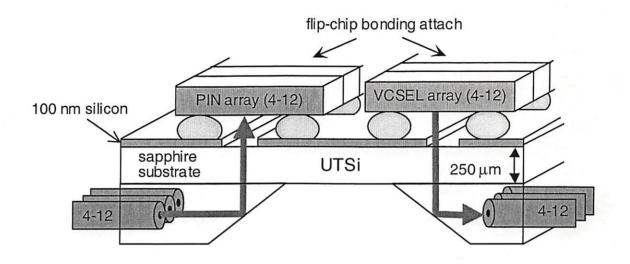

| Figure 8-1.<br>UTSi, (b) Bot               |                  |                       |            |                       |                       |                      |         |           |        |      |

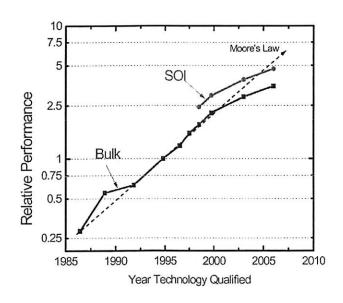

| Figure 8-2.                                | Benef            | its of SOI in         | Moore's    | law [22]              |                       |                      |         |           |        | .88  |

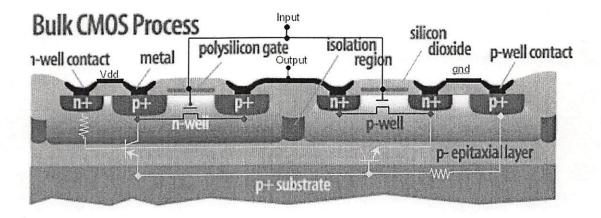

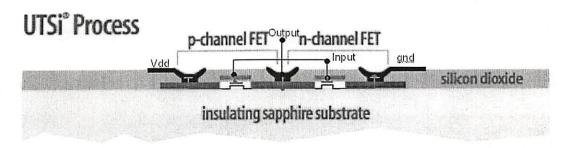

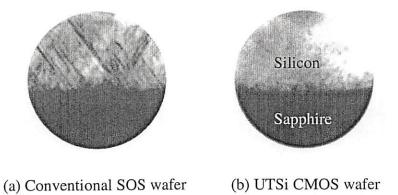

| Figure 8-3.                                | Cross-           | -section of b         | ulk CMC    | S and UTS             | i proce               | ess                  |         |           |        | 90   |

| Figure 8-4.                                | Cross            | sectional vi          | ew of war  | fers [33]             |                       |                      |         |           |        | 90   |

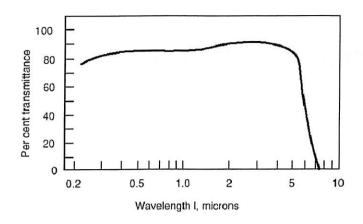

| Figure 8-5.                                | Transı           | mittance dat          | a of 1 cm  | thickness s           | sapphir               | e [2]                |         |           |        | .92  |

| Figure 8-6. substrate                      |                  | hip bonded            |            |                       | -                     |                      |         |           |        |      |

| Figure 8-7.                                | Flip-c           | hip bonded            | UTSi       |                       |                       | • • • • • •          |         |           |        | .95  |

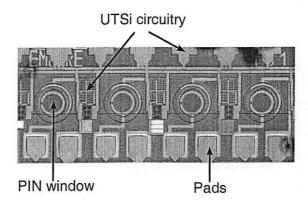

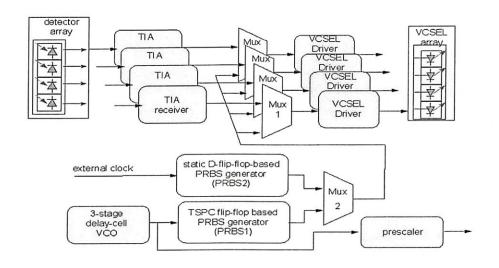

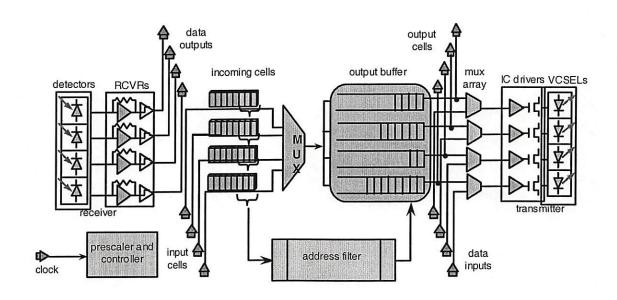

| Figure 9-1.                                | Block            | diagram of            | UTSi 200   | 00 chip #1            |                       |                      |         |           |        | 99   |

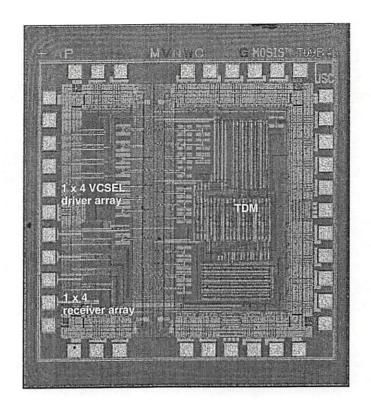

| Figure 9-2.                                | Pictur           | e of UTSi 2           | 000 chip   | #1                    |                       |                      |         |           |        | 99   |

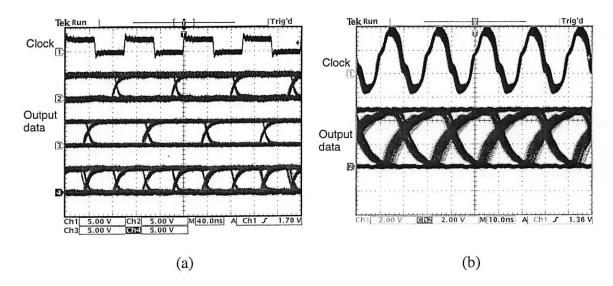

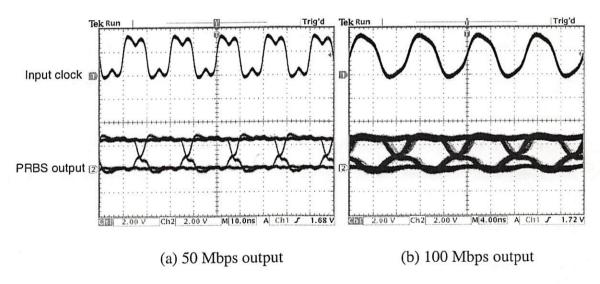

| Figure 9-3.                 | PRBS outputs of UTSi 2000 chip #1100                                           |

|-----------------------------|--------------------------------------------------------------------------------|

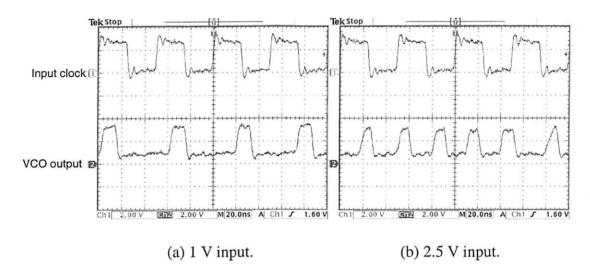

| Figure 9-4.                 | VCO outputs of UTSi 2000 chip #1 with 40 Mbps inputs101                        |

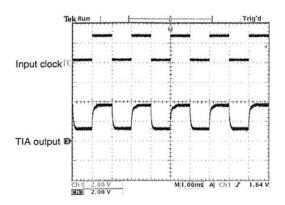

| Figure 9-5.                 | TIA receiver output of UTSi 2000 chip #1 with 1 Kbps input101                  |

| Figure 9-6.                 | Block diagram of UTSi 2000 chip #2                                             |

| Figure 9-7.                 | Picture of UTSi 2000 chip #2                                                   |

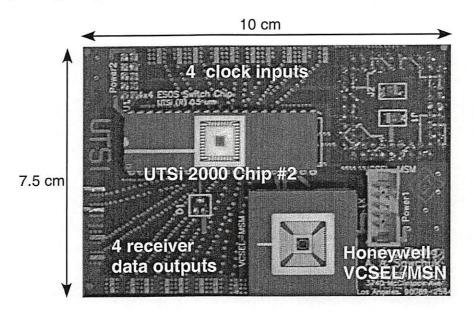

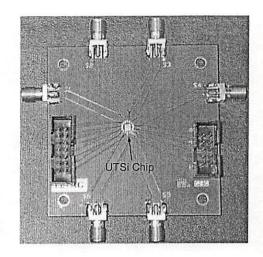

| Figure 9-8.                 | UTSi 2000 chip # 2 and Honeywell VCSEL array mounted on a PCB.105              |

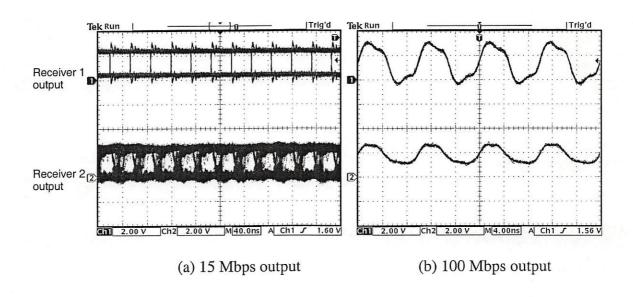

| Figure 9-9.                 | UTSi 2000 #2 chip receiver outputs                                             |

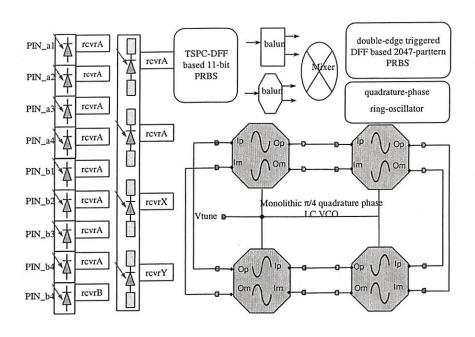

| Figure 9-10.                | Block diagram of UTSi 2001 chip #1                                             |

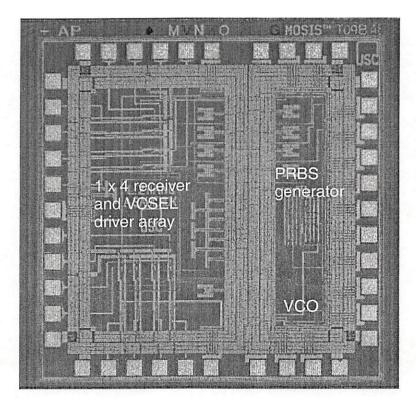

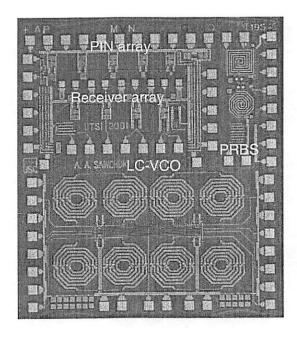

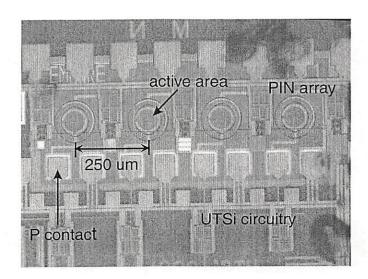

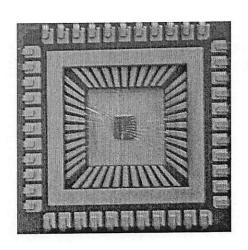

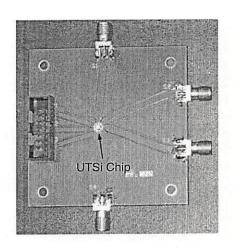

| Figure 9-11.                | Picture of UTSi 2001 chip #1                                                   |

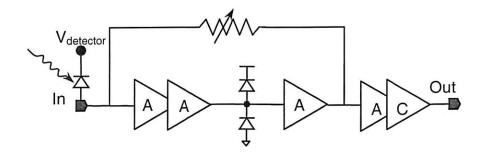

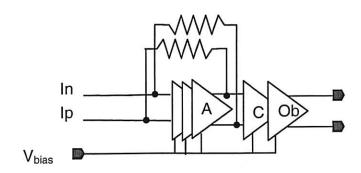

| Figure 9-12. resistance fee | Receiver A: a novel single-ended optical receiver with 2nd-order tunable dback |

| Figure 9-13.                | Receiver X and Y: an optical receiver design with LVDS outputs108              |

| Figure 9-14.                | Flip-chip bonded PIN array on UTSi 2001 chip #1110                             |

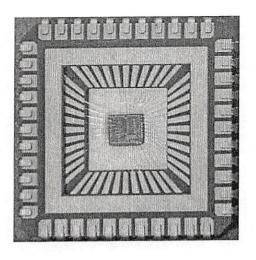

| Figure 9-15.                | UTSi 2001 #1 chip in different packages111                                     |

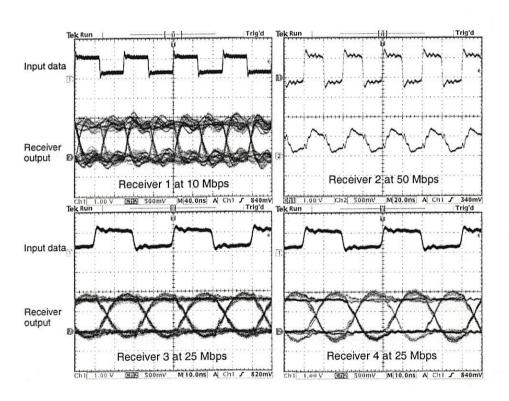

| Figure 9-16.                | The four different receiver outputs of UTSi 2001 chip #1                       |

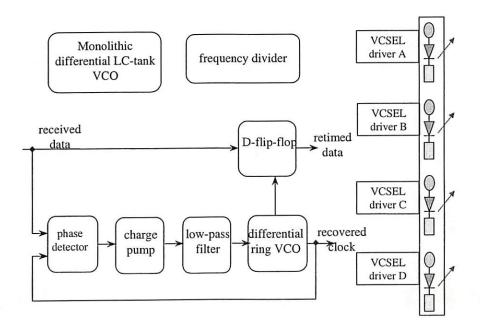

| Figure 9-17.                | Block diagram of UTSi 2001 chip #2112                                          |

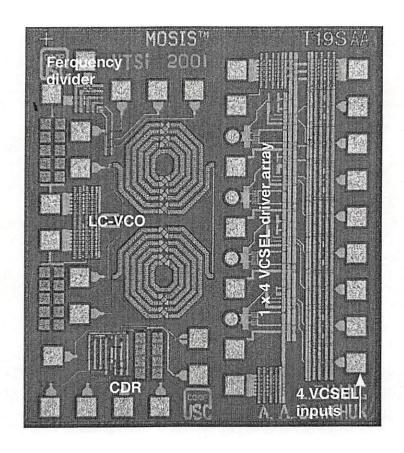

| Figure 9-18.                | Picture of UTSi 2001 chip #2113                                                |

| Figure 9-19.                | Flip-chip bonded VCSEL array on UTSi 2001 chip #2115                           |

| Figure 9-20.                | UTSi 2001 chip #2 packages                                                     |

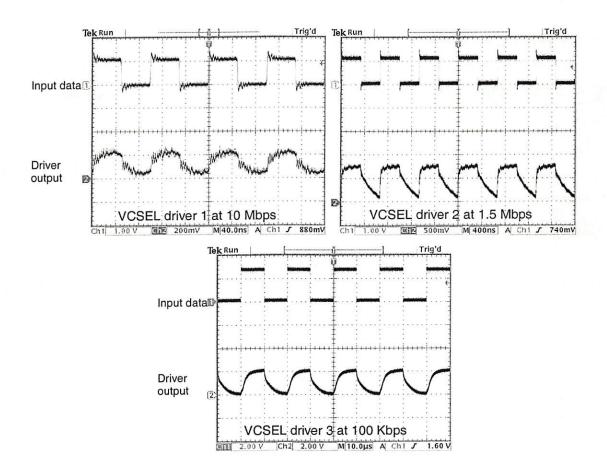

| Figure 9-21.                | Three different VCSEL driver outputs of UTSi 2001 chip #2116                   |

## **Abbreviations**

ASG acid-soluble glass

BPM beam propagation method

CSMA/CD carrier-sense multiple access/collision detection

CDR clock/data recovery

CMOS complimentary metal-oxide-semiconductor

COOP Consortium for Optical and Optoelectronic Technologies in Computing

CTE coefficient of thermal expansion

DAQ data acquisition

DOEs diffractive optical elements

DFF double flip-flop

EDA electronic design automation

EEPROM electrically erasable programmable read-only memory

ESD electrostatic discharge

FIGs fiber image guides

FPGA field-programmable gate array

HDTV high definition television

ISI intersymbol interference

JOP Joint Optoelectronics Project

LSB least significant bit

LED light-emitting diode

LANs local area networks

LNA low noise amplifier

LSB least significant bit

LVDS low-voltage differential signals

MCMs multichip modules

MIM metal-insulator-metal

MSM metal-semiconductor-metal

MMICs monolithic microwave integrated circuits

OIF Optical Internetworking Forum

OPDPs optical parallel data packets

PLL phase-locked loop

PD photodetector

PBS polarizing beam splitter

PE processing-element

PRBS pseudo-random bit steam

PCB printed circuit board

SEEDs self-electrooptic effect devices

SOC system-on-chip

SOI silicon-on-insulator

TBC transparent boundary conditions

TDM time-division multiplexing

TIA transimpedance amplifier

Transpar Translucent Smart Pixel Array

TR token ring

TSPC true single-phase clock

UTSi Ultra-Thin Silicon-on-Sapphire

VCSELs vertical-cavity surface-emitting lasers

VLSI very large scale integration

VSR very short reach

VR virtual reality

VCO voltage-controlled oscillator

WDM wavelength division multiplexing

## Chapter 1

## Introduction

#### 1.1 Motivation and Objective

The demands for high bandwidth and high-speed data processing are always increasing in modern information society. During the last decades, processor clock speeds have increased according to Moore's law [23] and the bandwidth of long haul communication systems have exploded with the advent of fiber optics. Recent multimedia applications such as high definition television (HDTV), virtual reality (VR), real-time image/video processing, and media immersion require more intensive signal processing and bandwidth [43]. For these reasons we expect that the need for more bandwidth and faster data processing will continue in the future.

In high-bandwidth telecommunications, optics has been extensively used and is increasing its role in networks over shorter distances, such as 10 km or less [55]. Optical interconnections in local area networks (LANs) that interconnect routers and other transport equipment are now being developed using links at over 10 Gbps using multiple parallel fiber optic channels [7]. Recently the Optical Internetworking Forum (OIF) has announced the use of  $1 \times 4$  parallel optical transceiver for very short reach (VSR) intra-office interface [50]. This enables the use of optical interconnects down to the range of 2 m communication distance.

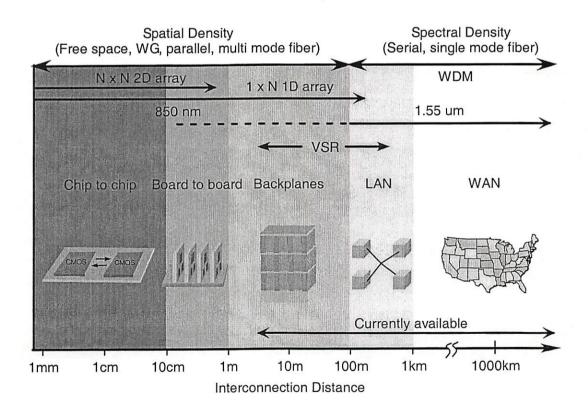

Figure 1-1 summarizes the possible use of optical interconnects for various distance scales. In long distance optical communication systems the information is carried by single-mode fibers using 1.55 μm wavelength. Expanding the spectral bandwidth using wavelength division multiplexing (WDM) increases the capacity enormously. Short distance optical interconnects, such as chip-to-chip, board-to-board, and backplane interconnections are based on waveguides on a substrate, free-space, or multi-mode fiber arrays with 850 nm laser sources [51], [53]. The information bandwidth can be expanded by increasing the number of spatial channels in two-dimension (2D) or one-dimension (1D).

Figure 1-1. Optical interconnection hierarchy as a function of distance.

Despite the success in long-haul communications and its emergence in LANs and VSR, optical interconnects in short-range communications are not well developed. The use of optics in short distance is quite different from long distance telecommunication systems from device and module fabrication to system integration and packaging [66]. In short distance data communication the optical input/output (I/O) has to be directly connected to silicon based electronic chips and this is still a challenge [31], [39], [45]. However, we need to push the limits of optical interconnects to short-range distances because the scaling limit of copper-based electrical interconnects soon will be reached [23].

Electronics has had a key role in digital logic, integrated circuitry, switching and storing data. Also, cost-effective complimentary metal-oxide-semiconductor (CMOS) processing will be a driving force for electronics in future digital information systems [24]. Many argue that Moore's law will soon face its limit in system performance and that performance improvements will likely come from new architectures, new materials, and new technologies. One limit is the I/O bottleneck. The bandwidth of electrical interconnections between chips or boards limits future information capacity. One solution is replacing electrical interconnections with optical interconnections that have attractive advantages for transmitting high-density 2D or 1D array data at low power, low crosstalk, and low latency. Moreover the recent development of vertical-cavity surface-emitting lasers (VCSELs) arrays has increased the flexibility of optical I/O arrays by providing optical sources with relatively low power consumption, high data rates, and the possibility of integration with electronics [37], [38].

Integrating optics to electronic systems faces many technical challenges. The key challenge is the introduction of optical devices based on III-V materials to silicon-based very large scale integration (VLSI) electronics. In addition high-energy photons are not efficiently converted to low-energy electrons. The idea of optical interconnects to VLSI electronics was first proposed by Goodman, *et al* in 1984 [10]. Since then many groups have been trying to integrate optics to VLSI using various methods, such as quantum-well devices [30], or VCSEL arrays [52], but cost effective solutions have not been found yet.

The goal of this research is the development of a new optoelectronic-VLSI technology for integrating optical interconnects to VLSI CMOS to relieve the interconnection bottleneck by optimizing the complementary properties of electronics and optics. In this technology 2D or 1D optics is used to transfer information to and from arrays of optoelectronic units with electrical processing between the optical I/Os.

#### 1.2 Contributions of the Research

In this research we describe optoelectronic interconnections for two different types of optoelectronic-VLSI systems. The first is a modular system called Translucent Smart Pixel Array (Transpar) [4], [34]. Transpar is an optoelectronic system that can perform high efficiency parallel data processing through smart pixel arrays on 2D data structures such as images and video. In this modular system, the optical and electrical components are individually tested and combined to optimize the system performance. The other

approach uses electrical components monolithically integrated on CMOS circuitry with optical I/O arrays that are flip-chip bonded to the CMOS. For the monolithic integration of the digital and analog circuitry we used a silicon-on-insulator (SOI) technology called Ultra-Thin Silicon-on-Sapphire (UTSi) that has been developed by Peregrine Semiconductor Corp. [2], [33]. This process is being developed to meet the cost and performance requirements of future integrated system-on-chip (SOC) solutions for high performance communication systems. We also investigate different optical interconnection methods such as fiber image guides (FIGs), and free-space optical interconnections based on refractive lenses and diffractive lenses. The modeling of FIGs is presented for the waveguide simulations. Details on the contributions are given as follows:

### (1) A modular approach for optical interconnects: Transpar.

We present a modular approach for optoelectronic-VLSI system called Transpar. Transpar uses different optical and electrical components mounted on printed circuit board (PCB). Each component can be optimized to perform high speed, low noise optical interconnections. We present the characteristics of each component and discuss the optimization of the modular system. Experimental results are also presented.

#### (2) Optical interconnection system based on free-space.

Optical data packets can be transmitted and received via interconnection systems implemented with free space or fiber arrays. We present optical interconnection

methods based on free-space with bulk refractive lenses and diffractive optical elements (DOEs). We show that refractive lenses have much better optical coupling efficiency but their bulky size is a problem in packaging and alignment. DOEs offer the advantage of a small volume advantage and possible integration with VCSEL arrays. We discuss different pros and cons in free-space optical interconnection systems for Transpar and UTSi based systems. The system optimization in terms of power loss and packaging is also discussed.

#### (3) Fiber image guides (FIGs) interconnection.

FIGs can offer 2D parallel data transmission without any other optical elements and are a convenient way to interconnect optical receiver array and transmitter arrays. We introduce a FIG based optical interconnection system and explore methods to minimize optical loss and crosstalk.

#### (4) FIGs modeling and simulations.

The propagations of light in FIGs are modeled, simulated compared with experimental measurements. We first model appropriate laser modes for VCSELs and the hexagonal array FIG structure. The modeling and simulations are done using the RSoft BeamPROP package. We analyze the simulation results and compare with experiments.

#### (5) An integrated approach for optical interconnects: UTSi.

UTSi is an integrated approach for an optoelectronic-VLSI system. Electrical components are monolithically integrated on Si-based CMOS circuitry and optical I/O arrays are flip-chip bonded to the CMOS. We have designed and tested four different UTSi chips. Each UTSi chip has different devices, functions, and sub-systems. We demonstrate different testbeds based on each different function. Different PCBs are also designed to perform high-speed test plans.

#### 1.3 Organization of the Dissertation

The remainder of this dissertation is organized as follows.

- Chapter 2 reviews the background of optical interconnects. We discuss the need for optical interconnection systems in multi-giga rate date transfer. The design issues in integration of optoelectronic components and its network implementations are also discussed.

- Chapter 3 introduces a modular approach for optical interconnects. The idea of

Transpar and the network applications are presented. We introduce the use of field

programmable gate arrays (FPGAs) for the system logic and VCSEL/MSM arrays

for the optical I/O.

- Chapter 4 presents the demonstrator system based on Transpar and shows details

of the components and the implementation. The test results are also presented and

discussed.

- Chapter 5 introduces interconnection methods between optical I/O arrays. Free space optical interconnections based on bulk refractive lenses and diffractive optical elements are presented. We discuss the optical power profile, coupling efficiency and their influence on the system design.

- Chapter 6 explores the interconnection methods using FIGs. We examine the

optimization of the power profile and optical I/O coupling to minimize power loss

and crosstalk.

- Chapter 7 describes FIGs modeling and simulations. We discuss and compare the test results.

- Chapter 8 presents an integrated interconnection approach based on UTSi and we discuss the design issues and network applications.

- Chapter 9 presents different designs of UTSi based systems and evaluates the performance and the system implementations.

- Chapter 10 concludes on the results of the research and discusses possible future work.

## Chapter 2

## **Optical Interconnects for Electronic Systems**

Silicon-based CMOS VLSI has been the industry standard and will continue to be the mainstream technology in digital electronic devices and systems. However the bandwidth of the data communication I/O between electronic processing modules is reaching a limit. In recent years, optical interconnects have been introduced as a solution for the I/O bottleneck, and the development of optoelectronic devices such as dense VCSEL and detector arrays, and flip chip-bonding technology have accelerated the use of optical interconnects in digital electronic systems [46], [58], [66].

In this chapter we discuss the advantages of optical interconnects over electrical interconnects and discuss the design issues of optoelectronic integration with Si-based electronic systems.

### 2.1 Advantages of Optical Interconnects over Electrical Interconnects

Optical systems are used extensively in long-haul communication systems. Longdistance electrical communication links have limitations in bandwidth, impedance matching, power budget, and signal delay (skew) while optical links overcome many of these electrical limitations. The basic reason for the advantage comes from the high energy, high frequency nature of photons. Compared to electronics, optics has no frequency dependent loss and crosstalk, low loss over a long distance, low skew, and no need for impedance matching. In addition, the ability to use many different colors (wavelengths) in WDM gives more than 100 TBps bandwidth over a single fiber [48]. Therefore optical networks have been dominant in long-haul communication systems. However the use of optical interconnects in short distance data communication systems is very immature because short distance data communication has different characteristics from long-haul communication systems.

Table 2-1 summarizes the differences between telecommunications and data communications. Currently, data communication applications generally use conventional coaxial cable for short distances at data rates up to 622 Mbits/sec (OC-12). When the rate reaches over 1 Gbit/sec, optical solutions look attractive [35].

|                      | Data communications | Telecommunications    |  |

|----------------------|---------------------|-----------------------|--|

| Distance             | Short (< 300m)      | Long (> km)           |  |

| Fiber                | Multimode           | Single mode           |  |

| Wavelength           | Short (0.85 μm)     | Long (1.3 or 1.55 μm) |  |

| Typical data rate    | 1~ 10 Gbps          | 10 ~ 100 Gbps         |  |

| Electrical interface | Directly from ASIC  | Serial/de-serial      |  |

| Volume/price         | High/low            | Low/high              |  |

Table 2-1. Comparisons of data communications and telecommunications.

In current digital electronic systems, electrical interconnects have not yet reached their limits for typical applications, and cost effective optical interconnects are not yet available. It is expected that future system performance will be limited by I/O bandwidth soon and cost-effective optical interconnects may be required.

The bandwidth capacity for the electrical interconnects is limited by aspect ratio defined as

$$B \cong B_0 \frac{A}{l^2} \text{ bits/s}, \tag{2-1}$$

where A is the cross-section area of the line, l is the line length  $(A/l^2)$  is dimensionless) and the prefactor  $B_0$  is ~  $10^{15}$  for unrepeatered inductive-capacitive (LC) lines, ~  $10^{16}$  for resistive-capacitive (RC) lines, ~  $10^{17}$  for equalized LC lines [47]. These limits are relatively independent of the details of the design of the line.

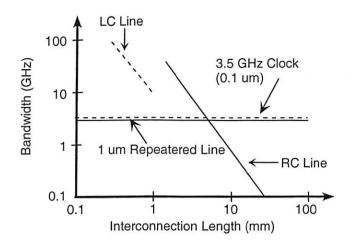

Figure 2-1 shows a simple modeling of the bandwidth and delay effects of Cubased electrical interconnections [45]. The modeling for RLC lines and repeatered lines is based on 0.25-μm technology and the 3.5 GHz clock line is based on future 0.1-μm technology. We also assume that the repeatered line is ideal and it simply attenuates all frequencies below the clock frequency to have the same loss as the clock frequency signal. From this discussion we see if the interconnection length is over 1 cm, the limitations of bandwidth and delay severely limit the 3.5 GHz clock-based system. Even with repeater amplifiers in the lines, the limitation of the delay is apparent over 1 cm [Fig 2-1 (b)]. Compared to these results, optical interconnects have no length-dependent limitation of bandwidth and the delay over the distance is much smaller than that of electrical interconnection.

Figure 2-1. Copper interconnection with 1  $\mu$ m  $\times$  1  $\mu$ m cross-section as a function of interconnection length [45]. LC and RC lines are with 1  $\mu$ m unrepeatered lines. The bandwidth of the repeatered line is with amplifiers to maintain a maximum bandwidth. On-chip clock rate is 3.5 GHz for 0.1  $\mu$ m technology. (a) Bandwidth of copper interconnect; (b) Delay of copper interconnect, the line labeled C for the case of optics.

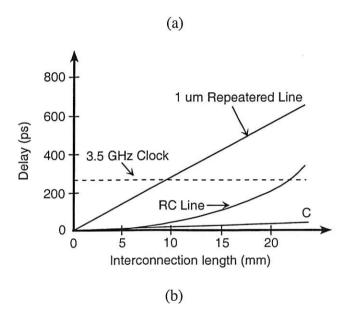

Another advantage of optical interconnects is the energy efficiency over the transmission distance [44]. A comparison of the energy required to send one bit shows optical interconnections can be more energy efficient than electrical interconnects for distance over 1 mm [Fig 2-2]. This calculation is based on  $10 \times 10 \ \mu m^2$  optical modulators, 1.5 eV photon energy, and 1 V electrical signal swing. It is also shown that smaller optical devices offer lower communication energies. Other groups show similar results and find that the on-chip energy requirements of one-to-one optical interconnect up to 2 cm are generally less than 50 pJ/bit transmitted, while electrical interconnects require on the order of several hundred picojoules [71]. From these results we can conclude that optical interconnects have advantages in power efficiency, bandwidth, and delay over distances of more than 1 mm.

Figure 2-2. A comparison of typical optical and electrical communication energies: the actual crossover point is system dependent [44].

In addition to the advantages above, optical interconnects are capable of dense 2-dimensional data processing without any crosstalk. While long-haul optical interconnects using WDM, use parallel spectral channels, short distance data communication increase the overall data rate at low cost by using parallel data channels. This is made possible due to the absence of electromagnetic crosstalk. Recently developed 2D VCSEL arrays are now available at relatively low cost. The ultimate density of optical interconnects is still an open issue that will affect the practical distance of the interconnections. The limit on the density of optical interconnects to chips is likely the power dissipation in the receiver and transmitter circuits.

#### 2.2 Optical Interconnects to Silicon CMOS: Design Issues

#### 2.2.1 Strategy

Optical devices are based on GaAs materials that have different lattice structures from Silicon. For this reason, it is very difficult to integrate optical I/O to silicon substrates and there are many approaches to integrated Si-GaAs technology to date. As a practical approach, a hybrid integration technology such as flip-chip bonding can be used. Several techniques for integration and system optimizations are described in Refs. [15], [27], [36], [64].

In the integration of optical transceivers to electric circuitry, the system power budget must be considered and optimized [70]. This is also one criterion for selecting appropriate optical sources and detectors. Low power lasers with threshold current

below 1 mA are essential and photodetector amplification must be very low power. In addition, transmitter and receiver circuits must not consume too much power. Integration of optoelectronic devices is a possible solution to reducing power consumption in the optimized systems.

Clock distribution strategy is also an important factor in system integration and optimization. Optical signals have no lower delay than electronic circuitry, but the optical transmitters and receivers in the system induce delay and can introduce excessive jitter and signal skew in the system. To avoid delay the circuitry for optical transceivers should have the same or fewer numbers of stages than their electrical counter parts.

Another consideration in integration is that optical transmitter and detector arrays need to be aligned to the optical signals and the tolerance of the misalignment must be considered. In the case when the optical components are directly attached to the chips this problem has to be considered with the system packaging. The packaging is an essential part of the design and implementation of an optical interconnection system and the system designers have to consider the final packaging at the beginning of the design for system optimization.

Generally, compared to electrical interconnection systems, optical interconnects gives two design benefits. The difficulty of impedance matching and wave reflections can easily be avoided. The inductance of the electrical connections to the chip that can give substantial voltage errors is not present in optical interconnections. In clock distribution, since optics have a very high frequency and the modulation frequency is

negligible compared to the carrier frequency, the optics itself does not have to be redesigned as the clock speed is increased.

#### 2.2.2 Component Requirements and Designs

#### **Optical Transmitter Array**

Optical transmitter arrays are an essential part of optics-based communication systems. Transmitters for high-speed optical communications require sources with high modulation bandwidth and high power at low threshold currents, small divergence angle, and cost-effective array capabilities. There are three different basic kinds of transmitters on the market for optical interconnection systems: quantum-well modulators, light-emitting diodes (LEDs), and VCSELs.

One type of quantum-well modulator is also called self-electrooptic effect devices (SEEDs) [46]. The modulators can be made in large arrays that can be flip-chip bonded onto VLSI chips. The performance of quantum-well modulators has proven good enough to allow demonstrations of large optically interconnection systems [30], but they require an external laser source, so that the optical system can be more complicated than in the case of active sources.

LEDs are relatively easier to manufacture at low cost than other devices. However, LEDs have limited speed response, low optical efficiency, and high divergence angle, therefore they are not generally used as the optical source for dense optical interconnects.

The use of VCSEL arrays has held promise as low-cost optical sources for optical array interconnections. Since VCSEL light is emitted perpendicular to the substrate, VCSEL arrays are more appropriate for 2D parallel optical interconnection systems. However there are drawbacks with current VCSELs. First, VCSELs have relatively high threshold current with a turn-on delay in the emission of light from the laser that depends on the previous data pattern. Second, VCSELs have different spatial optical modes and polarization at different current; and third, it requires high power supply voltages. Since future supply voltage of Si-CMOS likely to be under 1 V, the current high power supply voltages (~ 2 V) need to be lower. Despite these drawbacks, VCSELs are commonly used for short distance interconnections with 850 nm wavelength and research continues on single mode, low power, longer wavelength (> 1300 nm) or even tunable VCSEL arrays for local area optical interconnections [3].

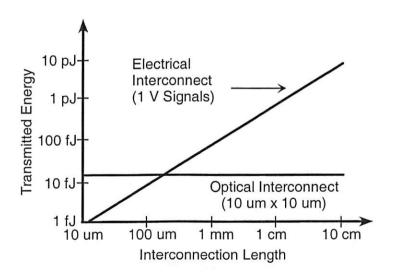

#### Photodetector (PD) Array

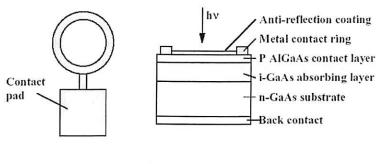

Favorable characteristics for a photodetector are low capacitance, short transit time, high responsivity (high sensitivity), and low dark current (low shot noise). The basic PD types are commonly used in optoelectronic-integrated devices. One is the PIN diode and the other is metal-semiconductor-metal (MSM) detector. These are shown in Fig. 2-2. The PIN diode produces a photocurrent that flows mostly vertically across the *i* region shown in Fig. 2-2 (a). The PIN diodes offer very good quantum efficiency up to 85 % with low noise.

(a) PIN diode

(b) MSM detector

Figure 2-2. Two most common photodetector types.

The MSM detector has photosensitive region consists of the interdigitated metal electrodes and produces a mostly lateral photocurrent flow as shown in Fig. 2-2 (b). The electrode geometry provides the MSM photodetector with a very low intrinsic capacitance, and thus the possibility of extremely high-speed devices. The MSM detectors have been also used in a number of microwave photonic applications because their compatibility for integration with field-effect-transistor devices in optically controlled monolithic microwave integrated circuits (MMICs) [62]. One drawback to use of MSMs is the low quantum efficiencies, typically in the range of 25 % to 40 %.

#### **Receiver Circuitry**

Receivers are an essential part of optoelectronic circuit design. Laser drive currents and other electronic I/O specification limit the degree of freedom in the design of electronic circuitry for optical interconnects. A low noise and high sensitivity receiver is necessary for reliable optical data processing in the system [15], [59], [61].

The optical receiver consists of an optical detector and a high gain, low noise transimpedance amplifier (TIA) that converts the low photocurrent to a large voltage variation with very short rise and fall times. Since typical input currents are in the range of  $1 \sim 100~\mu A$  and the typical output voltages are  $1 \sim 2.5~V$ , the transimpedance gain of the receiver amplifier must exceed 25 k $\Omega$ . With such a large-gain stage, the receiver designer has to be careful about the danger of oscillations, and should leave sufficient design margins to avoid them.

Small detector capacitance leads to larger voltage swings for a given photocurrent, which leads to better noise immunity and fewer gain stages. Also it allows the use of small, low-power dissipation transistors in the input stage. Therefore the capacitance of the photodetector and its connection to the receiver circuits should be as small as possible.

The noise, gain, and bandwidth of the TIA directly impact the sensitivity and speed of the overall system. The clock and data recovery functions must provide a high speed, tolerate long runs, and satisfy stringent jitter and bandwidth requirements [57].

# Chapter 3

# A Modular Testbed for Optical Interconnects

#### 3.1 Transpar

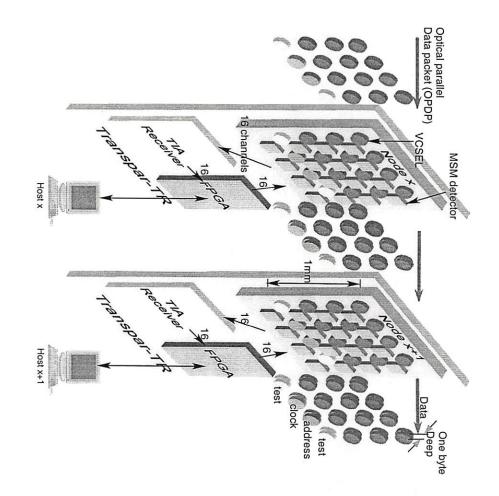

We have developed and built an optical interconnection testbed system called Transpar [4]. Transpar is configured as a high throughput photonic bus or ring network that transfers digital data using three-dimensional optical parallel data packets (OPDPs) propagating in free-space [16] or fiber image guides (FIGs) among nodes [18], [19]. It can provide high information capacity with digital interconnections and networks with three-dimensional (3D) optical data packets (2D spatial and 1D time) as in Fig. 3-1. Spatially parallel channels provide low latency for high-speed data transfers at the on-chip clock rate. Each node can serve as a high-throughput single-instruction-multiple-data (SIMD) parallel pipeline signal-processing node; with an internal arithmetic logic unit (ALU) and internal local mesh connections at each pixel.

Each 2D spatial channel is created by a smart-pixel array (SPA) [38]. By utilizing many spatial parallel channels Transpar can achieve high throughput, low latency communication between nodes. Each network node has three main components that are combined on a printed-circuit board (PCB). One is a Honeywell VCSEL/MSM smart pixel that is supplied by the DARPA-sponsored foundry project operated by the

program at George Mason University. Consortium for Optical and Optoelectronic Technologies ij Computing (COOP)

between them. Figure 3-1. Two Transpar nodes and free-space optical packets flowing from left to right

devices. flexible implementation of specific architectures without having to design custom chips The The second chip is a field-programmable gate array (FPGA) that allows the VCSEL/MSM arrays are two-dimensional arrays of optical input and output [65], [67]. The FPGA in Transpar is an Altera EPF10K100EQC 208-pin enhanced embedded programmable logic device from the FLEX10KE family. The third chip is a TIA receiver that amplifies the detected optical signals to electrical logic signals. We have designed four different TIA detector amplifiers and fabricated them through the MOSIS foundry. One of the drivers has been chosen for the best performance. We will discuss these components more in the next chapter.

FPGAs provide structural emulation at logic level and to mimic arbitrary logic level circuits. The FPGA can be programmed to implement different network logic such as: token-ring network, carrier-sense multiple access/collision detection (CSMA/CD), or other experimental protocols. Another advantage of the FPGA is that it can directly drive the VCSEL array. Its output voltage can be chosen to 2.5 V but it is limited to a drive frequency of 250 MHz for the FLEX10KE. For parallel processing, the Transpar node can operate as a mesh-connected SIMD processing-element (PE) array with electrical I/Os via FPGA or optical I/Os via 2D MSM detector or VCSEL array. The ALU performs add, subtract and other Boolean logic operations on bits that are stored in the local SRAM. The prototype system is able to perform very fast parallel processing of 2D data array, such as those required on image/video processing.

The logic design, design compilation, verification, timing analysis, and the programming of Transpar can be performed in Altera electronic design automation (EDA) tool, MAX+PLUS II.

For the optical interconnections between Transpar nodes we have investigated diffractive and refractive free-space optics, and FIGs for guided-wave interconnections.

Free-space interconnection systems have been studied in the past and demonstrated the usefulness and advantages of optical systems over electronic-only systems. However, bulk lenses and the difficulty of alignment of diffractive and refractive components might be obstacles to constructing practical systems. Diffractive optical elements (DOEs) or FIGs may be one of the key technologies to avoid packaging problems. DOEs are of comparable size to VCSEL arrays and could be monolithically integrated with VCSEL at low cost [42]. In comparison, FIGs are easy to set up and offer relatively flexible packaging and spatial parallelism that is easily realized.

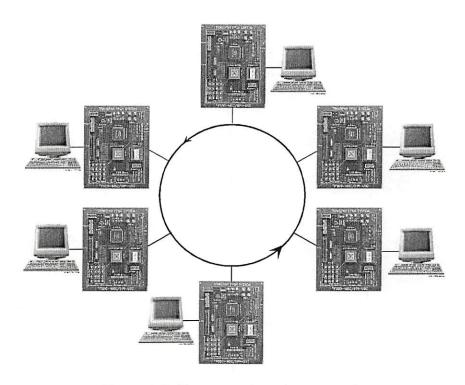

#### 3.2 Transpar Token-Ring Network

Transpar uses a particular network protocol called Transpar-token-ring (Transpar-TR) [16], [72]. Transpar-TR is a high throughput photonic ring network that transfers digital data using three-dimensional OPDPs propagating in free-space or waveguided medium among nodes. The number of nodes (N) in Transpar-TR is always an even number and each has an optoelectronic interface for an electronic host or server as shown in Fig. 3-2. N/2 optical parallel data packets are transmitted simultaneously around the N node ring using a slotted protocol that avoids the possibility of collisions. To avoid crosstalk, the Transpar-TR protocol does not allow the simultaneous use of VCSEL transmitters and MSM receivers.

In designing Transpar-TR, we have been concerned with potential electrical crosstalk between the closely spaced VCSELs and MSM-detectors at each node. The

VCSELs have mA drive signals that are three orders of magnitude greater than the  $\mu$ A signals generated by the MSM detectors. Similarly, optical crosstalk may also be a problem due to the divergence of the neighbor beams or unwanted reflections in the imaging system.

Figure 3-2. Transpar token-ring network.

In anticipation of crosstalk problems between VCSEL and MSM signals, several protocols have been evaluated and implemented. In the CSMA/CD protocol, each node simultaneously "listens" and "talks" to the network, requiring simultaneous operation of the VCSEL sources and MSM detectors. We have developed a novel slotted token-ring protocol for an N node (N even) Transpar-TR that is designed for collision free, high

throughput network operation and which also avoid simultaneous VCSEL/MSM operation. Hence, crosstalk problems are eliminated. In this scheme, each node waits for a 'ready to receive' signal from the next node before transmitting an optical packet. In contrast to the CSMA/CD protocol, packets are received, buffered and re-transmitted at each node as they traverse the network. Using this technique, the handshaking protocol allows packets from alternate network nodes to occupy the network concurrently. Thus *N*/2 nodes transmit simultaneously. A transmit queue and a receive queue serve as a bridge between the ultra fast optical network and relatively low speed of the electrical smart pixel array processors to minimize packet loss. Due to the parallel transmission of address and data packets, the processing latency is reduced compared to traditional serial token-ring networks. The CMOS SRAM process utilized in the Altera FLEX10KE FPGA devices can be rapidly reprogrammed. This suggests the possibility of implementing other novel OPDP protocols that can be dynamically reconfigured (to CSMA/CD or ATM, for example) depending on traffic level and other parameters.

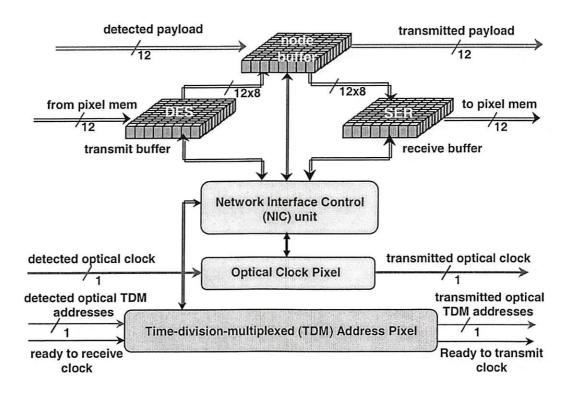

Figure 3-3 shows a block diagram with details of the FPGA logic functions at each node. As shown in Fig. 3-1, a detected incoming packet includes twelve detected payload channels, an address channel, and an optical clock channel. The double lines with arrows at the top left in Fig. 3-3 show twelve incoming payload (data) signals derived from optical inputs through the MSM detectors. The double lines at the top right are twelve transmitted signals that drive optical VCSEL outputs. The detected optical clock input at the left is generated by the previous (transmitting) node and is used to clock in the data and the node addresses. Incoming data is loaded into the node buffer at

the top. The ready to receive signal from the previous node goes to logic level "1" when the node is receiving an input.

Figure 3-3. Block diagram of Transpar TR logic functions.

The detected optical clock signal at a node comes from a local clock at the previous node, and its frequency can be different from the local clock frequency at other nodes. The slowest clock must be able to transmit an 8-bit deep 3D OPDP packet within the token time controlled by the ready-to-receive signal. To account for variations in the optical delay and minimize the bit error rate, the optical transmitted clock at each node is

delayed by 1/2 period so that the rising edge of each clock samples data in the middle of a bit time slot.

The address pixel reads the detected source and destination addresses, which are transmitted serially in one eight-bit byte, and sends them to the network interface control (NIC) unit (at the center of Fig. 3-3) where a comparison with the fixed node address are performed. The NIC is also responsible for global timing, optical clock generation, add/drop, retransmission, etc. The transmit buffer is a twelve channel deserializer, and the receive buffer is a twelve channel serializer. They perform packet adding and dropping in parallel with minimum delay and communicate with local pixel memory in serial for simplicity. The node buffers reshape the detected signal and limit noise accumulation or recirculation around the ring. In an advanced version of Transpar-TR, the transmit and receive buffers are twelve 8-bit long queues that are 7-bits deep (rather than 1-bit deep). These larger buffers perform even better to match the high-data rate of the optical ring network with the relatively slower host electronics. The 2D  $(3 \times 4)$ electrical data fields are transferred to and from the electronic host processor in Fig. 3-1 through the edge of the array in a 1D row-parallel format via a mesh network into twelve pixel memories (not shown). The pixel memories are connected to the transmit and receive buffers. The host processor controls these operations via the NIC unit and monitors the status of the OPDP packet network.

The Transpar-TR protocol is designed such that if the destination address of the incoming packet matches the node address, the packet is removed from the network and drops into the receive buffer. The oldest packet in the transmit buffer is added to the

network. If no address match occurs, the traffic on the ring has higher priority and continues to circulate around the ring to the next node. A newly generated packet is injected by a node into the network only if its ready to transmit time slot is or becomes empty. In case of packet add or drop contention, the new packet along with earlier ones, if any, are then queued in the transmitting queue. Any dropped (received) packets are queued in the receive buffer and moved to local pixel memories in sequence.

We describe now the test of a reconfigurable-Transpar system that specifically implements the Transpar-TR network protocol and host interface. In this test, two Transpar-TR nodes are set up with electrical inputs applied to emulate its operation in the optical token-ring network environment described. A data generator attached to the first node generates signal that would originate from the Honeywell MSM detectors. The VCSEL drive signal output of the first node is electrically connected to the detector input of the second node.

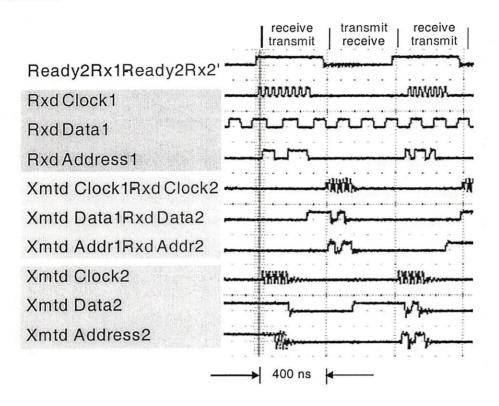

Figure 3-4 shows a test example of the communication between these two Transpar-TR nodes [16]. At the top are the Ready-to-Receive signal for node 1 (Ready2Rx1) and its complement (Ready2Rx2) for node 2. The top set of receive-transmit labels refers to node 1 and the bottom to node 2. Here the time interval for receive and transmit is 400 ns. When the Ready2Rx1 is high, node 1 receives incoming data (Rxd Data 1) and address data (Rxd Address 1) at the clock rate transmitted by the previous node (Rxd Clock 1). In the first 400 ns period shown, there is no address match, so at the next available transmit interval, node 1 retransmits the data and address to node 2 at its own local clock rate. In this example, as before, there is no address

match at node 2 so it again retransmits the data and address at its own local clock rate to the next node.

Figure 3-4. Two Transpar packet communications.

# Chapter 4

# Transpar Modular System Components and Experimental Setup

### 4.1 Printed Circuit Board (PCB)

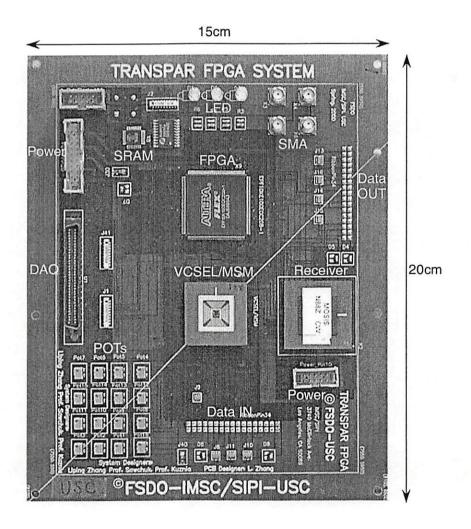

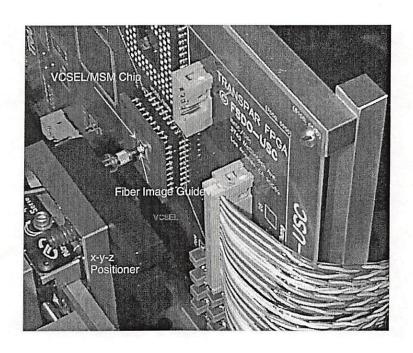

A printed circuit board (PCB) is used to test circuit components and interconnect them electrically. We have designed a PCB to test the Transpar system in which the components can be individually characterized for the optimal operating parameters and system integration. The PCB is four layers and made with conventional FR-4 materials. The physical size of the board is 15 cm × 20 cm as shown in Fig. 4-1. The PCB includes basically three major components: a FPGA chip for system logic, VCSEL/MSM chip for optical I/O, and a receiver chip for amplification of detected optical signals. These components are well positioned on the board to reduce crosstalk and power noise. We will discuss the details of these components in the next sections.

Other on-board components include surface mount decoupling capacitors, potentiometers, SMA connectors, SRAM, and pin connectors. The capacitors are designed to minimize switching noise on the power supply lines for high-speed operation. 16 separate potentiometers are to control the output optical power of the VCSELs individually. Two different power inputs are for the FPGA and receiver. A

32-bit SRAM chip is included to store data from the FPGA. Four SMA connectors are included to monitor high-speed data outputs. A 68-pin connector is on board for the data acquisition (DAQ) and 32 digital I/O lines are used. Ribbon cables are used to read and apply all 16 channels with data-in and data-out simultaneously and a 34-pin connector is mounted. A host computer can be connected to DAQ and monitor the data input and output.

Figure 4-1. Transpar PCB.

#### 4.2 VCSELs and MSM Detectors

Optical transmitters and receivers are the vital components in optical data communication. The requirements of optical transmitters are low power dissipation, high wall-plug efficiency (defined as the optical output relative to the electrical power), and stable operation with temperate change. In addition, the output power characteristics must be fairly uniform with spatial extent. VCSELs are one of the few light sources that satisfy the requirements and becoming widely available for high speed, short distance data communication systems. VCSELs have many advantages such as: low manufacturing costs, enhanced reliability, low threshold currents, low power consumption, high speed performance, circularly symmetric optical output and high density 2D array capability. 850nm VCSEL technology is accepted by the data communication industry [7]. The recent advent of VCSEL technology with longer and tunable wavelengths will soon be valuable in the telecommunication industry [3].

The desirable characteristics of photodiodes are low capacitance, short transit time, and high responsivity. Two different types of photodetectors are commonly used: MSM detector and PIN diode. We use MSM photodetector that is optimized at 850 nm wavelengths for Transpar system. PIN diode arrays are used for UTSi chips and are discussed later. The MSM photodetector is composed of back-to-back Schottky diodes that use an interdigitated metal electrode configuration on top of an active light absorption layer (GaAs). The interdigitated design minimizes parasitic resistance. The two adjacent metal electrodes are connected to upper or lower electrodes, respectively.

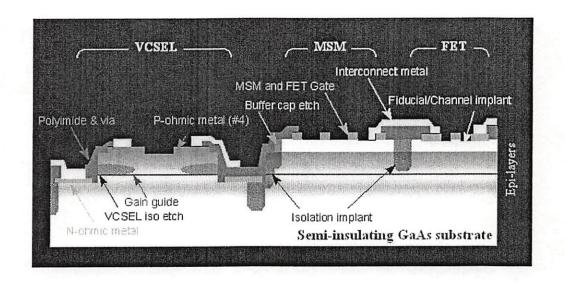

When biased during operation, either of the two electrodes could be chosen as cathode or anode. To manufacture the array of VCSELs and MSM detectors, the MSM is fabricated on a  $1.5~\mu m$  epilayer of undoped GaAs grown on top of the VCSEL structure and the undoped GaAs layer is selectively removed from the regions where the active VCSELs are located [38].

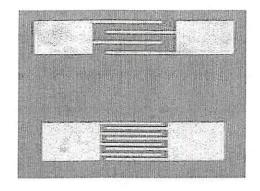

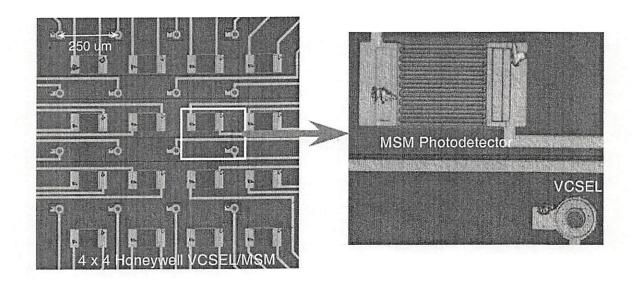

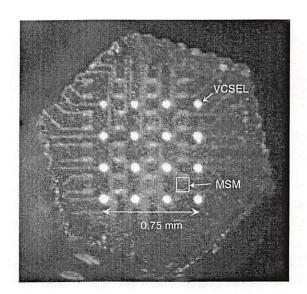

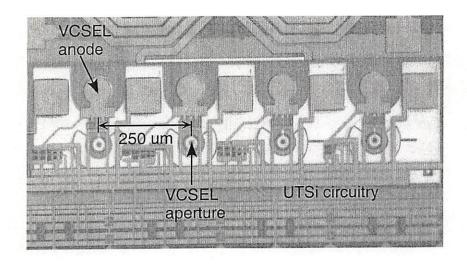

We have chosen Honeywell VCSEL chip that was obtained through the George Mason University COOP program. The chip has 4 × 4 array of VCSELs with interleaved MSM photodetector arrays. The physical properties of VCSELs and MSM detectors are summarized in Table 4-1 and a cross-section of the Honeywell VCSEL/MSM detector is shown in Fig 4-2. Figure 4-3 shows the interleaved VCSEL/MSM array layout.

| VCSEL                |              | MSM detector  |               |

|----------------------|--------------|---------------|---------------|

| Operating wavelength | 850 μm       | Responsivity  | 0.25 mA/mW    |

| Beam divergent angle | 15°          | Dark current  | <1 μA@ 5 V    |

| Optical power        | >1 mW@ 10 mA | Bias voltage  | > 0.22 V      |

| Optical window size  | 15 μm        | Detector size | 75 μm x 75 μm |

| Threshold current    | 4 mA         | Capacitance   | < 0.5 pF      |

| Pitch                | 250 μm       | Pitch         | 250 μm        |

Table 4-1. Honeywell VCSEL/MSM characteristics.

Figure 4-2. Cross-sectional view of Honeywell VCSEL/MSM chip.

Figure 4-3. 4 × 4 array of Honeywell VCSEL/MSM photodetector array.

#### 4.3 VCSEL Measurements

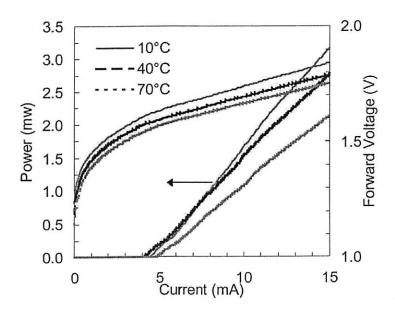

The Honeywell VCSEL output power as a function of current and voltage is shown in Fig. 4-4. We found experimentally that the impedance, output power, mode structure and frequency response of each VCSEL are closely interrelated and set the operation output power of the VCSEL to a minimum of 0.7 mW to a maximum of 1.3 mW for the highest frequency response (100 MHz). Higher power may also increase the effect of optical crosstalk to the neighbor detectors, thus it is important to determine an optimum optical power range. Crosstalk also can be produced by the reflection of VCSEL beams from the MSM detectors. To reduce these effects one might use anti-refection coated lenses.

The VCSEL output beam diameter  $\delta$  can be calculated by

$$\delta = 2d \tan \frac{\theta}{2} + a,\tag{4-1}$$

where d is distance between VCSEL and detector,  $\theta$  is VCSEL divergence angle (measured between its  $1/e^2$  profile), and a is the aperture diameter. The divergence angle of the Honeywell VCSEL is  $15^\circ$  and the aperture diameter is  $15 \mu m$ . This equation indicates that the distance between VCSEL and detector should be controlled to get the proper VCSEL output beam diameter. For example,  $\delta$  should be less than the detector pitch that is  $250 \mu m$  and the distance d should be less than  $0.9 \mu m$  without any optical elements. However longer interconnection can be realized using optical elements for beam collimating and focusing in practical optical interconnection systems.

The impedance of each VCSEL is dependent on the drive frequency, and therefore the VCSEL output power depends on the modulation frequency. To adjust for these different output characteristics, Transpar includes on-board potentiometers that vary the series resistance of each VCSEL from 1  $\Omega$  to 100  $\Omega$ . The potentiometers can be controlled individually to get uniform optical power for 16 different VCSELs.

Figure 4-4. Honeywell VCSEL output power performance [69].

# 4.4 Transimpedance Amplifier (TIA) Receivers

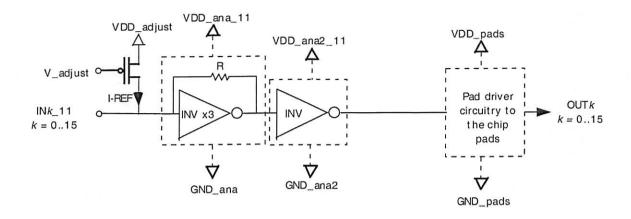

A low-noise, high-sensitivity receiver is essential for reliable transmission of optical data. The optical receiver consists of a photodetector, which converts the incoming optical power into electrical current, followed by a high-gain, low noise TIA that converts the small photocurrent to a large voltage swing. The Transpar system uses

a TIA receiver array that receives sixteen parallel signals in the form of currents from the MSM photodetectors on the Honeywell VCSEL/MSM array chip and converts them into 16 parallel digital CMOS signals for input into the FPGA chip. The TIA chip is intended for use with MSM detectors to convert photodetected current signals into 5 V CMOS compatible signals. The TIA chip was designed by Bogdan Hoanca, fabricated by MOSIS using the AMI 1.2  $\mu$ m process and is packaged in a 108 pin 12 × 12 PGA package. It also includes an array of 16 receivers for the detection of 16 parallel channels. The TIA is designed to meet the following specifications: low adjacent-channel crosstalk between small MSM signals (~ 10  $\mu$ A), stable and wide bandwidth operation (100 Mbps), high transimpedance gain (> 50 k $\Omega$ ), and ability to operate in a printed circuit board environment with large parasitic capacitance.

In order to find the optimal solution, the TIA receiver chip contained four distinct receiver designs. Through testing we found the best receiver design (shown in Fig. 4-5) that meets the above requirements. This design uses a preamplifier stage with multistage feedback to achieve high gain, followed by another gain stage and the digital output. The receiver chip is placed on a PCB as close as possible to the MSM chip and electrical connections should be made as short as possible between the output pins of the MSMs and chip and the receiver input pins. We have used a large number of separate power supply pins to ensure good separation between the analog and the digital domains on chip. To reduce the number of power supplies required, some of the pins can be connected together on the PCB, or even better at the power supply.

Figure 4-5. Block diagram of the TIA used in our experiments.

## 4.5 Field Programmable Gate Array (FPGA)

One limitation in optoelectronic systems is the need to design custom optoelectronic integrated circuits for each different application. This limitation can be addressed by merging a FPGA. FPGA is a device that can implement reconfigurable hardware and rapidly adapt to changing requirements and was emerged as a new technology for the implementation of digital logic circuits during the mid 1980's. FPGAs with optical I/O can have their functionality specified in the field by means of downloading a control-bit steam and can be used in a wide range of application, such as optical signal processing, optical image processing, and optical interconnects [67].

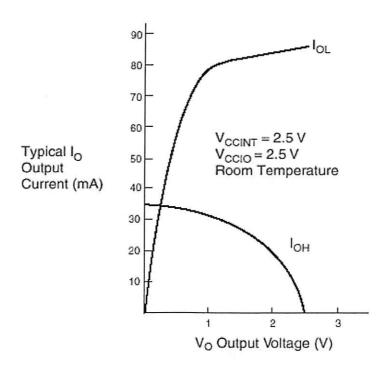

For Transpar, the design of the FPGA was synthesized from VHDL using the Maxplus II software package. The device operates at up to 250 MHz and has multi-volt I/O pins that can drive or be driven by 2.5 V, 3.3 V, or 5.0 V devices. We selected 2.5 V output in order to drive the VCSELs and found the FPGA can directly drive about 10

mA input current to the VCSELs [Fig. 4-6], so that the VCSEL output optical power can be about 1 mW.

To implement Transpar-TR, the FPGAs are programmed to implement a spatially parallel packet of a token-ring protocol. Our test system used an Altera EPF10K100EQC to drive 16 VCSELs in parallel. In Flex 10KE Devices 100 K of 250 K gates typically can be used, 50 K RAM and 250 MHz I/O. Also they have independent internal logic  $V_{CC}$  and I/O  $V_{CC}$  to allow direct drive of VCSELs. In testing the optical inputs and outputs of Transpar we use a 15-bit pseudo random string that is generated by the FPGA to drive the VCSELs on the Transpar board.

Figure 4-6. FPGA operation voltage and its current output.

#### 4.6. Power Setup

We need six separate power supplies for receiver array and MSM detector array. We supply 0.35 V for MSM bias; 4.93 V for  $V_{PAD}$  (power for output pins); 4.95 V for  $V_{dd-ana}$  (power for the first stage amplifier); 5.06 V for  $V_{dd-ana2}$  (power for the second stage amplifier); 4.91 V for  $V_{dd-adjust}$  (power for the threshold adjusting circuitry); 3.68V for adjust (threshold adjustment input).