#### **USC-SIPI REPORT #153**

Integration of Technology-Based Design Systems for VLSI Circuits

by

Chung-Ping Wan

February 1990

Signal and Image Processing Institute UNIVERSITY OF SOUTHERN CALIFORNIA

Department of Electrical Engineering-Systems

Powell Hall of Engineering

University Park/MC-0272

Los Angeles, CA 90089 U.S.A.

### Acknowledgment

I would like to express my appreciation to my research advisor, Professor Bing J. Sheu, for his guidance. I would also like to thank Professor Murray Gershenzon and Professor Ming-Deh Huang for serving on my dissertation committee. Their valuable comments and suggestions are very helpful in preparing the final version of this dissertation.

I would like to thank Hewlett-Packard Company for donation of the TE-CAP-3 program; The MOSIS Service at USC/Information Sciences Institute, Marina del Rey, CA, for its generous support; Stanford University, Stanford, CA, for the release of the PISCES and SUPREM programs; and University of California, Berkeley, for the release of the SPICE-3 program.

Valuable suggestions and assistance from my fellow graduate students in MOS VLSI Devices and Circuits group in PCE-210 are highly appreciated. Thanks are also given to Je-Hurn Shieh for help with the MESGEN program; to Antony H. Fung for helpful discussions on sensitive SPICE model parameters; to Ming Hsu for stimulating discussions on model parameter extraction; to Chih-Ching Shih for help with the capacitance measurement setup; and to Shih-Lien Lu for installing the PISCES and SUPREM programs.

This research was supported by National Science Foundation under Grant MIP-8710825, and by industrial grants from AT&T Company, Meta-Software Inc., and TRW Inc.

Last, but not the least, I would like to thank my parents and my wife for their support and encouragement. It is impossible for me to finish this dissertation without their constant encouragement.

## **Table of Contents**

| Chapter 1 - INTRODUCTION                                                | 1  |

|-------------------------------------------------------------------------|----|

| Chapter 2 - COMPUTER-INTEGRATED MANUFACTURING SYSTEMS FOR VLSI CIRCUITS | 6  |

| 2.1. Process-Level CAD Tools                                            | 7  |

| 2.1.1. Process Modeling                                                 | 8  |

| 2.1.2. Simulation Tools                                                 | 10 |

| 2.2. Device-Level CAD Tools                                             | 12 |

| 2.2.1. Semiconductor Equations                                          | 12 |

| 2.2.2. Simulation Tools                                                 | 14 |

| 2.3. Circuit-Level CAD Tools                                            | 14 |

| 2.3.1. Equation Formulation                                             | 17 |

| 2.3.2. Simulation Tools                                                 | 18 |

| 2.4. Equipment Modeling                                                 | 18 |

| Chapter 3 - INTEGRATION OF TECHNOLOGY CAD TOOLS                         | 19 |

| 3.1. The Need                                                           | 20 |

| 3.2. Integration Techniques for Device-to-Circuit Simulation            | 22 |

| 3.2.1. Table Look-Up Method                                             | 22 |

| 3.2.2. Conventional Parameter Extraction Method                         | 23 |

| 3.2.3. Mixed-Mode Simulation Method                                     | 23 |

| 3.2.4. Smart Link Method                                                | 24 |

| Chapter 4 - PARGEN: AN INTERFACE PROGRAM FOR PISCES-II           |    |

|------------------------------------------------------------------|----|

| AND SPICE-3                                                      | 25 |

| 4.1. PARGEN                                                      | 25 |

| 4.1.1. MOSGEN                                                    | 27 |

| 4.1.2. MESGEN                                                    | 32 |

| 4.2. Parameter Calculation                                       | 36 |

| 4.2.1. MOSFET Parameter Calculation                              | 36 |

| 4.2.2. MESFET Parameter Calculation                              | 41 |

| 4.3. PARGEN Results                                              | 41 |

| 4.3.1. MOSGEN Results                                            | 41 |

| 4.3.2. MESGEN Results                                            | 45 |

| 4.4. Applications                                                | 47 |

| 4.4.1. Integrated Simulation Environment                         | 50 |

| 4.4.2. Determination of Geometric Dependences of Submi-          |    |

| cron MOS Transistor Parameters                                   | 61 |

| Chapter 5 - SENSITIVE SPICE PARAMETERS FOR VLSI DESIGN           |    |

| ***************************************                          | 69 |

| 5.1. SPICE Modeling for VLSI Circuit Analysis                    | 70 |

| 5.1.1. Circuit-Level Modeling Requirements                       | 70 |

| 5.1.2. SPICE Built-In MOS Transistor Models                      | 72 |

| 5.2. Parameter Extraction for Different Fabrication Technologies |    |

| ***************************************                          | 73 |

| 5.3. Sensitive SPICE Parameter Subset                            | 79 |

| 5.3.1. Sensitivity Analysis                                | 79  |

|------------------------------------------------------------|-----|

| 5.3.2. Sensitivity Analysis Results                        | 83  |

| Chapter 6 - EFFICIENT SPICE TEMPERATURE DEPENDENCE         |     |

| MODELING                                                   | 89  |

| 6.1. Temperature Dependence Modeling                       | 90  |

| 6.1.1. Sensitive BSIM Parameter Subset                     | 90  |

| 6.1.2. The New Approach                                    | 91  |

| 6.2. Experimental Results and Discussion                   | 93  |

| 6.3. Theoretical Basis for BSIM Temperature Dependence     | 105 |

| Chapter 7 - CONCLUSION                                     | 108 |

| 7.1. Summary                                               | 108 |

| 7.2. Suggested Future Work                                 | 109 |

| 7.2.1. Parameter Calculation for Micron/Submicron MOSFET   |     |

| Models                                                     | 109 |

| 7.2.2. Parameter Calculation for Bipolar Transistor Models |     |

| ***************************************                    | 110 |

| Appendix A - PARGEN USER GUIDE                             | 111 |

| Appendix B - A NEW METHOD TO DETERMINE EFFECTIVE           |     |

| CHANNEL WIDTHS OF MOS TRANSISTORS                          | 118 |

| Appendix C - PARGEN PROGRAM LISTING                        | 135 |

| References                                                 | 156 |

## List of Figures

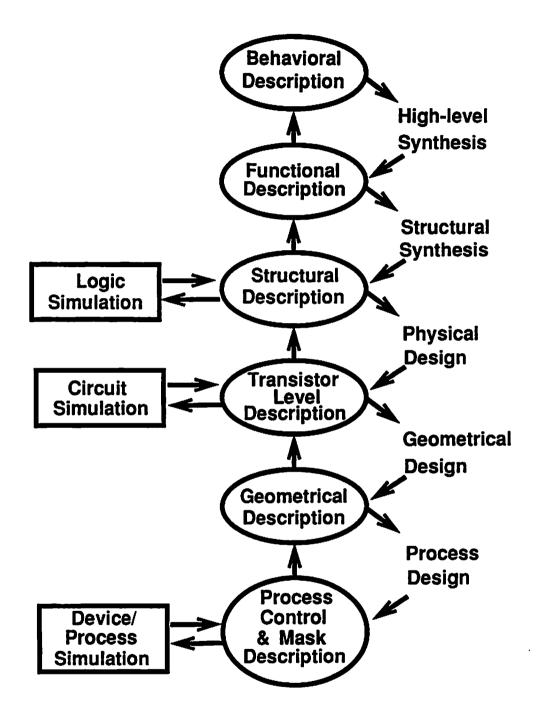

| Figure 1-1:  | The hierarchical relationship in VLSI design                                                                                                                                                                               | 2    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

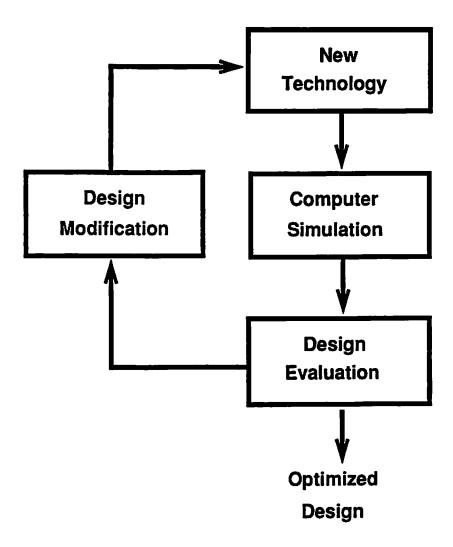

| Figure 1-2:  | Simulation-assisted technology development                                                                                                                                                                                 | 4    |

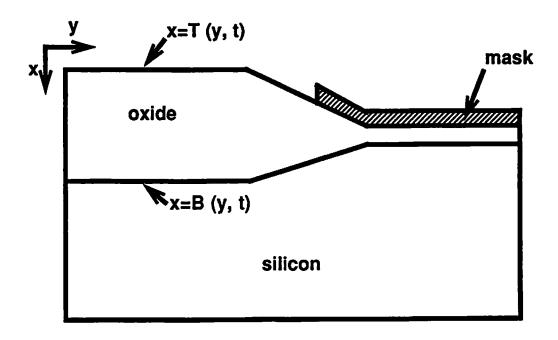

| Figure 2-1:  | A selective region for process modeling and simulation                                                                                                                                                                     | 9    |

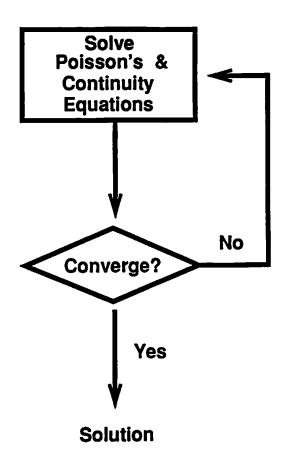

| Figure 2-2:  | Flowchart of the Newton's method                                                                                                                                                                                           | 15   |

| Figure 2-3:  | Flowchart of the Gummel's method                                                                                                                                                                                           | 16   |

| Figure 3-1:  | Flowchart of the conventional IC design approach                                                                                                                                                                           | 21   |

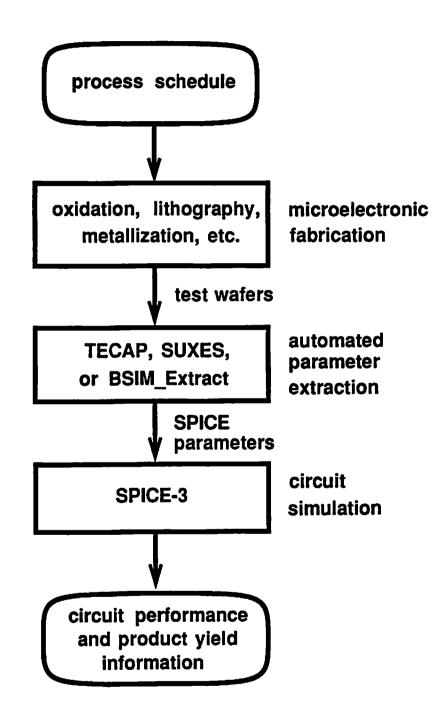

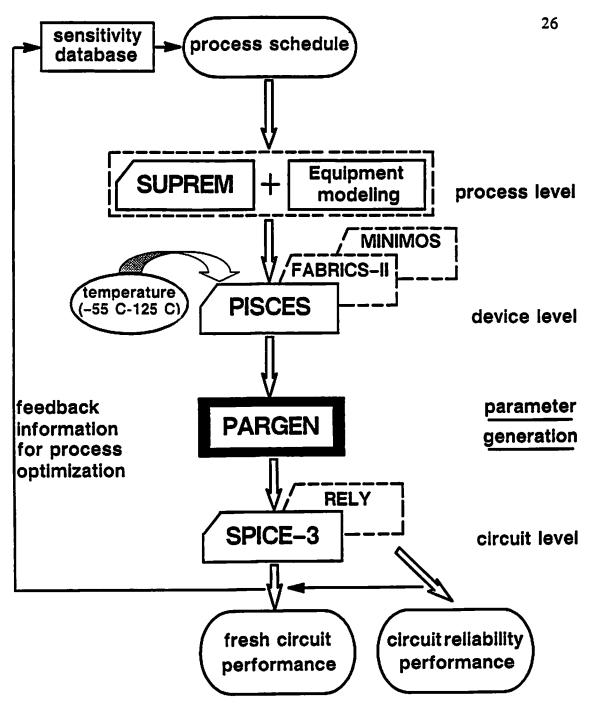

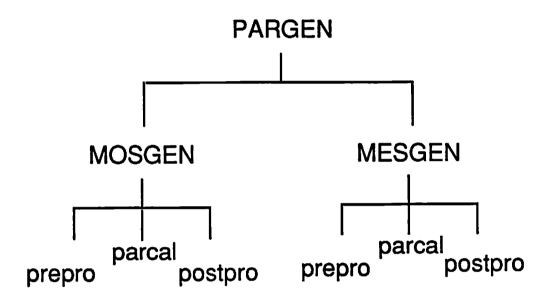

| Figure 4–1:  | Integrated simulation environment which allows a designer to examine how a microscopic fabrication variable affects final circuit performance and product yield. PARGEN is the interface program between PISCES and SPICE. | 26   |

| Figure 4–2:  | Organization of the PARGEN program                                                                                                                                                                                         | 28   |

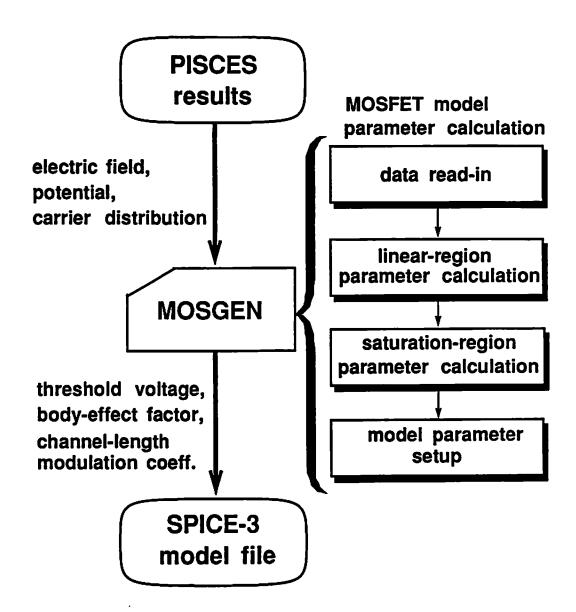

| Figure 4–3:  | Flowchart of the MOSGEN module which generates SPICE parameters for the Level-2 model.                                                                                                                                     | 31   |

| Figure 4–4:  | Cross section of a GaAs MESFET                                                                                                                                                                                             | 35   |

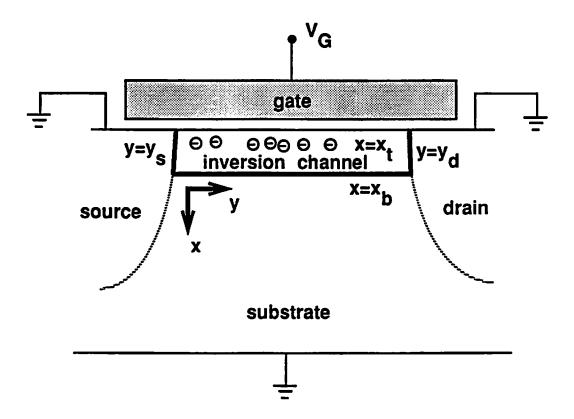

| Figure 4-5:  | Cross section of an MOS transistor highlighting the two-<br>dimensional area for the calculation of inversion charge                                                                                                       | 37   |

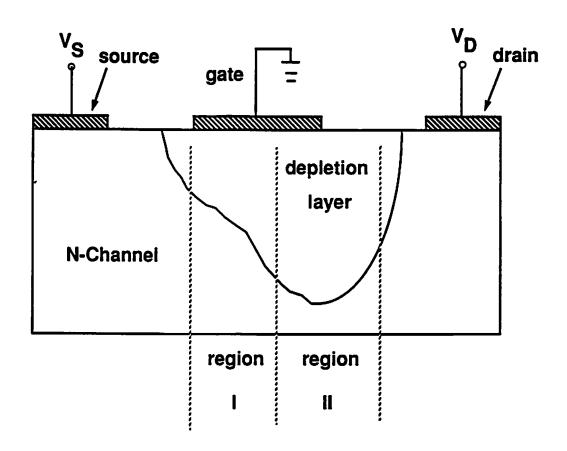

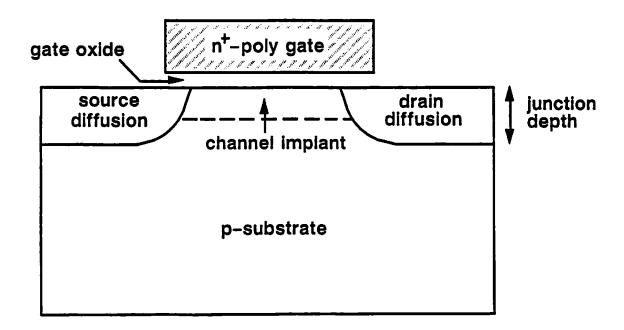

| Figure 4–6:  | Cross section of an N-channel MOS transistor used in PISCES device simulation.                                                                                                                                             | 42   |

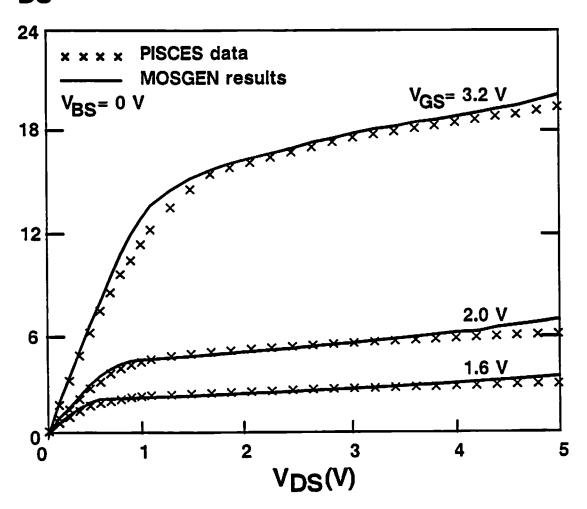

| Figure 4–7:  | Comparison of I-V characteristics between SPICE simulation results with MOSGEN-extracted parameters and the direct PISCES data for an $L_{\rm eff}=1.1~\mu m$ transistor. The Level-2 model is used.                       | 43   |

| Figure 4–8:  | Comparison of I-V characteristics between SPICE simulation results with TECAP-extracted parameters and the same set of PISCES data as in Figure 4-7. The Level-2 model is used.                                            | 44   |

| E: 4 C       | Commercian of manifestal TV characteristics between                                                                                                                                                                        | -9-4 |

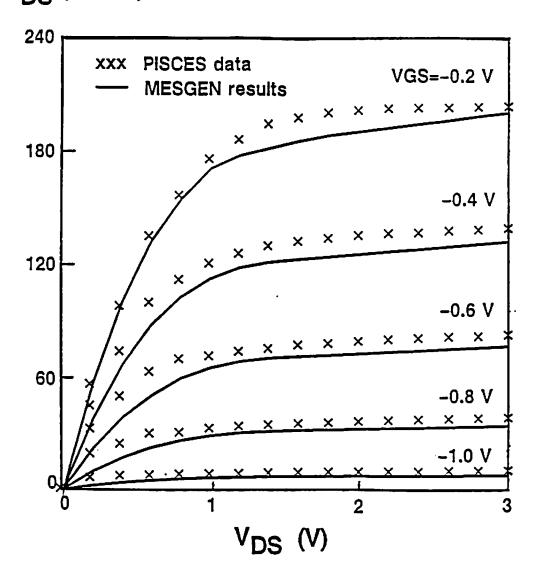

| Figure 4–9:  | Comparison of transistor I-V characteristics between MESGEN-SPICE simulation results and PISCES data for an $L=0.8~\mu m$ transistor.                                                                                      | 48   |

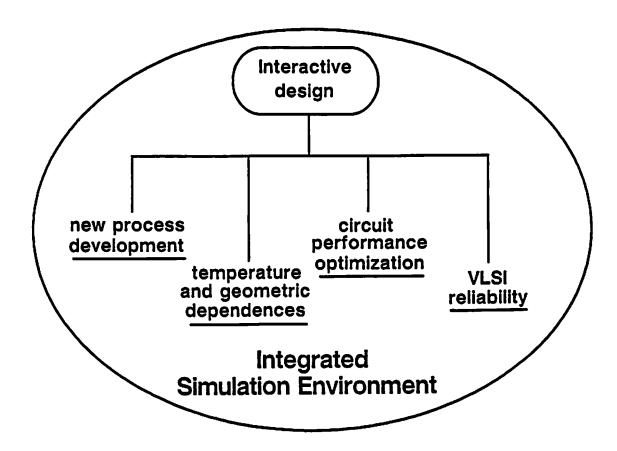

| Figure 4–10: | Potential applications of the integrated simulation environment.                                                                                                                                                           | 49   |

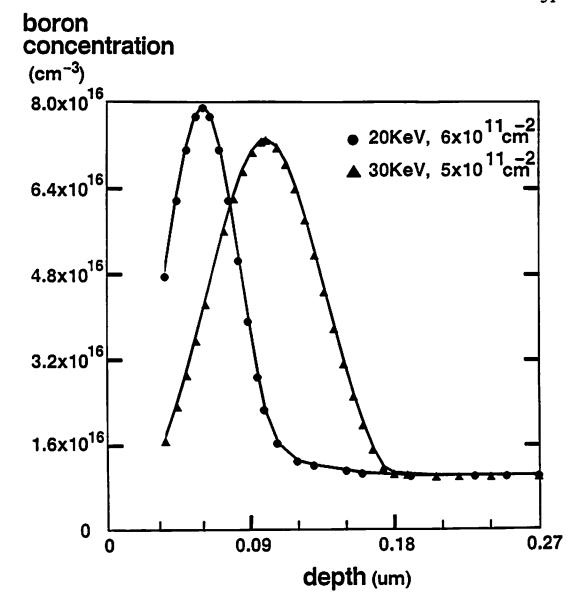

| Figure 4–11: | Simulated boron doping profiles on a silicon wafer for two ion implantation cases. The substrate doping is $1\times10^{16}$ cm <sup>-3</sup> .                                                                                                                                                                    | 51 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

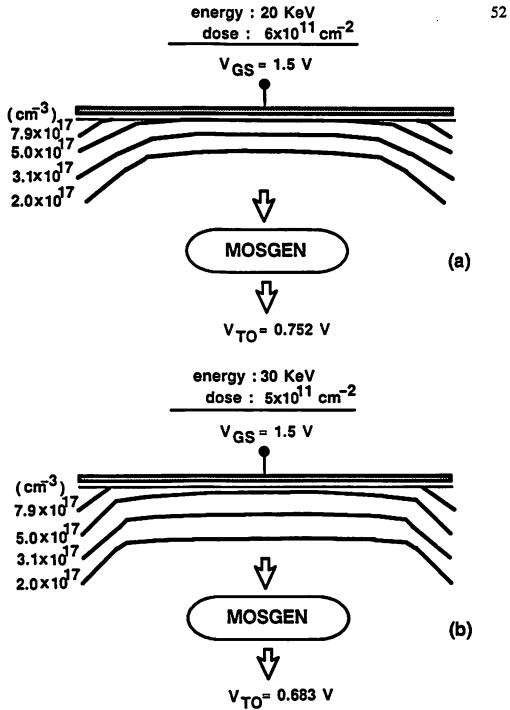

| Figure 4–12: | Two-dimensional carrier distributions from PISCES simulation. (a) An implantation dose of $6\times10^{11}$ cm <sup>-2</sup> and an energy of 20 KeV. (b) An implantation dose of $5\times10^{11}$ cm <sup>-2</sup> and an energy of 30 KeV.                                                                       | 52 |

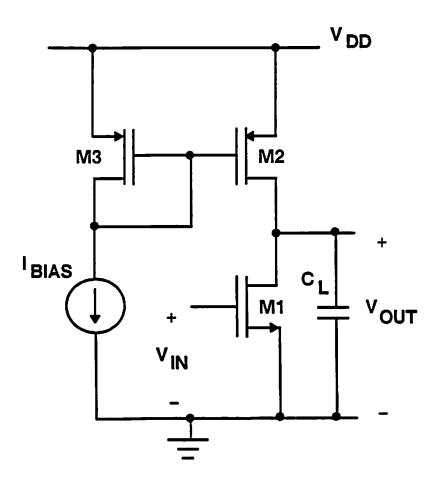

| Figure 4–13: | Circuit schematic of the core circuitry for a single-stage CMOS amplifier.                                                                                                                                                                                                                                        | 53 |

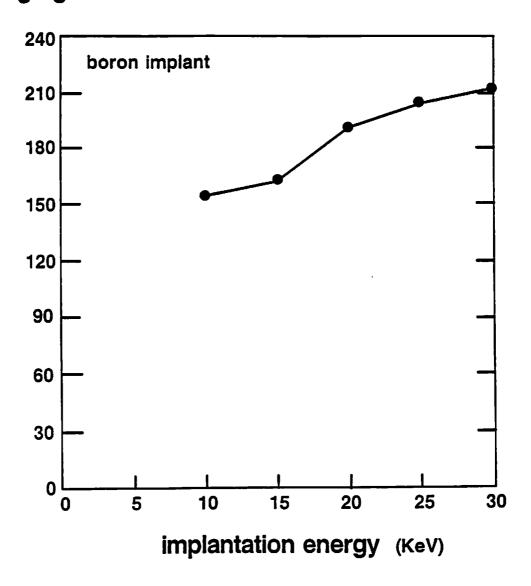

| Figure 4–14: | Plots of the open-loop voltage gain versus the boron implantation energy. The integrated simulation environment is used to produce the results.                                                                                                                                                                   | 55 |

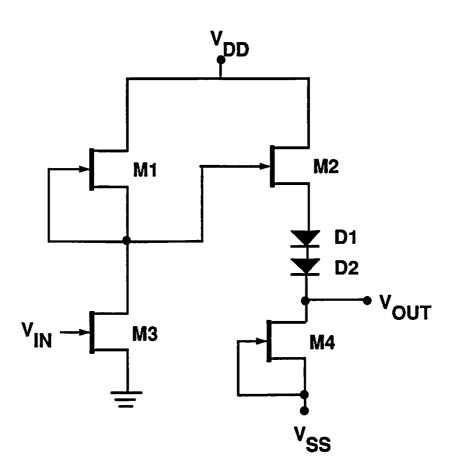

| Figure 4–15: | A GaAs inverter circuit with four MESFET's and two levelshifting diodes.                                                                                                                                                                                                                                          | 56 |

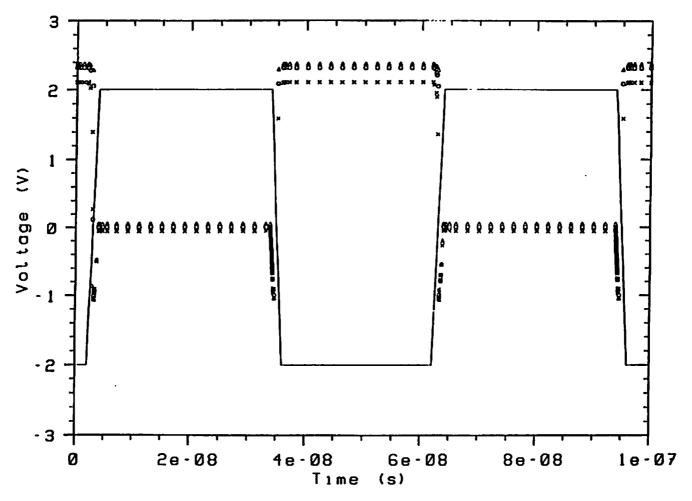

| Figure 4–16: | The inverter transient responses with different transistor active-layer thicknesses. $\Delta$ : 0.19 $\mu$ m, O: 0.17 $\mu$ m, x: 0.15 $\mu$ m. The solid line represents the input waveform                                                                                                                      | 57 |

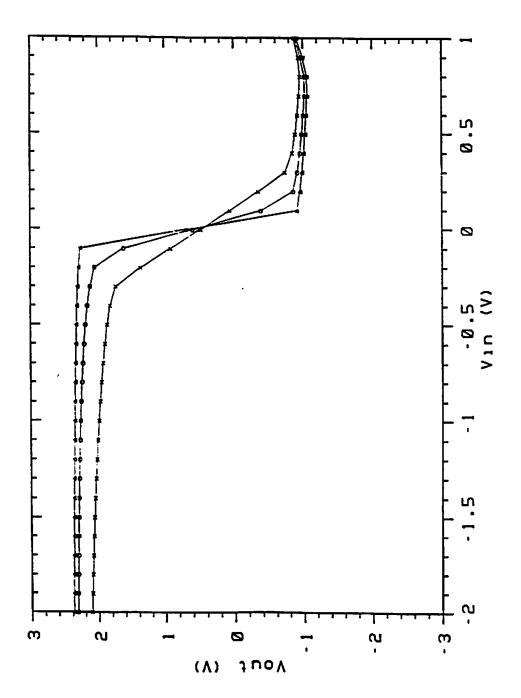

| Figure 4–17: | The inverter transfer characteristics with different transistor active-layer thicknesses. $\Delta$ : 0.19 $\mu$ m, O: 0.17 $\mu$ m, x: 0.15 $\mu$ m.                                                                                                                                                              | 58 |

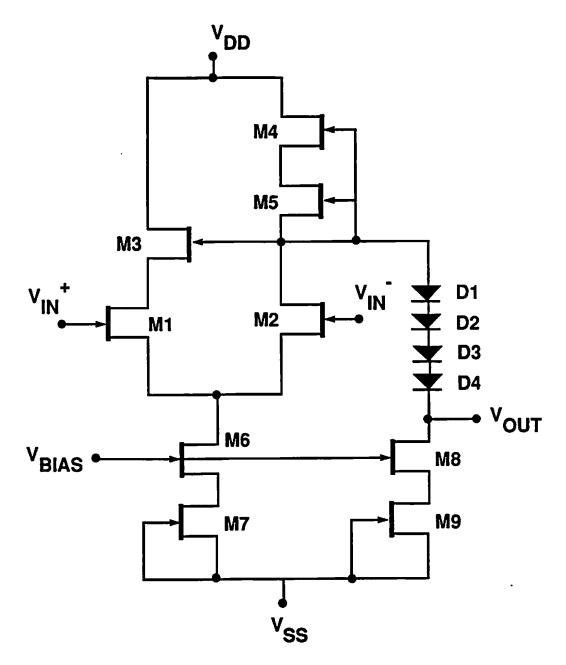

| Figure 4-18: | Circuit schematic of a single-stage GaAs Op-Amp                                                                                                                                                                                                                                                                   | 59 |

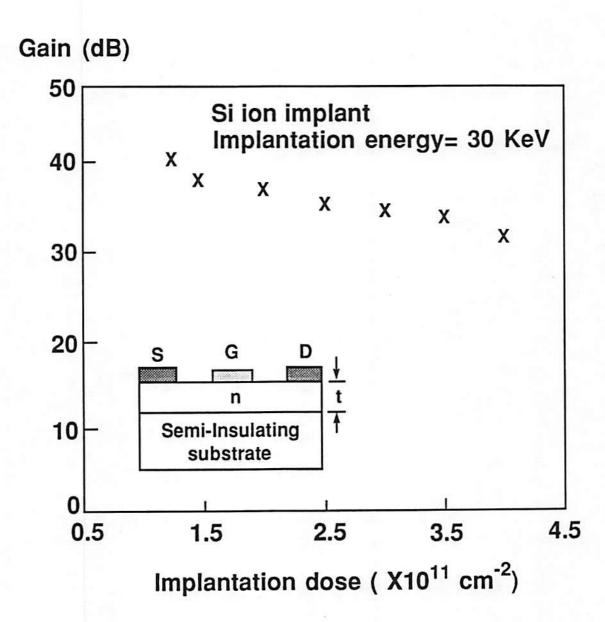

| Figure 4-19: | The effect of the implantation dose on the open-loop voltage gain.                                                                                                                                                                                                                                                | 60 |

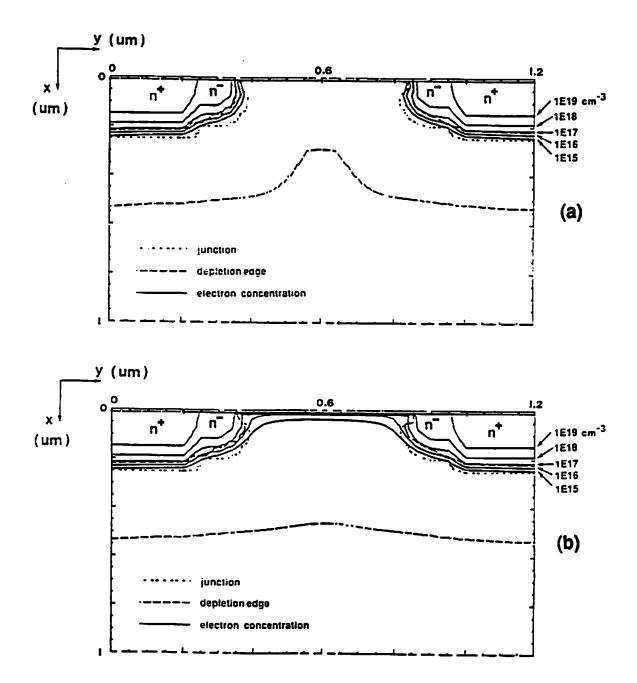

| Figure 4–20: | Electron concentration contours for an N-type LDD MOS transistor. (a) All terminals are grounded. (b) $V_{GS} = 1.5 \text{ V}$ , $V_{DS} = 0 \text{ V}$ , and $V_{BS} = 0 \text{ V}$ .                                                                                                                            | 63 |

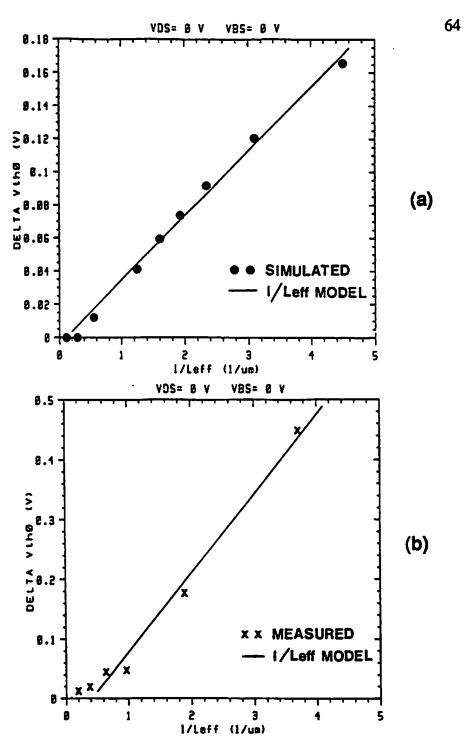

| Figure 4–21: | The plot of $\Delta V_{T0}$ versus $1/L_{eff}$ . A straight line is fitted through the data points with the least-square-error technique. (a) PISCES-extracted results. The correlation coefficient is 0.998. (b) Measured data. The correlation coefficient is 0.991.                                            | 64 |

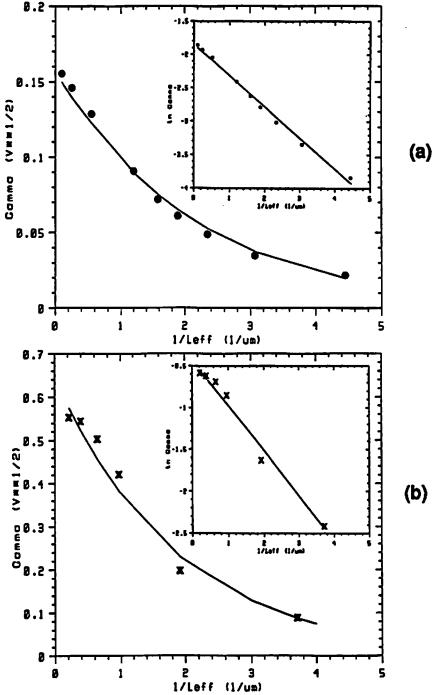

| Figure 4–22: | The plot of body-effect coefficient versus 1/L <sub>eff</sub> . The insert shows the logarithm of body-effect coefficient versus 1/L <sub>eff</sub> .  (a) PISCES-extracted results. The correlation coefficient in the insert is -0.996. (b) Measured data. The correlation coefficient in the insert is -0.991. | 66 |

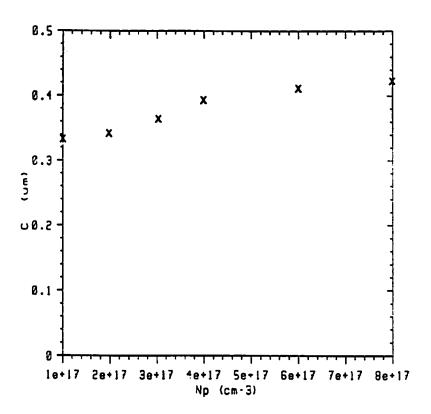

| Figure 4–23: | The plot of the parameter C versus the peak doping concentration in the channel.                                                                                                                                                                                                                                                                                  | 67 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

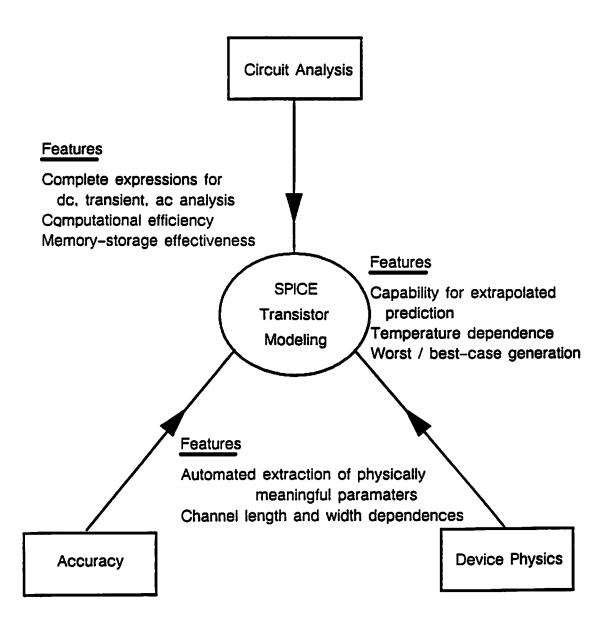

| Figure 5–1:  | Three key considerations for SPICE transistor modeling                                                                                                                                                                                                                                                                                                            | 71 |

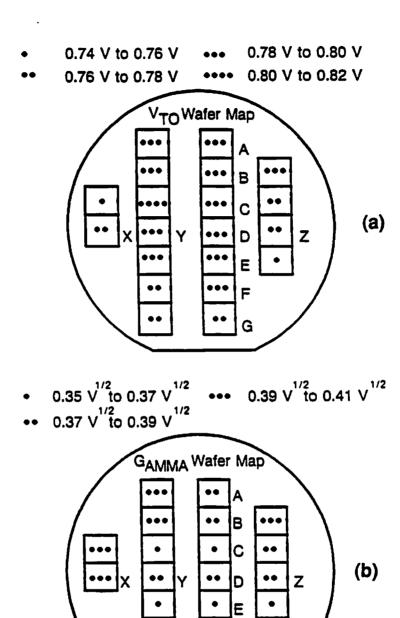

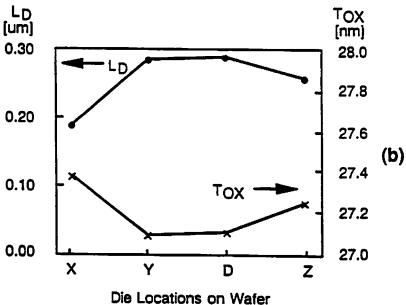

| Figure 5–2:  | Two-dimensional wafer mapping information. The test wafer was fabricated by a 1.2-\mu m technology. (a) Threshold voltage. (b) Body-effect coefficient.                                                                                                                                                                                                           | 77 |

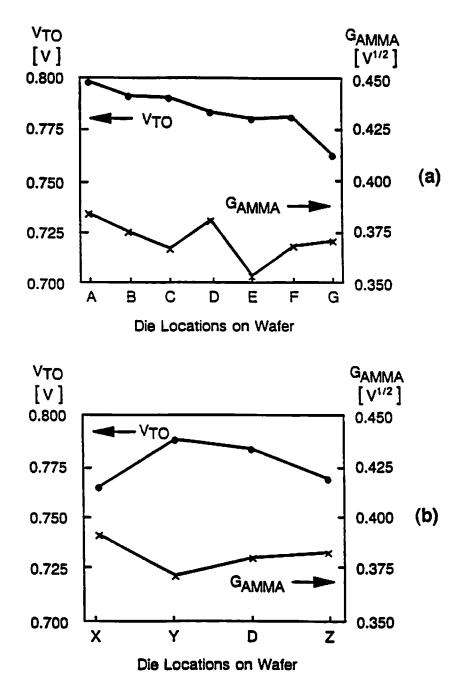

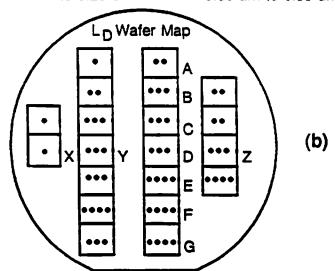

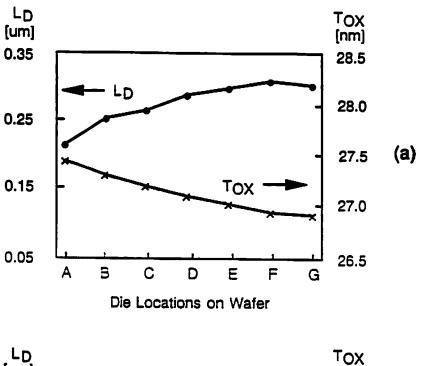

| Figure 5–3:  | Across-wafer variations of the threshold voltage and body-<br>effect coefficient for (a) die locations A to G, and (b) die lo-<br>cations X, Y, D, and Z.                                                                                                                                                                                                         | 78 |

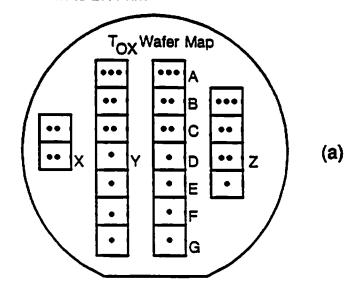

| Figure 5–4:  | Two-dimensional wafer mapping information. The test wafer was fabricated by a 1.2-\mu m technology. (a) Gate-oxide thickness. (b) Channel-length reduction.                                                                                                                                                                                                       | 80 |

| Figure 5–5:  | Across-wafer variations of the gate-oxide thickness and channel -length reduction for (a) die locations A to G, and (b) die locations X, Y, D, and Z.                                                                                                                                                                                                             | 81 |

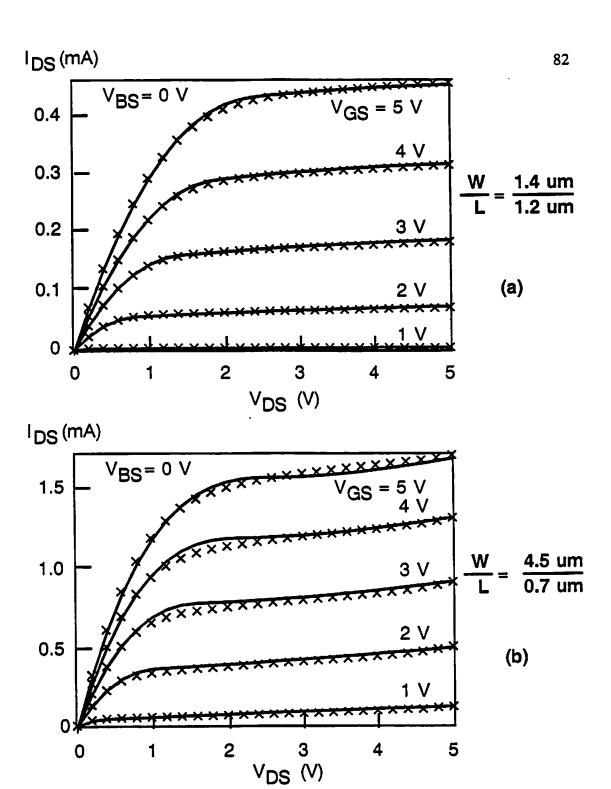

| Figure 5–6:  | Comparison of measured data and the simulated results using the Level-4 model. (a) A W/L = 1.4 $\mu$ m/1.2 $\mu$ m transistor. (b) A W/L = 4.5 $\mu$ m/0.7 $\mu$ m transistor.                                                                                                                                                                                    | 82 |

| Figure 6–1:  | Circuit performance verification procedure using the sensitive SPICE parameter subset approach.                                                                                                                                                                                                                                                                   | 92 |

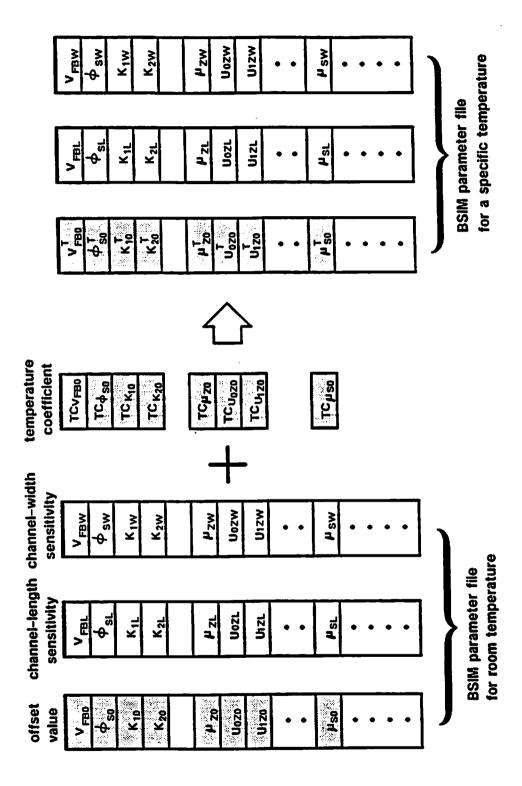

| Figure 6–2:  | Updating of the Level-4 model parameter values is done prior to circuit analysis at each given temperature                                                                                                                                                                                                                                                        | 94 |

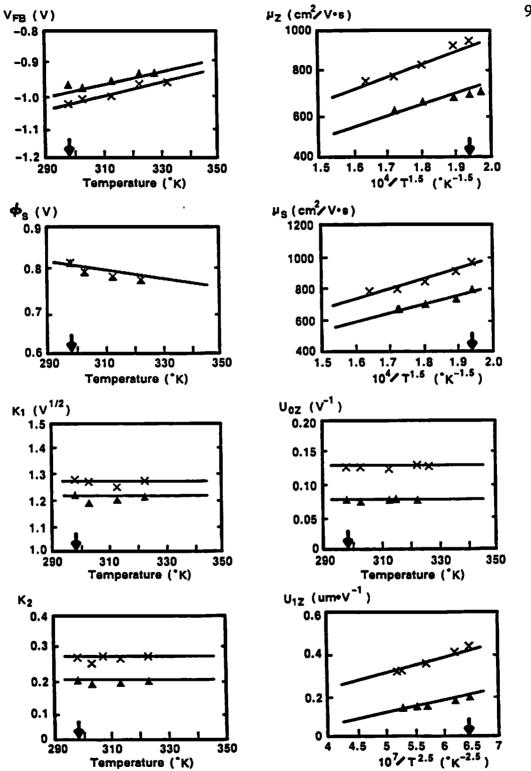

| Figure 6–3:  | Measured temperature dependences of sensitive Level-4 model parameters with W/L = $4.8 \mu m/1.2 \mu m$ ( $\times \times \times$ ) and W/L = $14.4 \mu m/3.6 \mu m$ (filled $\Delta$ ). Room temperature (298°K) is indicated by an arrow.                                                                                                                        | 95 |

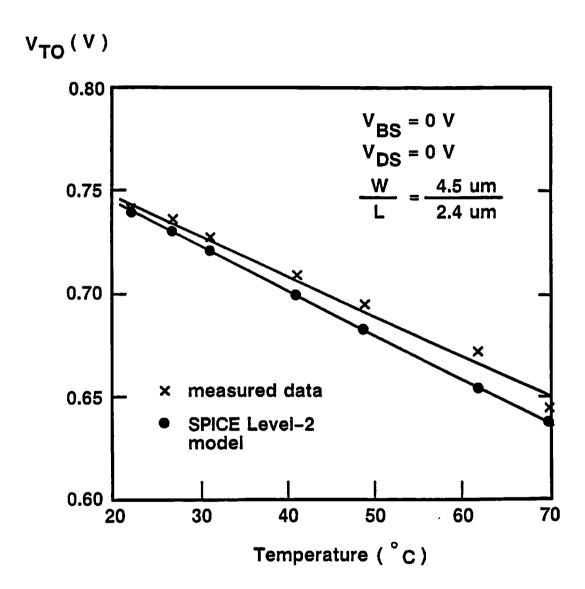

| Figure 6–4:  | A comparison of the measured and simulated results for the temperature dependence of the threshold voltage. The Level-2 model is used in the simulation for an N-channel MOS transistor.                                                                                                                                                                          | 98 |

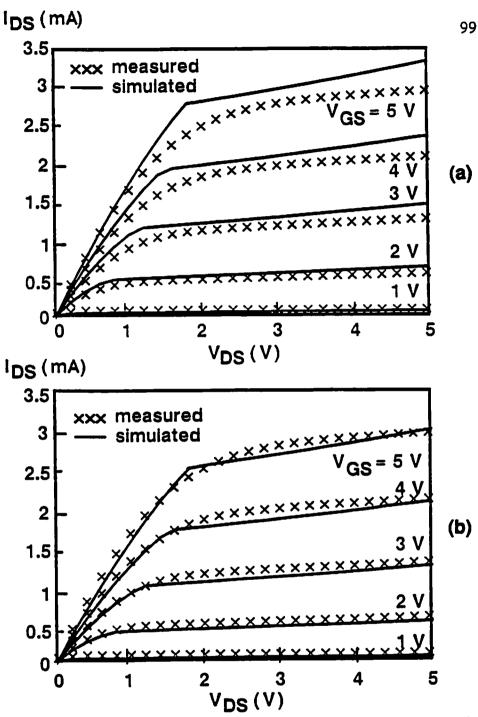

| Figure 6–5:  | Comparisons of the measured and simulated I-V characteristics for a $W/L = 14.4 \ \mu m/1.2 \ \mu m$ transistor at 70°C. (a) In simulation, only the temperature control command is used to update Level-2 model parameter values through SPICE. (b) In simulation, parameter values for the sensitive Level-2 model subset have been updated from new extraction | 99 |

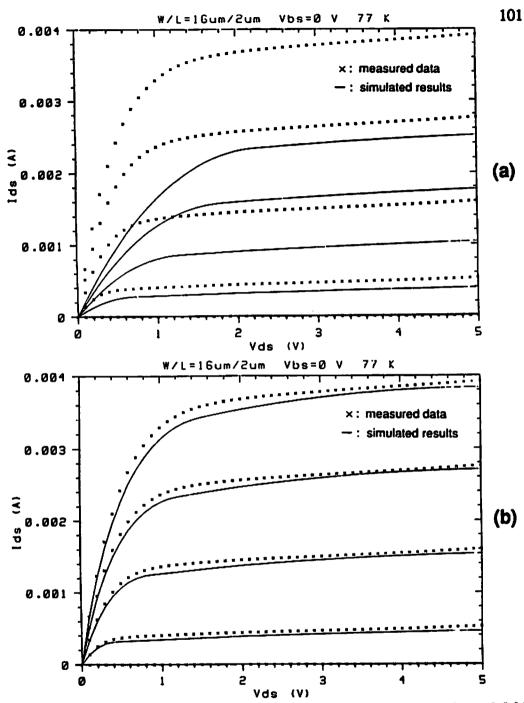

| Figure 6-6: | Comparisons of the measured and simulated I-V characteristics for a $W/L = 16 \mu m/2 \mu m$ transistor at 77°K. (a) In simulation, only the temperature control command is used to update Level-4 model parameter values through SPICE. (b) In simulation, parameter values for the sensitive Level-4 model subset have been updated from new extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 101 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

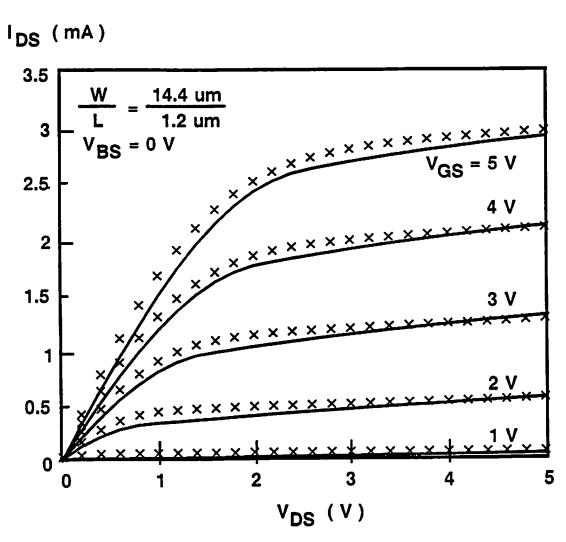

| Figure 6–7: | A comparison of the measured and simulated I-V characteristics at 70°C. In simulation, parameter values for the sensitive Level-4 model subset have been updated through the preprocessor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 102 |

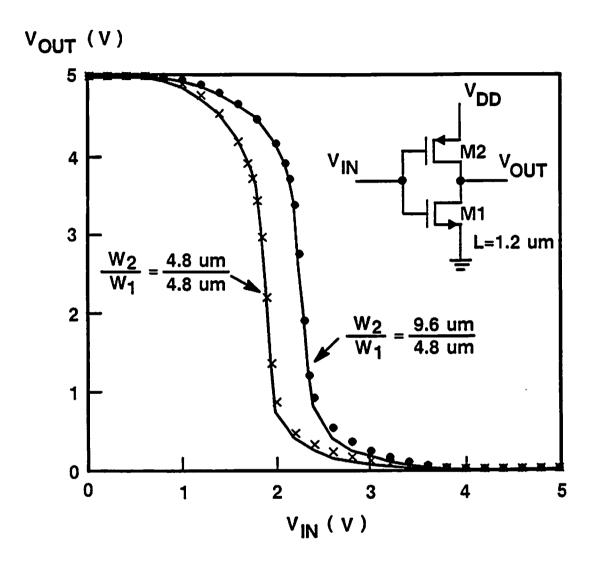

| Figure 6-8: | Measured and simulated voltage transfer characteristics of two CMOS inverters at 70°C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 103 |

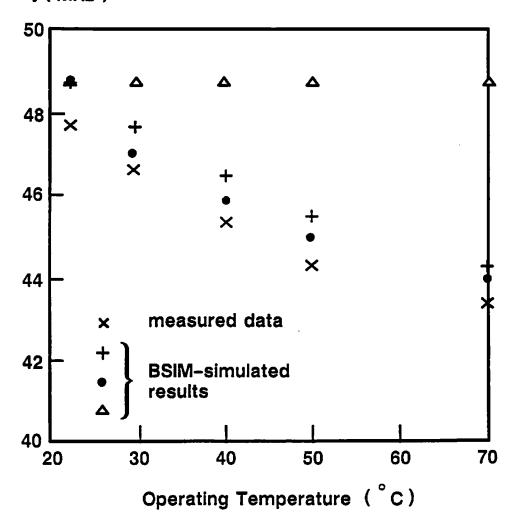

| Figure 6–9: | Measured and simulated frequencies of a 31-stage ring oscillator at different operating temperatures. " $\Delta \Delta \Delta$ ": Using temperature control command."+++": Using the sensitive Level-4 model parameter subset approach. " $\bullet \bullet \bullet$ ": Using all                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 104 |

| T71 A 1-    | apartos promotos control de versas control de ve | 104 |

| Figure A-1: | PISCES input deck to generate the data needed by MOS-GEN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 114 |

| Figure A-2: | A sample MOSGEN.IN file.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 116 |

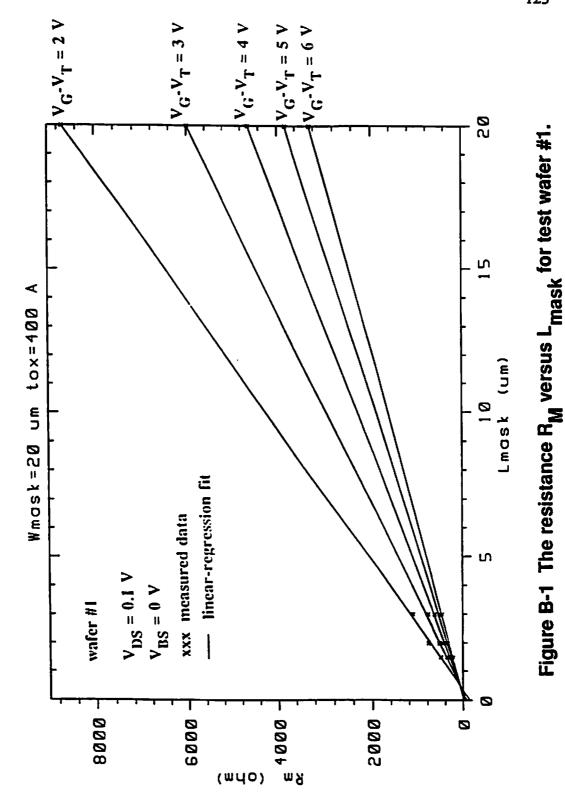

| Figure B-1: | The resistance R <sub>M</sub> versus L <sub>mask</sub> for test wafer #1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 123 |

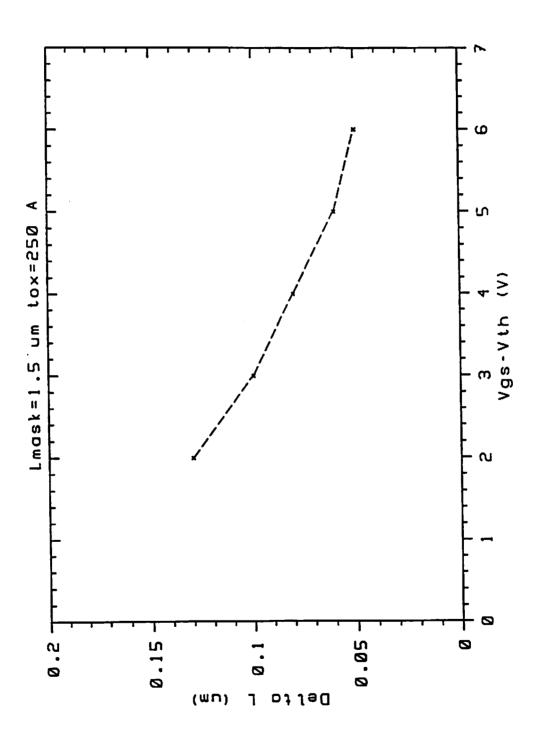

| Figure B-2: | The channel-length reduction $\Delta L$ versus $V_{GS} - V_{TH}$ for test wafer #2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 124 |

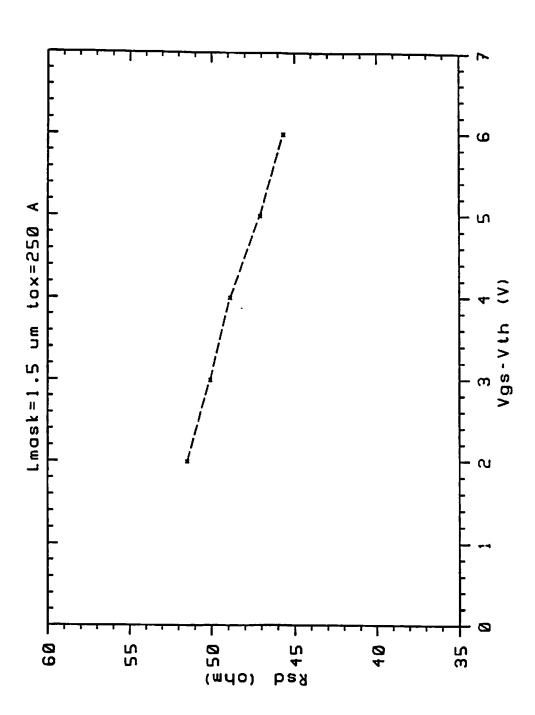

| Figure B-3: | The source/drain series resistance $R_{SD}$ versus $V_{GS} - V_{TH}$ for test wafer #2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 125 |

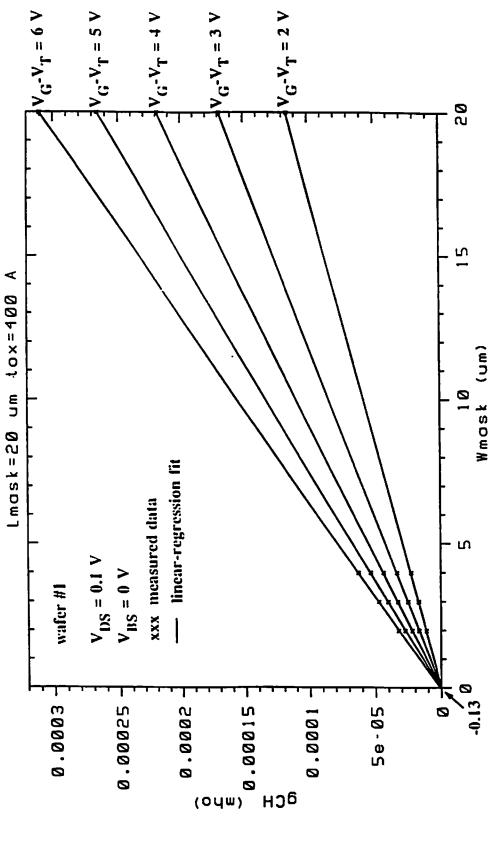

| Figure B-4: | The channel conductance $g_{CH}$ versus $W_{mask}$ for test wafer #1 using the new method. The channel-width reduction $\Delta W$ is determined to be -0.13 $\mu m$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 126 |

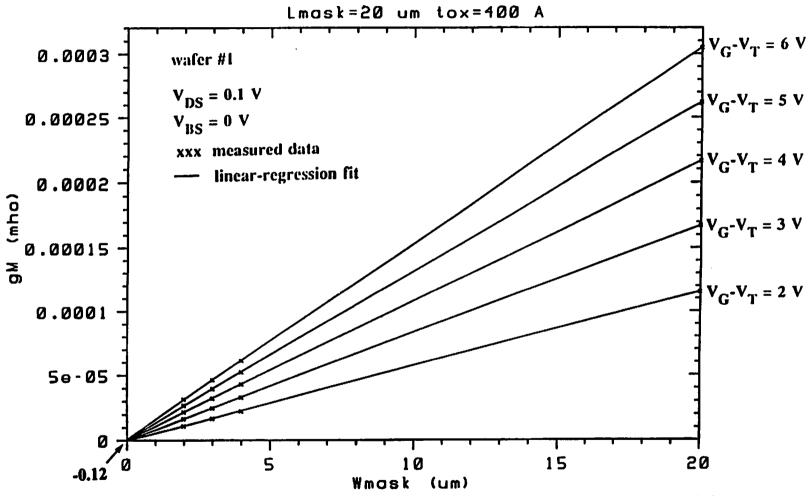

| Figure B-5: | The conductance $g_M$ versus $W_{mask}$ for test wafer #1 using Ma's method. The channel-width reduction $\Delta W$ is determined to be $-0.12~\mu m$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 127 |

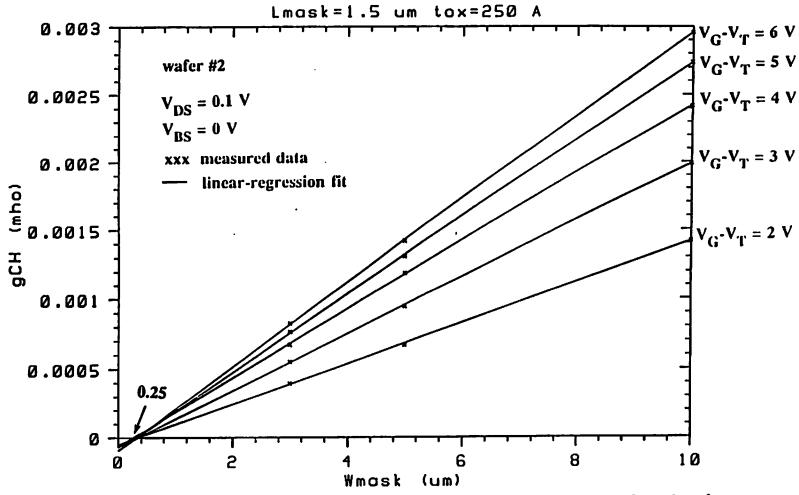

| Figure B-6: | The channel conductance $g_{CH}$ versus $W_{mask}$ for test wafer #2 using the new method. The channel-width reduction $\Delta W$ is determined to be 0.25 $\mu m$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 129 |

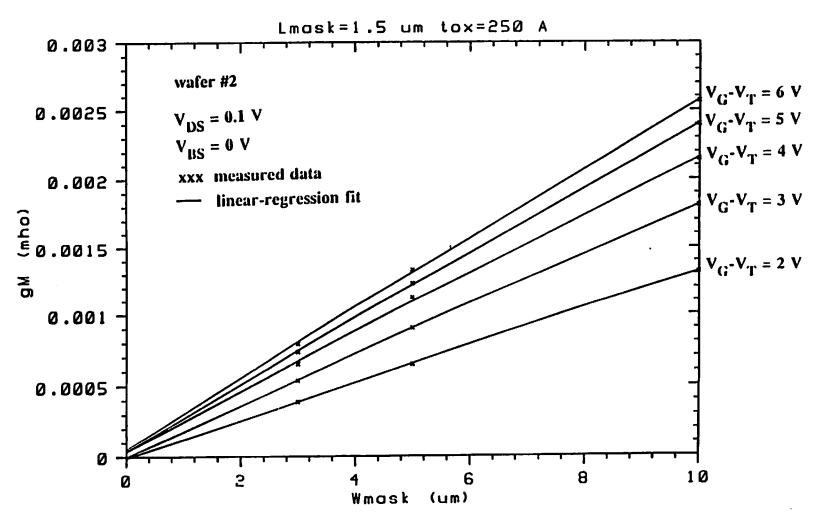

| Figure B-7: | The conductance g <sub>M</sub> versus W <sub>mask</sub> for test wafer #2 using Ma's method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 130 |

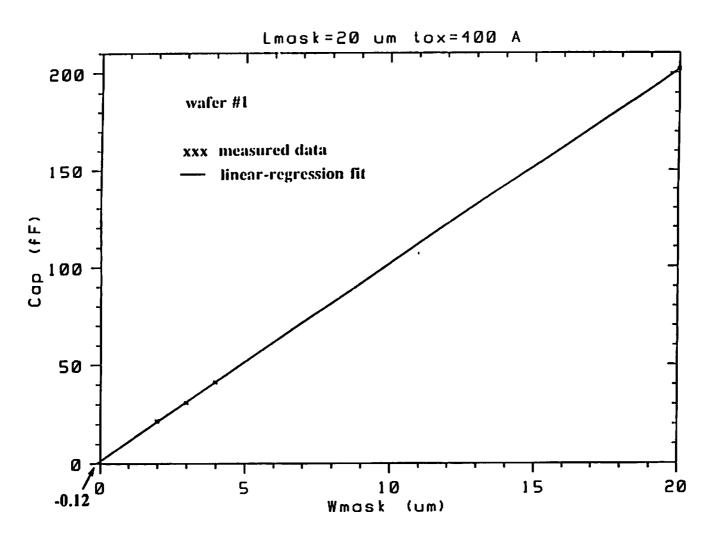

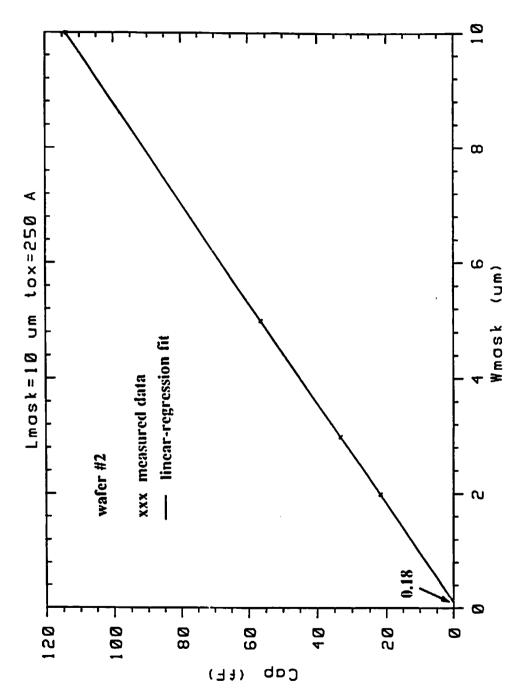

| Figure B-8:  | Intrinsic gate capacitance versus $W_{mask}$ for test wafer #1. The channel-width reduction $\Delta W$ is determined to be $-0.12~\mu m$ . |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Figure B–9:  | Intrinsic gate capacitance versus $W_{mask}$ for test wafer #2. The channel-width reduction $\Delta W$ is determined to be 0.18 $\mu m$ .  |

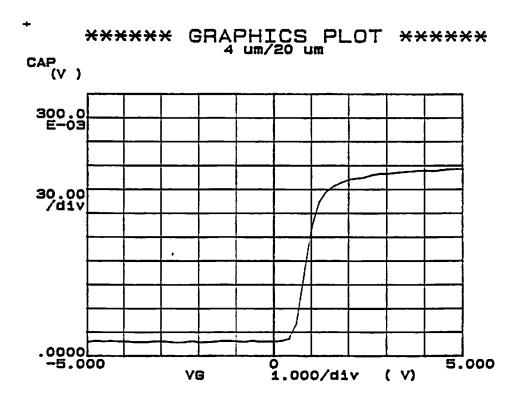

| Figure B-10: | Measured capacitance (uncalibrated) versus V <sub>GS</sub> for the capacitance method                                                      |

## List of Tables

| Table 4–1:         | Biasing conditions for PISCES runs to be used by MOSGEN. (An N-channel MOSFET is assumed.)                  | 29  |

|--------------------|-------------------------------------------------------------------------------------------------------------|-----|

| Table 4-2:         | Biasing conditions for PISCES runs to be used by MESGEN.                                                    | 33  |

| Table 4–3:         | MOSGEN-extracted SPICE Level-2 MOSFET model parameters.                                                     | 46  |

| Table 5–1:         | Comparison of important features among various existing SPICE MOSFET models.                                | 74  |

| <b>Table 5–2</b> : | Sensitivity analysis results for the Level-2 MOSFET model parameters in a 3-\mu m technology.               | 85  |

| <b>Table 5–3</b> : | Sensitivity analysis results for the Level-2 MOSFET model parameters in a 1.2-\mum technology.              | 86  |

| Table 5-4:         | Sensitivity analysis results for the Level-4 MOSFET model parameters in a 2-\mu m technology.               | 87  |

| Table 5–5:         | Sensitivity analysis results for the Level-4 MOSFET model parameters in a 1.2-\(\mu\mathrm{m}\) technology. | 88  |

| Table 6-1:         | Temperature dependences of sensitive BSIM parameters                                                        | 96  |

| Table B-1:         | Comparison of $\Delta W$ determined by the capacitance method and the new resistive method.                 | 133 |

#### **Abstract**

Integration of technology-based design systems is strongly needed for the manufacturing of very-large-scale integrated circuits. The computer-aided design program PARGEN which provides accurate and efficient interface between the device simulator PISCES-IIB and the circuit simulator SPICE-3C1 in the technology-based design system is described. Algorithms to calculate parameter values for the built-in MOSFET and MESFET models have been developed and incorporated into this interface program. Only six device simulation results are required to extract a complete set of the popular Level-2 MOSFET model parameters and four device simulation results are needed for the MESFET model in the circuit simulator. This interface program, together with the process simulator, device simulator, and circuit simulator, form an integrated simulation environment for computer-integrated manufacturing of microelectronic chips. Such an integrated simulation environment greatly facilitates the designers to examine just how a microscopic fabrication variable, such as the implantation dose, affects final device and circuit performance and product yield. A methodology for efficient circuit modeling and simulation in the integrated simulation environment is also described. A subset of circuitlevel sensitive parameters which have large effects on simulated transistor output characteristics is used in this methodology. The sensitive model parameters are identified through a sensitivity analysis. This methodology has been applied to the temperature dependence modeling of the BSIM (Berkeley short-channel IGFET model) for MOS transistors in the circuit simulators. Updating of model parameter values for the sensitive parameter subset is performed prior to circuit simulation at each given temperature. For a 1.2-µm CMOS fabrication process, the sensitive parameter subset for temperature

effects consists of only eight out of the sixty-seven BSIM parameters. Circuit simulation results using this sensitive model parameter subset approach agree with experimental data on transistor output characteristics, inverter transfer characteristics, and oscillation frequency of a 31-stage ring oscillator.

## Chapter 1

#### Introduction

Rapid advances in very-large-scale-integration (VLSI) technology have resulted in the reduction of minimum feature sizes from several microns to submicrons over the past fifteen years. By the year 2000, the feature size can be reduced to 0.15 µm in an advanced CMOS process and a density of 10<sup>8</sup> transistors per chip can be achieved for memory devices [1.1]. With such a high level of integration, a complete electronic system can be fabricated onto a single chip. To successfully design complex VLSI circuits, extensive use of computer-aided design (CAD) tools is a necessity. The CAD tools are invaluable in integrated circuit designs.

Figure 1-1 shows a hierarchical method for VLSI design. The behavioral description of the system is transformed into an integrated circuit following several synthesis stages: high level synthesis, structural synthesis, physical design, and process design. An analysis step is performed after each synthesis stage to verify that the new description is functionally equivalent to the more abstract input description. If these descriptions do not match, changes are made in previous descriptions by following the appropriate feedback path to any of the earlier synthesis stages. In the design sequence, computer simulators are used for the process, device, circuit, logic, and behavioral simulations. Layout, placement, and routing tools are used to aid the physical design of VLSI circuits. These CAD tools play a critical role in the successful designs of VLSI systems.

Figure 1-1 The hierarchical relationship in VLSI design.

The rapid rate of change in process technologies also mandates extensive uses of CAD tools for new technology development. The development of new technology traditionally has been guided by the experimental approach. Starting with an existing process, critical steps are modified and this modified process is realized by fabricating several lots. Finished test structures are then evaluated carefully to examine whether the design goals are achieved. This trial-and-error procedure requires many iterations to optimize a new process. However, with proper simulation programs, the development time and cost can be greatly reduced. As shown in Figure 1-2, the process design can be verified through computer simulations and adequate modifications to the process design can be made to obtain the desired design.

One key issue in the integrated-circuit fabrication is the yield and performance of VLSI circuits. Increasing emphasis on the yield and performance of VLSI design has driven the semiconductor industry toward automation of manufacturing facilities to fabricate complex integrated circuits with minimum feature sizes in the submicron range. An important concern in the complete automation of semiconductor manufacturing environment involves the integration of CAD tools to provide quick simulation so that the product yield can be optimized prior to fabrication. The integration of CAD tools requires the coupling between process, device, and circuit simulators.

The particular interest of this dissertation is the integration of technology-based design systems for VLSI circuits. One contribution of this work is the development of an efficient approach to coupling the device and circuit simulators. Different approaches have been developed to link the device and circuit simulators by other researchers [1.2-1.5]. However, their approaches require hundreds of device simulation runs and the computational cost is very high. In our approach, only several device simulation runs are required to accomplish the integration task using the newly developed computer-aided design program. The incorporation of this interface program into the simulation environment makes possible the efficient integration of process, device, and circuit

Figure 1-2 Simulation-assisted technology development.

simulators. The integrated simulation environment is of fundamental importance for the technology development and product yield optimization in computer-integrated manufacturing (CIM) systems for VLSI circuits.

The other contribution of this dissertation is the development of a new methodology for the technology-based design environment. As statistical process variations have more significant effects on VLSI device characteristics, a great number of device and circuit simulations have to be performed in the device and circuit designs. However, since the parameters of MOS transistor model do not have uniform influence on the device output characteristics, a set of sensitive circuit-level model parameters which have large effects on the transistor output characteristics can be identified for efficient circuit modeling and simulation. The use of sensitive model parameters facilitates VLSI circuit designs in the technology-based design environment.

In Chapter 2, the computer-integrated manufacturing systems and technology CAD tools are discussed. The need for the integration of technology CAD tools are discussed in Chapter 3. The interface program for the new approach is described and its applications are presented in Chapter 4. In Chapter 5, a new methodology using sensitive parameters is presented for efficient modeling in the technology-based design environment. The application of this new methodology to the temperature dependence modeling of SPICE Level-4 MOS transistor model parameters is described in Chapter 6. Chapter 7 concludes this work and suggests the future work along this research direction.

## Chapter 2

# Computer-Integrated Manufacturing Systems for VLSI Circuits

Fabrication of VLSI circuits is a very complicated manufacturing process. Hundreds of processing steps, such as oxidation, ion implantation, etch, lithography etc., are involved in the fabrication of VLSI circuits. The process schedule must be tested before it can be applied to real fabrication lines. Adequate control on the equipment for processing is needed to accomplish the desired processing steps. In-process measurements are to be made to monitor the process flow. Large amount of data is collected and analyzed so that feedback can be provided for the process and equipment control. The data storage, data analysis, and information exchange between different pieces of equipment are complicated tasks in the fabrication. The increasing sensitivity of circuit performance to inherent process variations due to decreasing device sizes also requires better process and equipment control to guarantee a high product yield and good performance of VLSI circuits.

Advanced computer-integrated manufacturing (CIM) systems are crucial in the reliable production of standard and application-specific VLSI circuits and systems. In CIM systems, information management, process and equipment control, testing and measurement, and design verification are all accomplished through the use of computers. Computers not only maintain control and improve productivity, but also make automation of manufacturing process possi-

ble. The complete automation of a semiconductor manufacturing facility involves the integration of design, wafer fabrication, assembly, and test with management information systems. Computer simulations play a vital role in the integration of design for CIM systems. A VLSI simulator for the manufacturing environment enables the prediction of device, circuit, and yield behavior of a complex VLSI process based on the specification of a process, the characteristics of the fabrication equipment and laboratory environment, and a description of the geometric pattern information. There is a strong need for the development of efficient and accurate computer simulation tools in manufacturing environment so that a designer may compare simulated results to measured data on a real-time basis.

Technology CAD tools have been widely used for VLSI technology development and integrated circuit design over the past two decades. These tools offer a predictive capability and they can be used to evaluate processing options and performance prior to fabrication. For a particular technology, process and device simulation tools can be used to optimize product yields and track variations in production, and circuit simulation tools are used for circuit analysis. These tools prove to be useful for systematic determination of the worst-case and best-case model parameters and they provide a means of understanding the underlying causes for observed variations and problems in the fabrication process and which parameters should be monitored and adjusted.

#### 2.1. Process-Level CAD Tools

A VLSI fabrication process consists of hundreds of steps. Process level CAD tools are used to deal with all aspects of VLSI fabrication. Given a description of the processing steps and layout geometry, the process simulator determines the details of the resulting device structure, including the boundaries of the different material layers of the structure and the distribution of doping impurities within these layers.

The analysis capability of process-level CAD tools can be used for several purposes, including the evaluation of process models, the determination of physical coefficients and the calculation of electrical parameters. The capability of calculating electrical parameters allows a process designer to relate a process sequence to the electrical performance of devices fabricated using this process. This capability can provide the basis for optimizing the performance of individual devices and ultimately the circuits incorporating these devices.

#### 2.1.1. Process Modeling

Integrated-circuit processing steps can be classified into three categories: thermal processing and doping, pattern definition, and pattern transfer. The thermal processing and doping steps include ion implantation, oxidation, epitaxial growth, and annealing. Various etching processes, such as wet chemical etching, plasma etching, and reactive ion etching, and deposition processes, such as CVD and evaporation, are classified as pattern definition. Pattern transfer processing includes optical, x-ray, electron-beam, and ion-beam lithography methods.

Process simulation involves the solution of physical equations for the processing steps needed to fabricate complete device structures. Modeling of the diffusion process is given here as an example. The problem of calculating the impurity profiles in semiconductor devices is that of the transport and redistribution of charged particles in the semiconductor crystal lattice. The processing steps that introduce and redistribute the impurities in selected regions alter the boundaries of the material layers in the device. The problem of calculating the change in these boundaries is that of keeping track of various material layers and their deformations due to the processing steps to which they are subjected.

Let (x,y,t) be the set of two spatial variables and time. Figure 2-1 shows a sample simulation region where x is the coordinate along the depth direction and y is the coordinate along a lateral direction. Two different material layers

Figure 2-1 A selective region for process modeling and simulation.

(oxide and nitride) are depicted on top of the silicon substrate. The nitride layer forms a mask which blocks impurities and retards oxidation locally under the mask. The silicon-oxide interface is defined by x=B(y,t) and the top surface of the oxide is defined by x=T(y,t). Assume that there are m impurities present in the silicon. The continuity equation governs the transport of the ith impurity,

$$\frac{\partial C_i}{\partial t} = \operatorname{div} \mathbf{J_i}$$

$$= \nabla (\mathbf{D_i} \nabla C_i + \mathbf{Z_i} \mu_i \mathbf{N_i} \mathbf{E})$$

(2.1)

where  $C_i = C_i(x, y)$  and  $J_i$  are the concentration and the flux of the ith impurity, respectively,  $D_i$  is the concentration-dependent diffusion coefficient,  $Z_i$  and  $\mu_i$  are the charge state and the mobility of the impurity, respectively,  $N_i$  is the electrically active concentration, and E is the electric field.

#### 2.1.2. Simulation Tools

The use of computer programs to calculate the impurity profile in semiconductor devices has become a routine part of IC device design and process development since the availability of SUPREM [2.1-2.4] from Stanford University. Beginning with SUPREM-I and proceeding to SUPREM-II, each version has drawn from the models and physical understanding of fabrication processes then available.

The third generation SUPREM-III substantially upgrades the simulation capability. New and more accurate models for oxidation, diffusion, epitaxy, and ion implantation are included. Types of processing steps simulated by SU-PREM-III include inert ambient drive in, oxidation of silicon and silicon-nitride, ion implantation, epitaxial growth of silicon, and low temperature deposition or etching of various materials. SUPREM-III simulates in one dimension the changes in a semiconductor structure as a result of the various processing

steps. The primary results of interest are the thickness of the structure and the distribution of impurities within those layers. The program also determines certain material properties such as polysilicon grain size and the sheet resistivity of diffused regions in silicon layers.

SUPREM-I, -II, and -III are essentially simulators which emphasize one-dimensional (1D) physical kinetic models. The new SUPREM-IV incorporates oxidation, ion implantation, and diffusion models in two-dimensional (2D) format. SUPREM-3.5 [2.5] was recently developed to simulate processes used to manufacture ion implanted GaAs devices. The process models in SUPREM-3.5 include ion implantation, diffusion, and activation.

SUPRA [2.6] is a two-dimensional process simulator which uses approximations in many cases to keep execution times low. It is therefore more difficult to obtain quantitative results with SUPRA than with SUPREM. It is used, however, for modeling structures that can not be treated with SUPREM and when only qualitative results are required.

BICEPS [2.7] is a comprehensive two-dimensional process simulation program developed at AT&T Bell Laboratories. BICEPS can accommodate the various processing steps of ion implantation, predeposition, oxidation, and epitaxy in one or two spatial dimensions as well as etching and deposition of oxide, nitride, photoresist, and polysilicon. One unique feature of BICEPS is that the boundary variations of the material layers of the device structure are calculated along with the impurity profiles in a consistent manner.

The simulation of optical lithography was pioneered by the SAMPLE program [2.8,2.9] at the University of California, Berkeley. Simulation has been particularly successfully in the development of proximity effect correction technique in electron-beam lithography. The simulation of etching and deposition is probably the least developed area in IC process simulation due to the complexity of the chemistry and physics of a variety of continually evolving techniques. The SAMPLE program models some of these steps based on empirical functions.

#### 2.2. Device-Level CAD Tools

Numerical device simulators are extensively used to study device electrical phenomena which can not be easily formulated by analytical expressions. The simulation results provide a lot of insight into the underlying physics of the device operations. For MOS transistors, two-dimensional effects, such as short-channel and narrow-width effects, are significant as the device sizes scale down. Detailed and accurate analysis of these effects require 2D simulations to help understand the device physics of small-geometry transistors. CMOS latchup phenomena, hot carrier effects, and bipolar effects such as base-width modulation and base pushout, are often characterized using 2D simulators.

A device simulator is quite useful in the VLSI device development. Various device design options can be simulated and the design with the desired electrical characteristics is selected from these options. The process simulation and device simulation can be linked to allow process parameters and layout to be tailored to optimize device performance.

#### 2.2.1. Semiconductor Equations

Device simulations involve the solution of a system of semiconductor equations over a spatial grid. Basically, there are three fundamental equations involved in the device simulation: Poisson's equation and continuity equations for electrons and holes. The Poisson's equation relates the electrostatic potential to the total charge density in the semiconductor,

$$\Psi = -\frac{\rho}{\varepsilon_{\rm c}} \quad . \tag{2.2}$$

The electric field is the gradient of the electrostatic potential,

$$E = -\nabla \psi. \tag{2.3}$$

The total charge density is expressed as

$$\rho = q(p - n + N) \tag{2.4}$$

where N=N<sub>D</sub><sup>+</sup> - N<sub>A</sub><sup>-</sup> is the electrically active net impurity concentration, and p and n are the electron and hole carrier concentrations, respectively.

$$J_{n} = q \mu_{n} n E + q D_{n} \nabla n, \qquad (2.5)$$

$$J_{p} = q \mu_{p} n E - q D_{p} \nabla p$$

(2.6)

where  $\mu_n$  and  $\mu_p$  are electron and hole mobilities, respectively, and  $D_n$  and  $D_p$  are electron and hole diffusivities, respectively. The carrier densities are related to the electrostatic potential by the Boltzmann approximation,

$$n = n_i \exp\left[\frac{q(\psi - \phi_F)}{kT}\right], \qquad (2.7)$$

$$p = p_i \exp\left[\frac{q(\phi_F - \psi)}{kT}\right]$$

(2.8)

where  $n_i$  is the intrinsic carrier concentration and  $\phi_F$  is the Fermi potential in equilibrium. Under nonequilibrium condition, the carrier concentrations can be expressed using quasi-Fermi potential  $\phi_n$  and  $\phi_p$  as

$$n = n_i \exp\left[\frac{q(\psi - \phi_n)}{kT}\right], \qquad (2.9)$$

$$p = p_i \exp\left[\frac{q(\phi_p - \psi)}{kT}\right]. \tag{2.10}$$

The current continuity equations for electrons and holes are given by

$$\frac{\partial n}{\partial t} = \frac{1}{q} \nabla J_n + G - R, \qquad (2.11)$$

$$\frac{\partial \mathbf{p}}{\partial t} = -\frac{1}{\mathbf{q}} \nabla \mathbf{J}_{\mathbf{p}} + \mathbf{G} - \mathbf{R} . \tag{2.12}$$

The term G incorporates generation phenomena, such as impact ionization or radiation-induced carrier generation and the term R includes Shockley-Read-

Hall and Auger recombination processes.

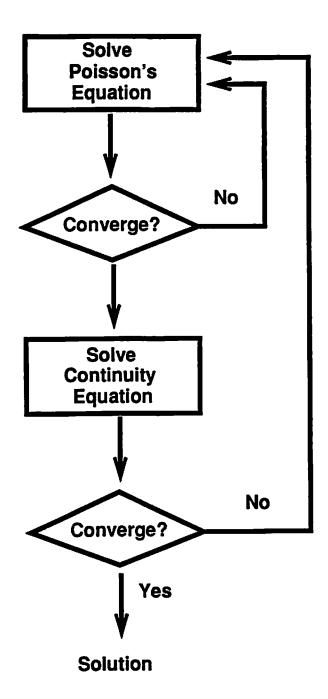

Two techniques are used to solve the coupled set of equations (2.2), (2.11) and (2.12): Newton's method and Gummel's method. The Newton's direct method applies to the three equations (2.2), (2.11), and (2.12) coupled over all space. The Gummel's iterative method applies sequentially to the individual equations. The flowcharts of these two methods are shown in Figures 2-2 and 2-3, respectively. The Gummel's method has major storage advantages and superior execution speeds for bias levels where the equations are not guaranteed. In contrast, the direct solution of the coupled equations using the Newton's method results in more costly solutions at lower biases but guarantees convergence at high bias levels.

#### 2.2.2. Simulation Tools

PISCES-II [2.10] is a two-dimensional semiconductor device modeling program which simulates the electrical behavior of devices under steady-state or transient conditions. PISCES-II can analyze physical structures with completely arbitrary geometries (nonplanar as well as planar) with general doping profiles. A wide variety of materials and physical models are incorporated.

The device simulator MINIMOS [2.11] was developed at the University of Vienna, Austria. It can be operated in a hierarchy of levels. MINIMOS's major advantages are its speed and user friendliness. It is however limited to modeling conventional MOS structures.

#### 2.3. Circuit-Level CAD Tools

Integrated circuit design is a complex task as the level of integration increases. Circuit simulation programs are important computer-aided design tools for the analysis of the electrical performance of integrated circuits. Circuit designers can verify their new designs simply by computer simulations and they can modify their designs until the specifications of the circuit performance is achieved. Circuit simulation programs can perform a variety of anal-

Figure 2-2 Flowchart of the Newton's method.

Figure 2-3 Flowchart of the Gummel's method.

yses, including dc, ac, and time-domain transient analyses of circuits containing a wide range of nonlinear active circuits.

#### 2.3.1. Equation Formulation

Computer simulation of an electronic circuit involves the numerical analysis of mathematical models of the circuit. The circuit is modeled as an interconnection of branches. Each circuit element is associated with a branch and is modeled in mathematical expressions. Each branch is connected between two nodes and characterized by a branch-constituent relation. There are two types of branches: current-defined branch and voltage-defined branch. A branch is current-defined if the branch current is defined in terms of circuit parameters and circuit variables.

$$I_{h} = f(x) \tag{2.13}$$

where x is the vector of branch voltages and branch currents. In a voltage-defined branch, the branch voltage is defined in terms of circuit parameters and circuit variables.

$$V_{h} = f(x) \tag{2.14}$$

where x is the vector of branch voltages and branch currents. Examples of current-defined branches include independent and controlled current-sources, capacitors, and most branches embedded in semiconductor device models. Examples of voltage-defined branches include independent and controlled voltage sources, inductors, and transmission lines. The resistor is an element which can be modeled either as a voltage-defined branch or as a current-defined branch.

In general, branch-constituent relations are nonlinear, time-dependent, and may involve the time derivative operation. Therefore, the determination of node voltages and branch currents of a circuit generally involve solving a system of nonlinear, time-dependent differential equations of the form,

$$G(\mathbf{x}) = 0 \tag{2.15}$$

where x is the vector of unknown circuit variables.

#### 2.3.2. Simulation Tools

The SPICE program [2.12,2.13] is the most widely used circuit simulation program for IC design. A lot of circuit simulation programs used in the IC industry and universities are variations of the SPICE program. SPICE is a general-purpose circuit simulation program for nonlinear dc, nonlinear transient, and linear ac analyses. A circuit may contain resistors, capacitors, inductors, mutual inductors, independent voltage and current sources, four types of dependent sources, transmission lines, switches, and five most common semiconductor devices: diodes, BJT's, MESFET's, JFET's, and MOSFET's. SPICE has built-in models for the semiconductor devices, and the users need to specify only the pertinent model parameter values.

#### 2.4. Equipment Modeling

One new class of CAD tools for manufacturing requires fabrication equipment modeling. The equipment models are used to predict the performance of the factory, such as performance and throughput. Some work has been done on reactive ion etching, rapid thermal processing, and sputtering. Research in several universities is being conducted on the physical understanding of the equipment dynamics. More work on equipment and process modeling and characterization will lead to improved fundamental understanding, better capability for closed-loop process control, and improved equipment design.

## Chapter 3

## **Integration of Technology CAD Tools**

Integrated-circuit technology has progressed with a rapid pace over the past two decades. In the VLSI era, device feature sizes are scaled down to the submicron range and IC chips with component counts more than 10<sup>7</sup> have been in large-volume production. With increasing integration level and complexity of VLSI circuits, the development time and cost for a new VLSI technology tend to increase enormously. The huge manpower and cost spent on the process development for standard circuits are compensated by the large profits earned from high-volume production. Recently, application-specific integrated circuits (ASICs) have emerged as a very important type of IC products in the market [3.1]. It is essential for IC manufacturing companies to adopt new strategies for process development in order to remain highly competitive in this new market.