# **USCIPI REPORT #203**

**VLSI Image Compression**

by

Wai-Chi Fang

May 1992

Signal and Image Processing Institute UNIVERSITY OF SOUTHERN CALIFORNIA

Department of Electrical Engineering-Systems 3740 McClintock Avenue, Room 404 Los Angeles, CA 90089-2564 U.S.A.

### Acknowledgments

I would like to express my deepest gratitude to Professor Bing J. Sheu, my research adviser, for his constant guidance and encouragement throughout the course of my Ph.D. research work. I wish to extend my sincere appreciation to Professor Irving S. Reed and Professor Dominic Cheung for serving on my dissertation committee. I would also like to thank them along with Professor Rama Chellappa and Professor B. Keith Jenkins for serving on my qualifying examination committee.

I am very grateful to Professor Hans H. Kuehl, Chairman of EE-Electrophysics Department; Professor Melvin A. Breuer, Chairman of EE-Systems Department; Professor Leonard Silverman, Dean of Engineering School; and Mrs. Ramona Gordon, Senior Administrative Assistant, for providing me the opportunity to pursue my Ph. D. studies under such a great research environment at USC. Encouragement from Professor Jerry M. Mendel, Director of Signal and Image Processing Institute (SIPI); Professor Mike Arbib, Director of Center for Neural Engineering (CNE); Professor Ramakant Nevatia, Director of Institute for Robotics and Intelligent Systems (IRIS); Professor Stephen R. Forrest, Director of National Center for Integrated Photonic Technology (NCIPT) has been very helpful. Assistance from Mr. Cesar Pina, Director of the MOSIS Service and other members of USC/Information Sciences Institute at Marina del Rey, CA is also highly appreciated.

I would like to thank Professor Sun-Yuan Kung of Princeton University, while he taught at USC, on VLSI array processors. Valuable discussions with my colleagues at Jet Propulsion Laboratory, especially Dr. Chi-Yung Chang and Dr. John C. Curlander on radar imagery compression, Dr. Jun-Ji Lee and Mr. Robert Rice on lossless data compression are very fruitful. I greatly enjoyed discussion with Professor B. Keith Jenkins and Dr. Chein-Hsun Wang on artificial neural networks, Dr. Yi-Tong Zhou and Professor Rama Chellappa on optical flow computing.

I would like to thank my fellow graduate students in the VLSI Signal Processing Laboratory for their constant discussions and friendships. I appreciate Dr. Bang Won Lee, Dr. Ji-Chien Lee, and Dr. Wen-Jay Hsu for discussions on VLSI neural chip design. I thank Oscal T.-C. Chen for his valuable contribution to the software simulation. I also thank Joongho Choi, Ms. Chia-Fen Chang, Ms. Min Chen, Sudhir Gowda, and Sa Hyun Bang for the circuit simulation and layout.

I wish to thank many people in Jet Propulsion Laboratory, California Institute of Technology; especially Dr. Edward C. Stone, Director; Dr. Charles Elachi, Assistant Laboratory Director; Dr. William J. Weber, Manager of Telecommunications Science and Engineering Division; Dr. Fuk K. Li, Manager of Radar Science and Engineering Section; Mr. D. Eisenman, Mr. R. H. Nixon, Mrs. Mimi Paller, and Mrs. Barbara Cline, for their encouragement and assistant. I am grateful for the tuition support and the Profession Development Program provided by Jet Propulsion Laboratory.

Finally, I would like to dedicate this work to my wife, Tsuey-Yuh, our children, Annie, Sonia, and Jonathan, my parents, Chung-Hsun Fang and Su-Yueh Lin Fang, and my parents-in-law, Jong-Tang Huang and Han-Hsiao Liao Huang, for their love, understanding, patience, support during my doctoral studies. The constant prayers of my mother and the cheerful faces of my children greatly help me to complete my Ph.D. studies.

This research has been performed since Summer 1989 while I keep a full-time position at Jet Propulsion Laboratory. The Interactive Television Program at the School of Engineering has been extremely valuable for most of my course work. The research was partially supported by DARPA under Contract No. MDA972-90-C-0037 and by Faculty Research and Innovation Fund No. 22-1502-9759 to Professor Bing J. Sheu from University of Southern California and Contributions from TRW, Inc., Samsung Electronics Co. and NKK Corp.

# **Table of Contents**

| Acknowled     | lgment | ts                                             | ii   |

|---------------|--------|------------------------------------------------|------|

| List of Figu  | res    |                                                | ix   |

| List of Table | es     |                                                | xiv  |

| Abstract      |        | •••••••••••••••••••••••••••••••••••••••        | xv   |

| Chapter 1     | Intro  | oduction                                       | 1    |

|               | 1.1    | Motivation                                     | 1    |

|               | 1.2    | Scope and Objective                            | 4    |

|               | 1.3    | Approach: An Integrated Study of VLSI Image    |      |

|               |        | Compression                                    | 4    |

|               | 1.4    | Overview of the Dissertation                   | 8    |

| Chapter 2     | Data   | and Image Compression                          | 18   |

|               | 2.1    | Lossless Compression                           | 18   |

|               | 2.2    | Lossy Compression                              | 20   |

|               |        | 2.2.1 Prediction Coding                        | 20   |

|               |        | 2.2.2 Block Truncation Coding Algorithm        | 21   |

|               |        | 2.2.3 Transform Coding Algorithm               | 22   |

|               |        | 2.2.4 Vector Quantization Algorithm            | 22   |

|               |        | 2.2.5 Summary of Results                       | 23   |

|               | 2.3    | Neural Networks for Data and Image Compression | on24 |

|               |        | 2.3.1 Associative Memory                       | 25   |

|               |        | 2.3.2 Multi-layer Perceptron                   |      |

|               |        | 2.3.3 Hierarchy Associative Memory             | 26   |

|               |        | 2.3.4 Winner-Take-all Competitive Network      |      |

|               |        | 2.3.5 Kohonen's Self-Organizing Feature Maps   | 27   |

|               |        | 2.3.6 Grossberg's Adaptive Resonance Theory    |      |

|               |        | Network                                        | 30   |

|           | 2.4  | Conc   | lusion                                      | 34 |

|-----------|------|--------|---------------------------------------------|----|

|           | Refe | rences | •••••••••••••••••••••••••••••••••••••••     | 34 |

| Chapter 3 | A Hi | gh-Spe | ed VLSI Systolic Vector Quantizer for Image |    |

| _         | Data | Comp   | ression                                     | 41 |

|           | 3.1  | Intro  | duction                                     | 41 |

|           | 3.2  | Vecto  | or Quantization                             | 43 |

|           |      | 3.2.1  | Full-Searched Vector Quantization           | 43 |

|           |      | 3.2.2  | Tree-Searched Vector Quantization           | 44 |

|           |      | 3.2.3  | Binary Tree-Searched Vector Quantization    | 45 |

|           |      | 3.2.4  | Vector Quantization Algorithm Trade-Offs    | 46 |

|           | 3.3  | Systo  | lic Architecture for Vector Quantization    | 47 |

|           |      | 3.3.1  | Systolic Architecture for Full-Searched     |    |

|           |      |        | Vector Quantization                         | 47 |

|           |      | 3.3.2  | Systolic Architecture for Tree-Searched     |    |

|           |      |        | Vector Quantization                         | 50 |

|           |      | 3.3.3  | Systolic Architecture for Binary Tree-      |    |

|           |      |        | Searched Vector Quantization                | 51 |

|           |      | 3.3.4  | Systolic Architecture for Binary Tree-      |    |

|           |      | 1      | Searched Vector Quantization with           |    |

|           |      |        | Difference Codebook                         | 52 |

|           |      | 3.3.5  | Comparisons for Various Systolic VQ         |    |

|           |      |        | Schemes                                     | 54 |

|           | 3.4  | Array  | Processors Design for Binary Tree-Searched  |    |

|           |      | Vecto  | or Quantization                             | 54 |

|           |      | 3.4.1  |                                             |    |

|           |      |        | Design                                      | 55 |

|           |      | 3.4.2  | Design of Systolic Difference-Codebook      |    |

|           |      |        | Binary Tree-Searched VQ                     | 56 |

|           | 3.5  | VLSI   | Implementation                              |    |

|           | 3.6  |        | bility and Fault Tolerance Design           |    |

|           | 3.7  |        | m Simulation Results                        |    |

|           |                                                      | 3.7.1    | Algorithm for Constructing Codebook           | 62  |  |

|-----------|------------------------------------------------------|----------|-----------------------------------------------|-----|--|

|           |                                                      | 3.7.2    | Simulation Results                            | 64  |  |

|           | 3.8                                                  | Concl    | lusion                                        | 65  |  |

|           | Refe                                                 | rences   | ***************************************       | 66  |  |

| Chapter 4 | A VI                                                 | LSI Neu  | ral Processor for Image Data Compression      |     |  |

| -         |                                                      |          | Organization Networks                         | 99  |  |

|           | 4.1                                                  | Introd   | duction                                       | 100 |  |

|           | 4.2                                                  | The L    | earning Algorithm                             | 101 |  |

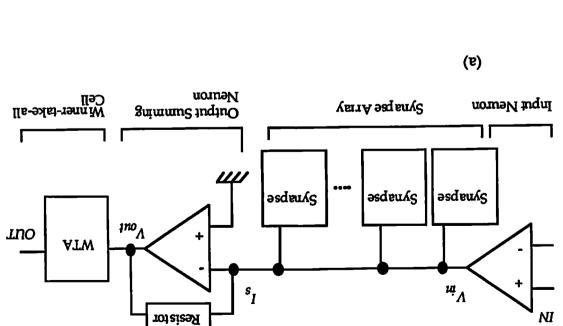

|           | 4.3                                                  |          | Neural Processor Architecture                 |     |  |

|           | 4.4                                                  | Detail   | ed Circuit Implementation                     | 108 |  |

|           |                                                      | 4.4.1    | Input Neuron                                  | 108 |  |

|           |                                                      | 4.4.2    | Programmable Synapse                          | 108 |  |

|           |                                                      | 4.4.3    | Output Summing Neuron                         | 109 |  |

|           |                                                      | 4.4.4    | Winner-Take-All Cell                          | 110 |  |

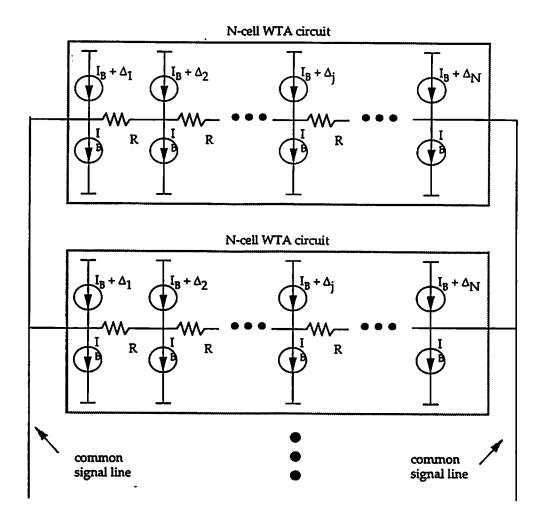

|           |                                                      | 4.4.5    | Analysis of Large Number of Winner-Take-      |     |  |

|           |                                                      |          | All Cells                                     | 111 |  |

|           |                                                      | 4.4.6    | FSO Network                                   | 114 |  |

|           | 4.5                                                  | Testin   | ng of the Neural Network Chip                 | 115 |  |

|           | 4.6                                                  |          | usion                                         |     |  |

|           | App                                                  | endix 4. | A: Analysis of Non-ideal Effects              | 118 |  |

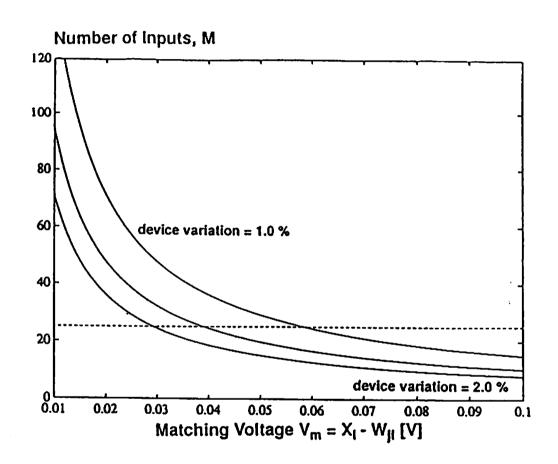

|           |                                                      | 4.A.1    | Effects of Device Variations on the FSO       |     |  |

|           |                                                      |          | Network Dimensionality                        | 118 |  |

|           |                                                      | 4.A.2    | Effects of Parasitic Resistance on the Number |     |  |

|           |                                                      |          | of the WTA Cells                              | 120 |  |

| Chapter 5 | VLSI Neural Network Processor for Optical-Flow Based |          |                                               |     |  |

| •         | Motion Compression                                   |          |                                               | 149 |  |

|           | 5.1                                                  |          | duction                                       |     |  |

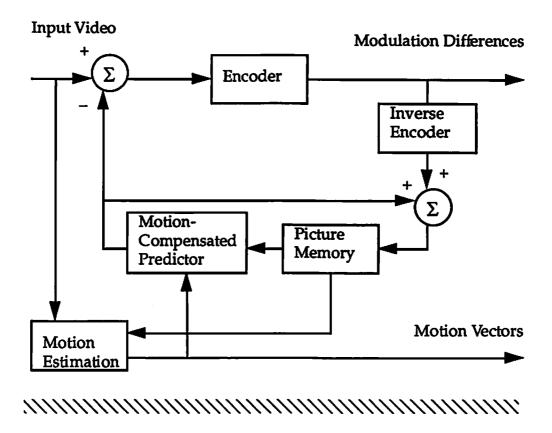

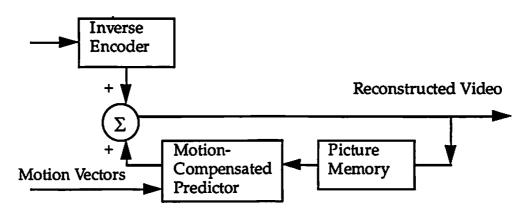

|           |                                                      | 5.1.1    | Motion Estimation and Video Compression.      | 150 |  |

|           |                                                      |          | Optical Flow Estimation                       |     |  |

|           |                                                      |          | Neural Network Applications to Optical        |     |  |

|           |                                                      |          | Flow Computing                                | 152 |  |

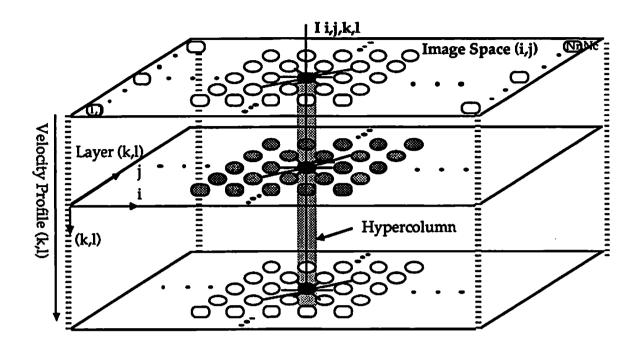

|           | 5.2                                                  | Optic    | al Flow Computing Using Neural Networks       |     |  |

|           | 5.3  | VLSI Optical-flow Neuroprocessors Design160         | 0 |

|-----------|------|-----------------------------------------------------|---|

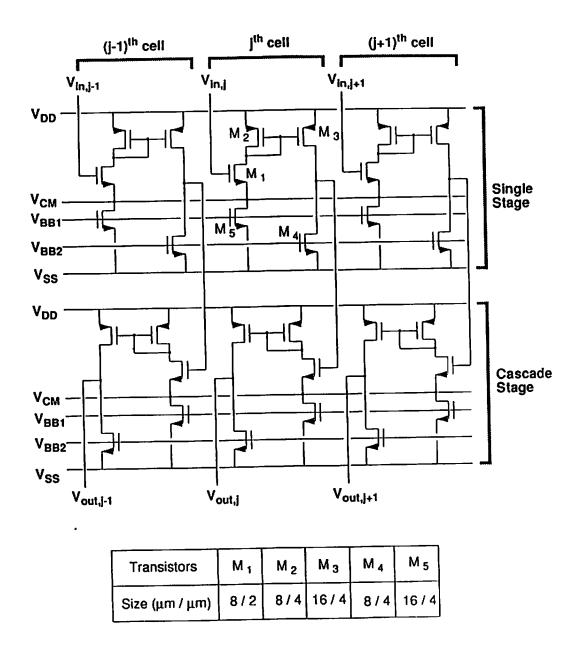

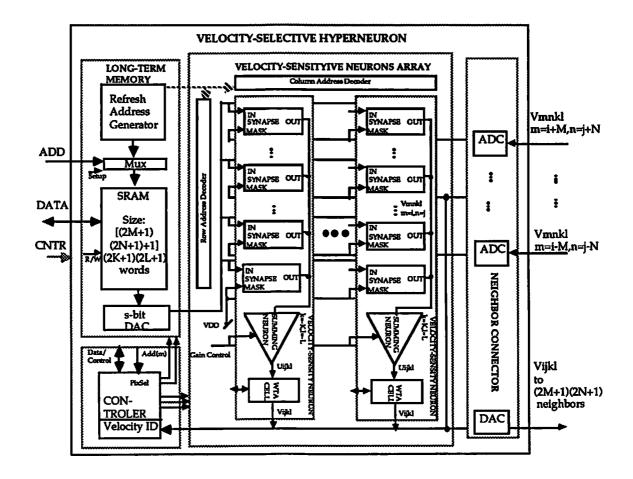

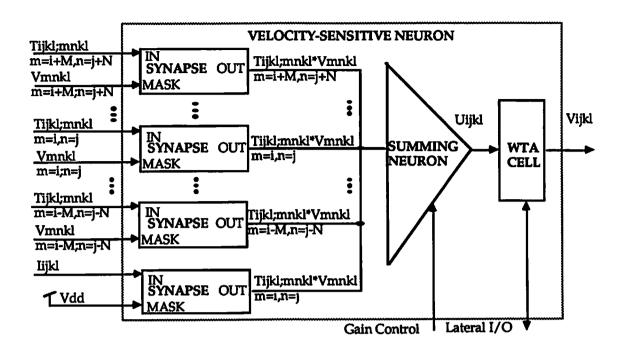

|           |      | 5.3.1 Velocity-sensitive neurons array16            | 1 |

|           |      | 5.3.2 Neighbors Interconnection16                   | 1 |

|           |      | 5.3.3 Digital Co-processor                          | 3 |

|           | 5.4  | Detailed Circuit Implementation164                  | 4 |

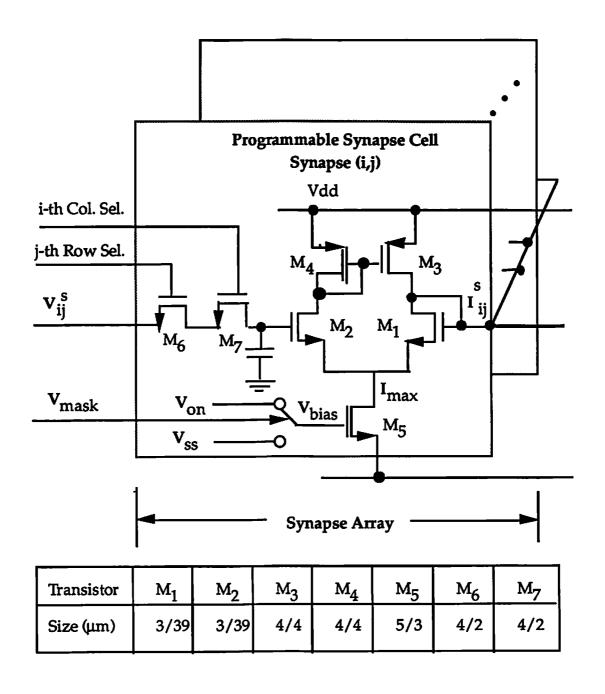

|           |      | 5.4.1 Programmable Synapse164                       | 4 |

|           |      | 5.4.2 Output Summing Neuron165                      | 5 |

|           |      | 5.4.3 Winner-Take-All Cell166                       | 6 |

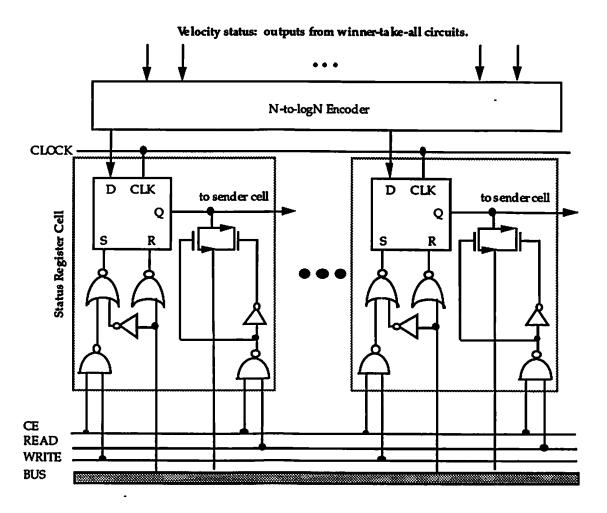

|           |      | 5.4.4 Velocity Status Register162                   | 7 |

|           |      | 5.4.5 Neighbor Interconnection Sender162            | 7 |

|           |      | 5.4.6 Neighbor Interconnection Receiver162          | 7 |

|           | 5.5  | Experimental Results168                             | 8 |

|           |      | 5.5.1 Prototype Chip168                             | 8 |

|           |      | 5.5.2 Chip Performance Measurement169               | 9 |

|           | 5.6  | Optical-flow Neuroprocessor Based System176         | 0 |

|           |      | 5.6.1 System Implementation and Operation170        | 0 |

|           |      | 5.6.2 Hardware Constrained System-Level             |   |

|           |      | Analysis173                                         | 1 |

|           | 5.7  | Conclusion172                                       | 2 |

|           | Refe | rences172                                           | 2 |

| Chapter 6 | High | -Speed VLSI Pipelined Processor Design for Lossless |   |

|           | Imag | e Data Compression195                               | 5 |

|           | 6.1  | Introduction196                                     | 6 |

|           | 6.2  | The Rice Algorithm and Its Performance197           | 7 |

|           |      | 6.2.1 Rice's Universal Noiseless Coding             |   |

|           |      | Technique 197                                       |   |

|           |      | 6.2.2 UNC-PSI14,K+ Algorithm202                     | 2 |

|           |      | 6.2.3 Performance Measurement208                    | 8 |

|           |      | 6.2.4 Experimental Results209                       | 9 |

|           | 6.3  | Design and Implementation of the VLSI PSI14,K+      |   |

|           |      | Encoder21                                           | 1 |

|           |      | 6.3.1 System and Chip Partition21                   | 1 |

| Appendix A | Journ       | nal and Confere | nce Publications                        | 229 |

|------------|-------------|-----------------|-----------------------------------------|-----|

| Chapter 7  | Future Work |                 | 226                                     |     |

|            | 6.5         | Conclusion      | *************************************** | 218 |

|            | 6.4         | The Prototype   | Chip                                    | 217 |

|            |             | 6.3.3 Adaptiv   | e Variable Length Coder                 | 215 |

|            |             | 6.3.2 Preproce  | essor Module                            | 213 |

# List of Figures

| Fig. 1.1  | An end-to-end high rate communication and/or storage        |  |  |  |  |  |

|-----------|-------------------------------------------------------------|--|--|--|--|--|

|           | system with the source and channel coding3                  |  |  |  |  |  |

| Fig. 1.2  | Design methodology for the VLSI image compression           |  |  |  |  |  |

|           | processor7                                                  |  |  |  |  |  |

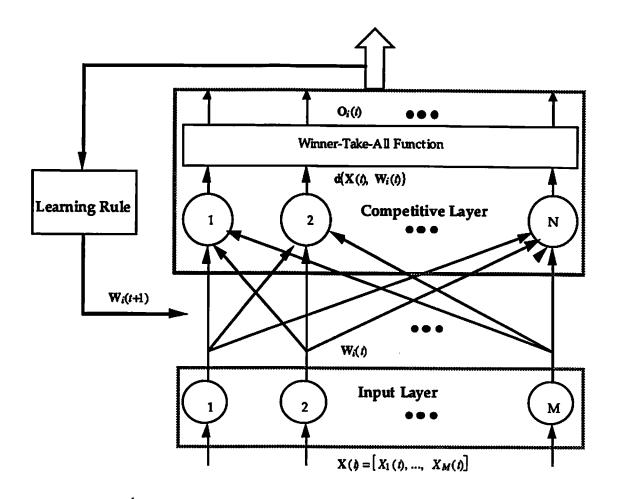

| Fig. 2.1  | Structure of Kohonen's self-organizing feature maps28       |  |  |  |  |  |

| Fig. 2.2  | Structure of VQ using ART33                                 |  |  |  |  |  |

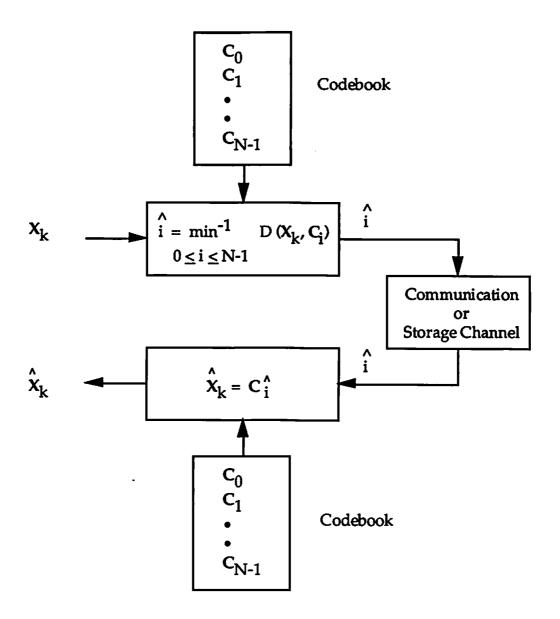

| Fig. 3.1  | Functional block diagram of the vector quantization70       |  |  |  |  |  |

| Fig. 3.2  | Dependence graph of the full-searched vector                |  |  |  |  |  |

|           | quantization algorithm71                                    |  |  |  |  |  |

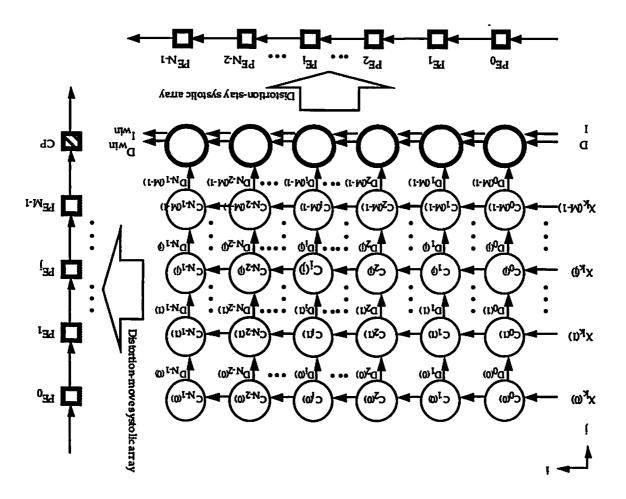

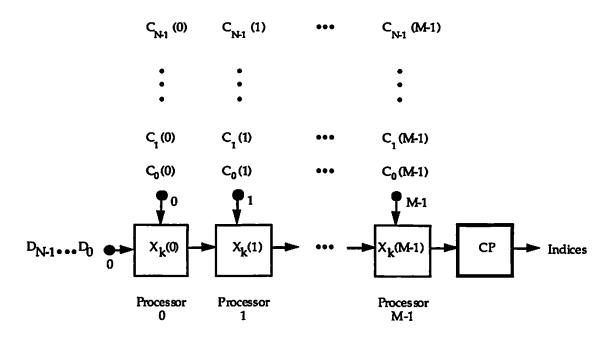

| Fig. 3.3  | Distortion-stay systolic architecture for the full-searched |  |  |  |  |  |

|           | vector quantizer72                                          |  |  |  |  |  |

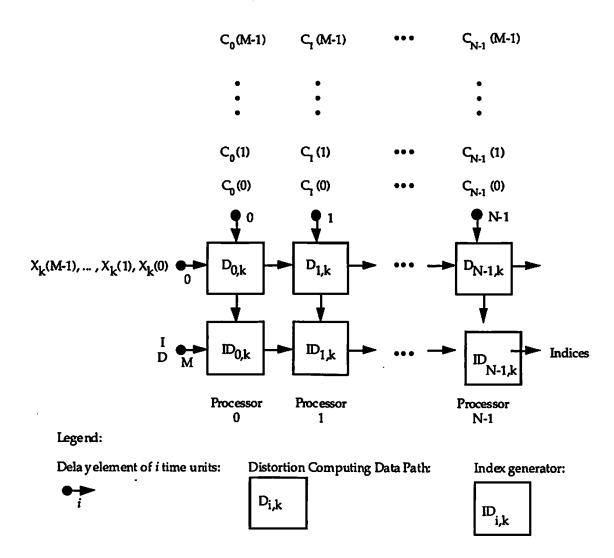

| Fig. 3.4  | Distortion-move systolic architecture for the full-searched |  |  |  |  |  |

| Ü         | vector quantizer73                                          |  |  |  |  |  |

| Fig. 3.5  | Systolic architecture for the tree-searched vector          |  |  |  |  |  |

| Ŭ         | quantizer74                                                 |  |  |  |  |  |

| Fig. 3.7  | Systolic architecture for the binary tree-searched vector   |  |  |  |  |  |

| Ū         | quantizer76                                                 |  |  |  |  |  |

| Fig. 3.8  | System configuration for the difference-codebook BTSVQ77    |  |  |  |  |  |

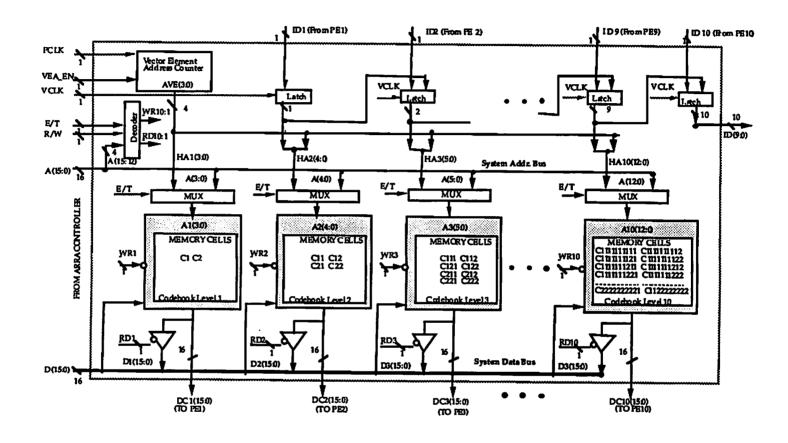

| Fig. 3.9  | Functional block diagram of hierarchical memory banks       |  |  |  |  |  |

| J         | design of the raw-codebook BTSVQ78                          |  |  |  |  |  |

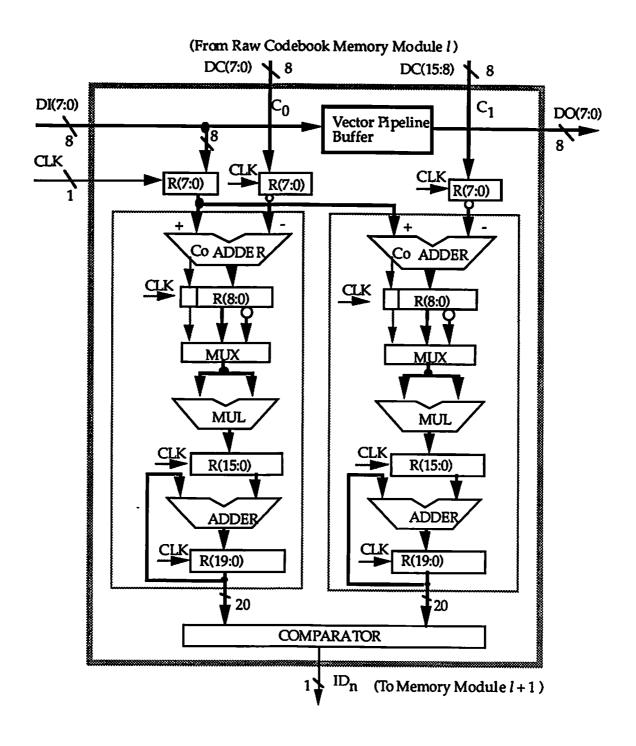

| Fig. 3.10 | Functional block diagram of the raw-codebook PE of the      |  |  |  |  |  |

| 0         | BTSVQ79                                                     |  |  |  |  |  |

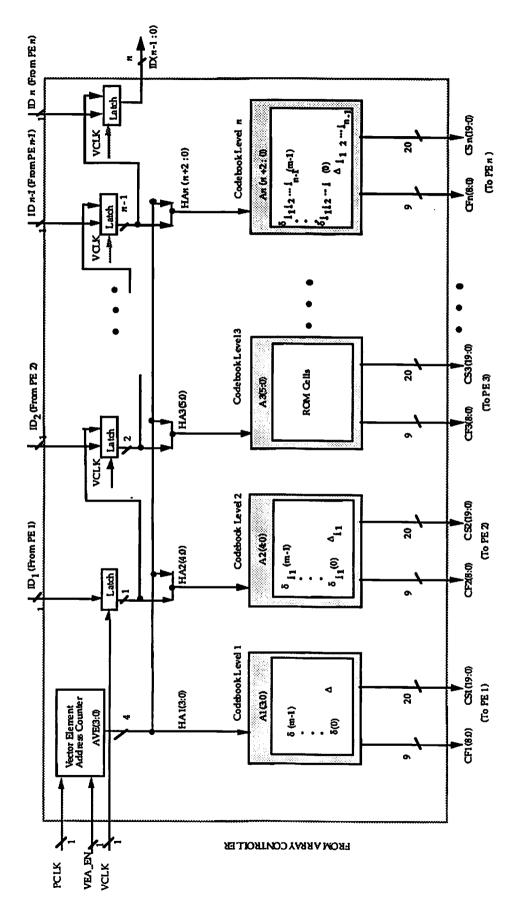

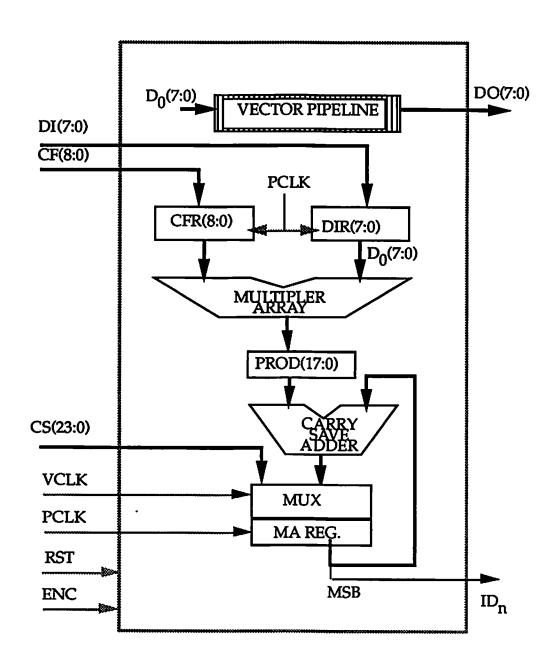

| Fig. 3.12 | Functional block diagram of the PE design of the            |  |  |  |  |  |

|           | difference-codebook BTSVQ81                                 |  |  |  |  |  |

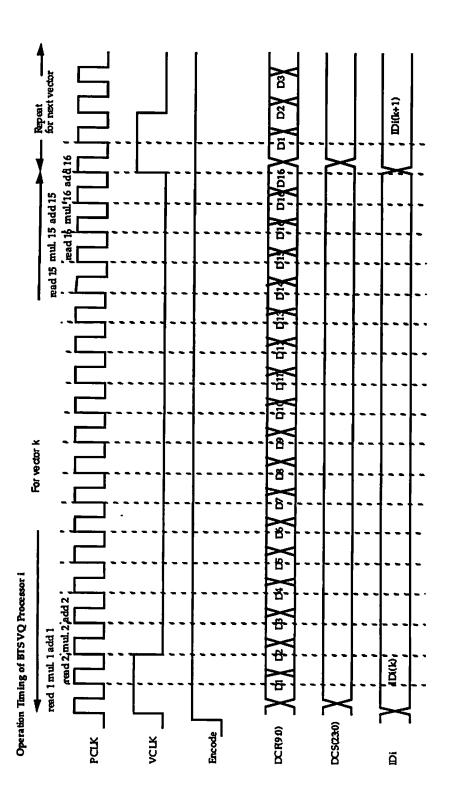

| Fig. 3.13 | Operation timing of the binary tree-searched vector         |  |  |  |  |  |

| 0         | quantizer82                                                 |  |  |  |  |  |

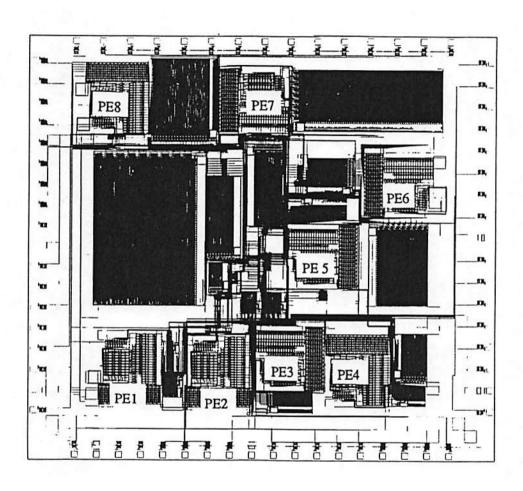

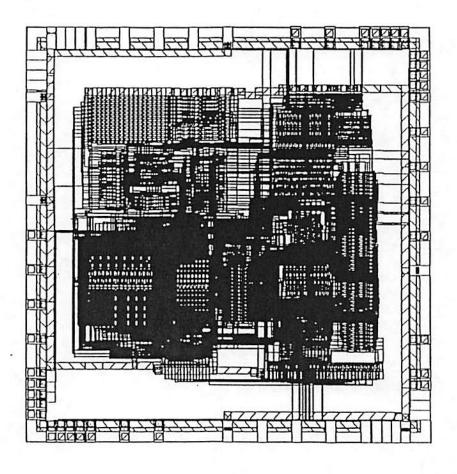

| Fig. 3.14 | A GDS-II layout of the systolic 8-level BTSVQ chip83        |  |  |  |  |  |

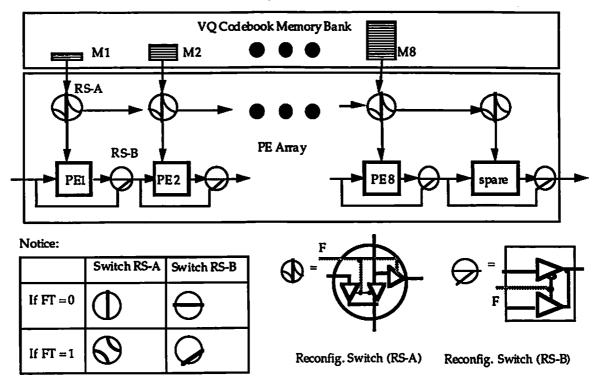

| Fig. 3.15 | Fault-tolerant systolic array architecture of the BTSVQ84   |  |  |  |  |  |

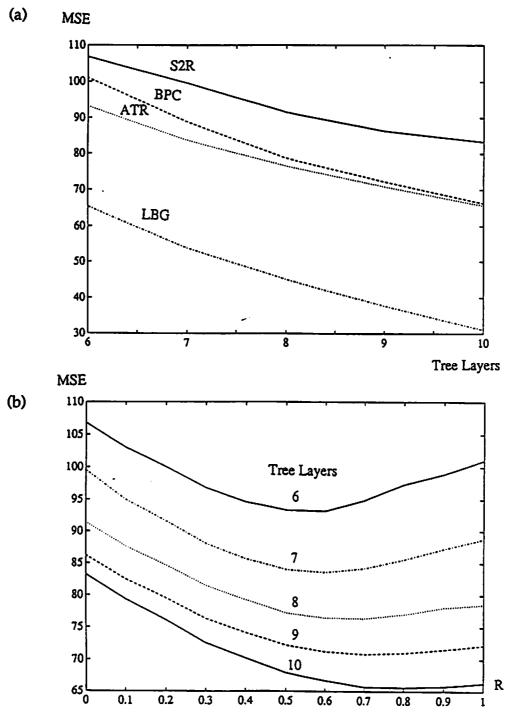

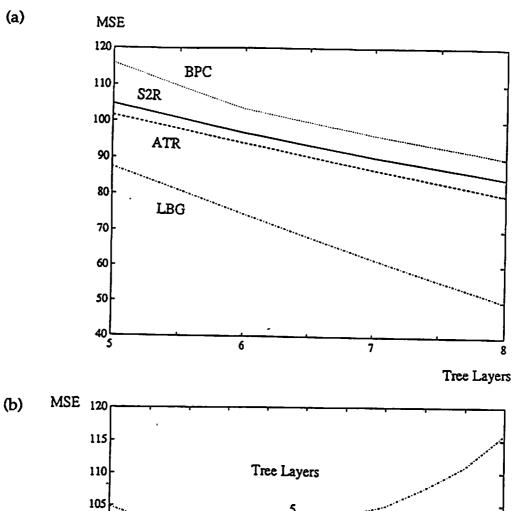

| Fig. 3.16 | (a) MSE vs. tree layer plot of S2R, BPC, ATR, and LBG for a |  |  |  |  |  |

| 6. 0.10   | 4x4 window on the 512x512-pixel 256-gray-level girl image.  |  |  |  |  |  |

|           | (b) MSE of the ATR method with scalar training ratio        |  |  |  |  |  |

|           | (n) when of the way menton with status framing rang         |  |  |  |  |  |

|           | changes from 0 to 185                                                    |

|-----------|--------------------------------------------------------------------------|

| Fig. 3.17 | (a) MSE vs. tree layer plot of S2R, BPC, ATR, and LBG for a              |

|           | 4x4 window on the 256x256-pixel 256-gray-level moon                      |

|           | image.                                                                   |

|           | (b) MSE of the ATR method with scalar training ratio                     |

|           | changes from 0 to 186                                                    |

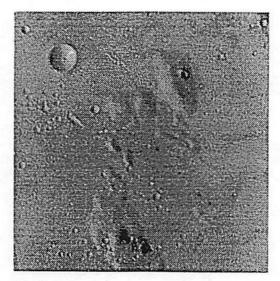

| Fig. 3.18 | (a) The original 256x256-pixel 256-gray-level moon image.                |

|           | (b) The reproduced 256x256-pixel 256-gray-level moon                     |

|           | image using 8-level binary tree-searched vector quantizer                |

|           | and ART method87                                                         |

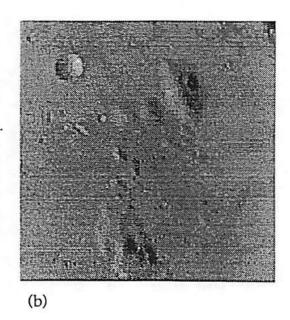

| Fig. 3.19 | MSE of ATR for various windows on the 256x256-pixel                      |

|           | 256-gray-level moon image88                                              |

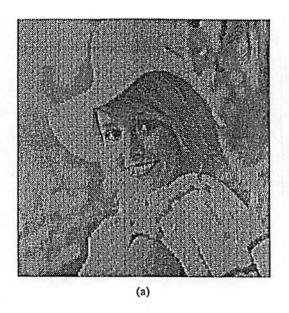

| Fig. 3.20 | Reproduced Girl image by 10-level binary tree-searched                   |

|           | vector quantizer for a $4 \times 4$ window on the 512 $\times$ 512-pixel |

|           | 256-gray-level Girl image89                                              |

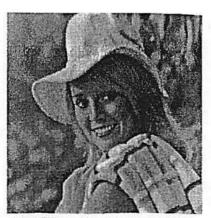

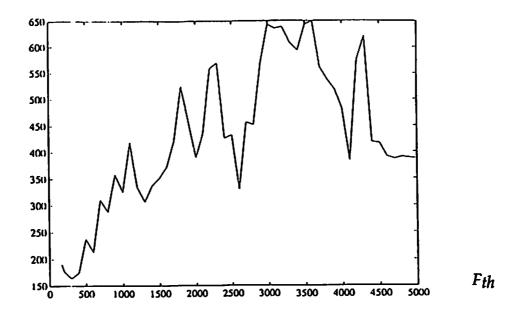

| Fig. 4.1  | Plots of mean-squared errors of image compression versus                 |

|           | the upper-threshold frequency. The one-iteration FSO                     |

|           | method is used for a 6-bit codebook on 5x5 subimage                      |

|           | blocks. (a) SAR Ice image of Beaufort Sea, Alaska127                     |

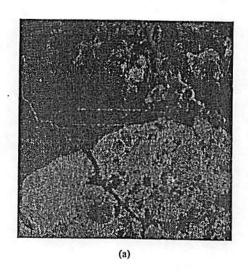

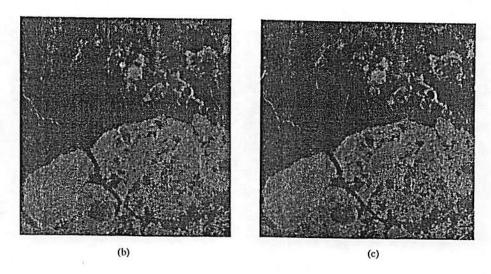

| Fig. 4.2  | Image compression using the FSO method on 5x5                            |

|           | subimage blocks128                                                       |

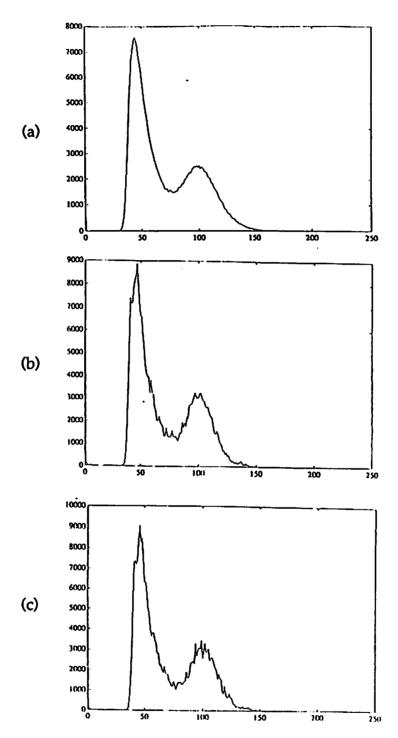

| Fig. 4.3  | Histogram of the 512 x 512-pixel SAR Ice image129                        |

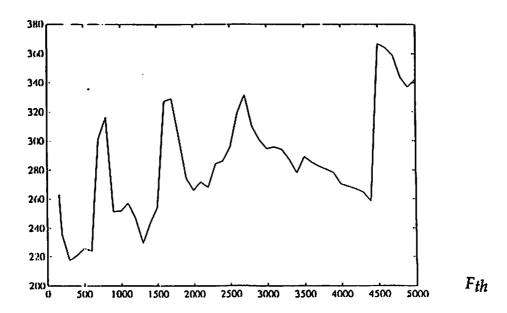

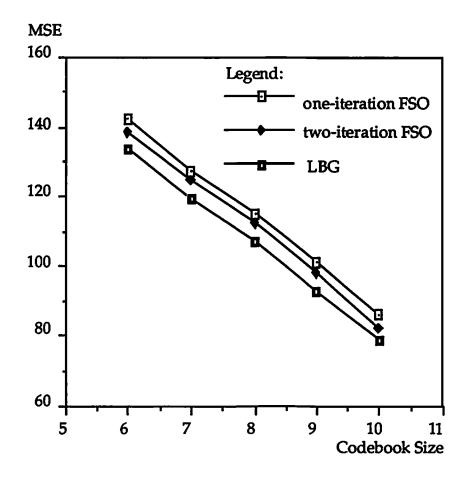

| Fig. 4.4  | Mean-squared errors of image compression using the FSO                   |

|           | method and the LBG method on 5x5 subimage blocks of                      |

|           | the 512 x 512-pixel SAR Ice image130                                     |

| Fig. 4.5  | Adaptive image compression using the FSO method131                       |

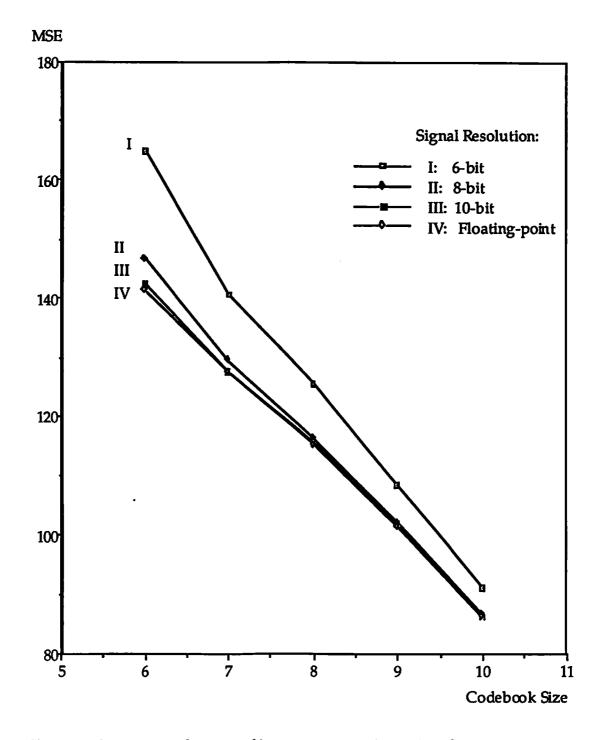

| Fig. 4.6  | Mean-squared errors of image compression using the one-                  |

|           | iteration FSO method for 6-bit, 8-bit, 10-bit, and floating-             |

|           | point resolutions on 5x5-pixel subimage blocks of the                    |

|           | 512x512-pixel SAR Ice image132                                           |

| Fig. 4.7  | The architecture of the FSO neural network133                            |

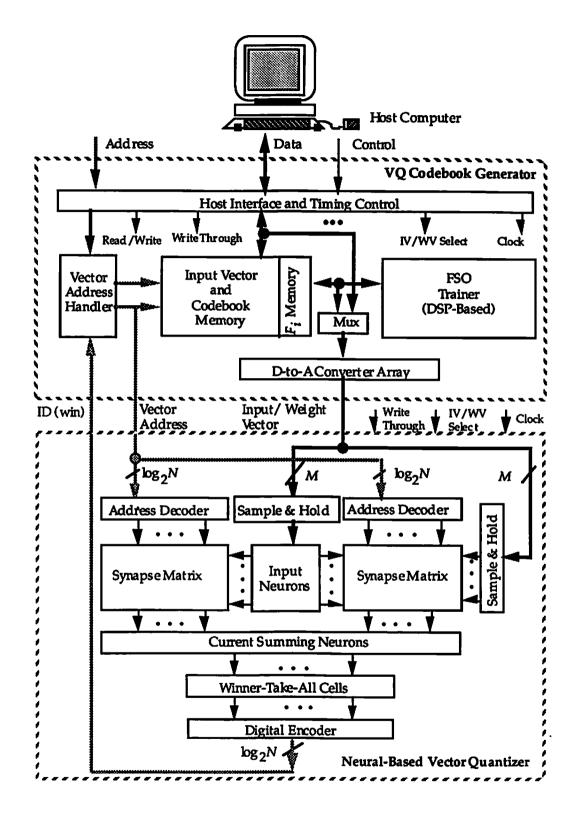

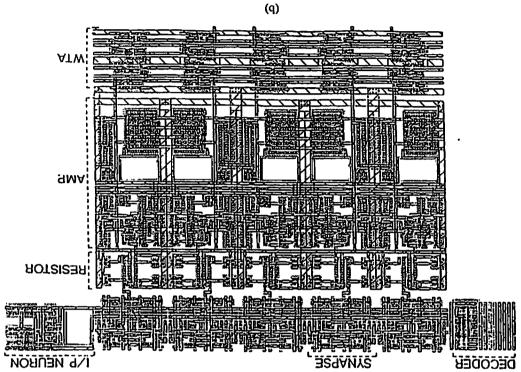

| Fig. 4. 8 | The VLSI neural processor based on the FSO method134                     |

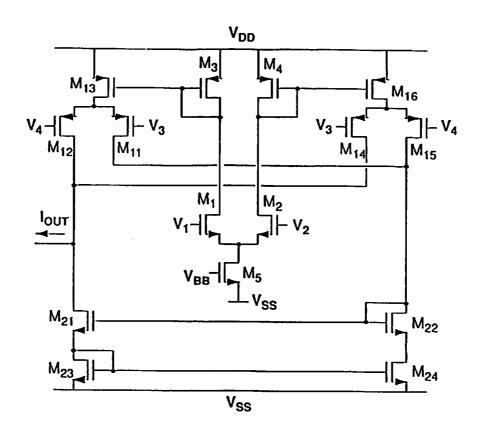

| Fig. 4.9   | Circuit schematic and transistor sizes for the                     |     |  |  |  |

|------------|--------------------------------------------------------------------|-----|--|--|--|

|            | programmable synapse based on Gilbert multiplier                   | 135 |  |  |  |

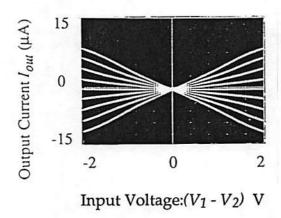

| Fig. 4.10  | Measured synapse output current versus neuron input                |     |  |  |  |

|            | voltage (V1-V2) with different weight voltage values               |     |  |  |  |

|            | (V3-V4): -2.00, -1.00, -0.50, -0.25, 0.00, 0.25, 0.50, 1.00, and   |     |  |  |  |

|            | 2.00 V, from bottom to top                                         | 136 |  |  |  |

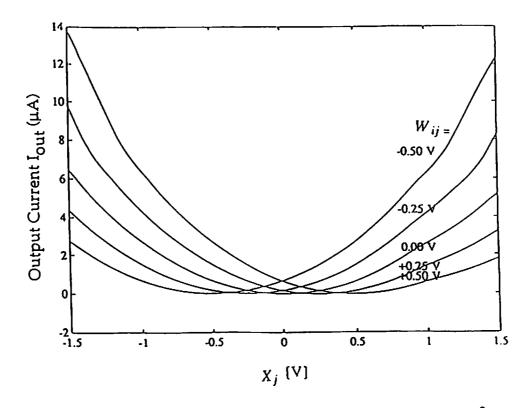

| Fig. 4.11  | Simulated characteristics of the synapse cell for $(X_j-W_{ij})^2$ |     |  |  |  |

|            | computing. Here Xj is applied to V1, V3 and Wij is                 |     |  |  |  |

|            | applied to V2, V4 for the (i,j)th synapse cell                     | 137 |  |  |  |

| Fig. 4.12  | The output neuron.                                                 | 138 |  |  |  |

| Fig. 4.13  | Detailed circuit schematic of the winner-take-all cells            | 139 |  |  |  |

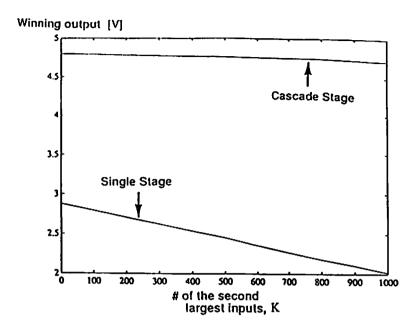

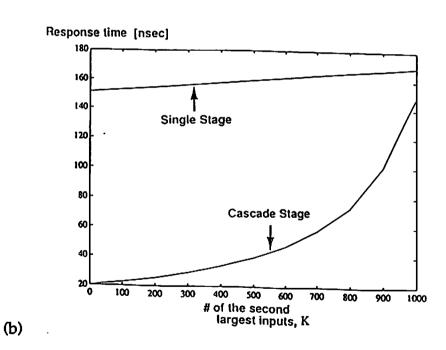

| Fig. 4.14  | Calculation results on a 1000-input WTA with different             |     |  |  |  |

|            | numbers of cells having the second largest input voltage           |     |  |  |  |

|            | value.                                                             | 140 |  |  |  |

| Fig. 4.15  | The FSO network slice.                                             | 141 |  |  |  |

| Fig. 4.16  | The characteristics of the FSO network slice                       | 142 |  |  |  |

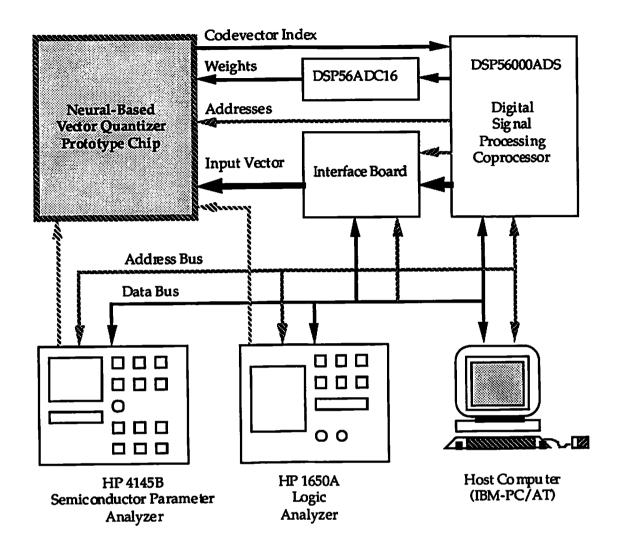

| Fig. 4.17  | Schematic of a dedicated testbed for the neural-based              |     |  |  |  |

|            | vector quantizer chip.                                             | 143 |  |  |  |

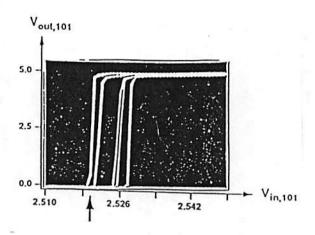

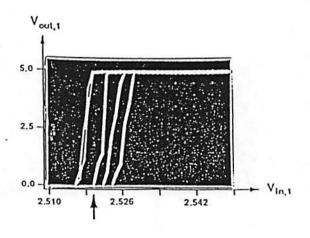

| Fig. 4.18  | Measurement results of a 200-input WTA test structure              | 144 |  |  |  |

| Fig. 4.19  | A die photo of the neural-based vector quantizer                   |     |  |  |  |

|            | prototype chip.                                                    | 145 |  |  |  |

| Fig. 4.20  | Functional testing results for the neural-based vector             |     |  |  |  |

|            | quantizer chip.                                                    | 146 |  |  |  |

| Fig. 4.A.1 | The number of the possible dimensionality versus the               |     |  |  |  |

| •          | matching voltage with different device variations                  | 147 |  |  |  |

| Fig. 4A.   | Simple model of the winner-take-all circuit                        | 148 |  |  |  |

| Fig. 5.1   | A generic motion-compensated predictive video                      |     |  |  |  |

|            | compression encoder.                                               | 175 |  |  |  |

| Fig. 5.2   | A locally connected multi-layer neural network                     | 176 |  |  |  |

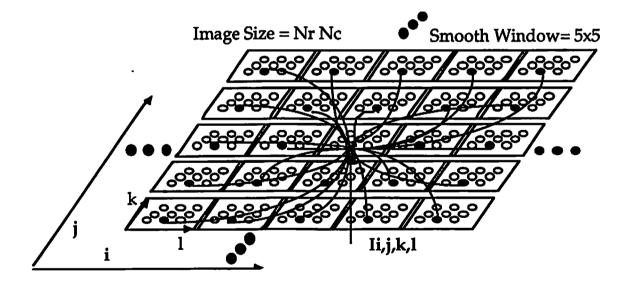

| Fig. 5.3   | A 2-D array neuroprocessors for optical flow                       | 176 |  |  |  |

| Fig. 5. 4  | Functional diagram of the velocity-selective                       |     |  |  |  |

| -          | hyperneuron.                                                       | 177 |  |  |  |

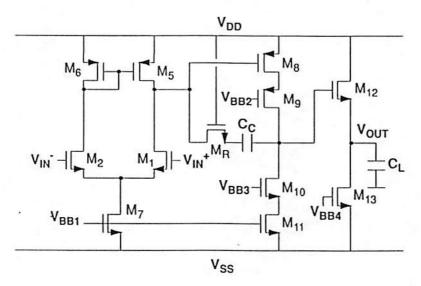

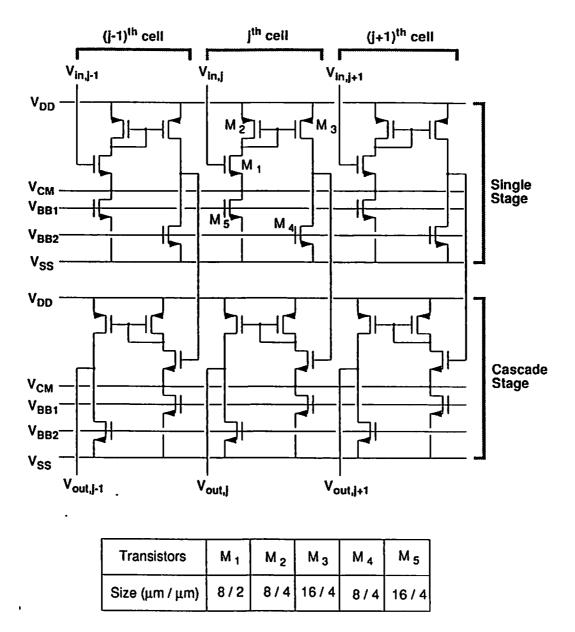

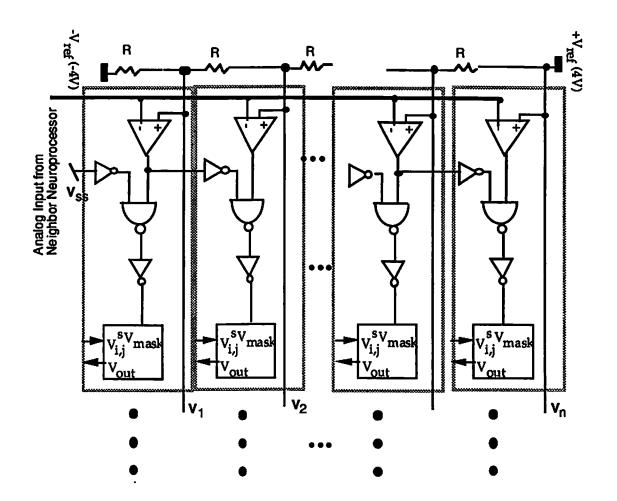

| Fig. 5.5  | Block diagram of the velocity-sensitive neuron178                       |

|-----------|-------------------------------------------------------------------------|

| Fig. 5.6  | Circuit schematic of the programmable synapse cell179                   |

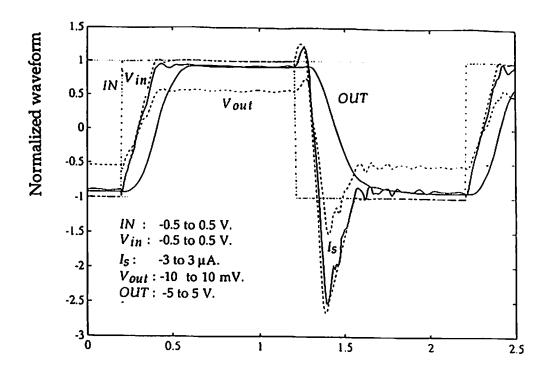

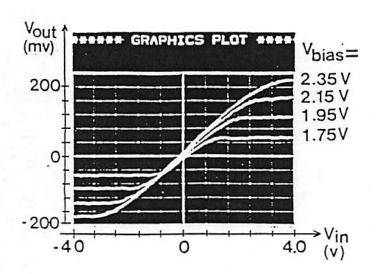

| Fig. 5.7  | A measured DC characteristics of the synapse cell180                    |

| Fig. 5.8  | A circuit diagram and its associated transistor size of the             |

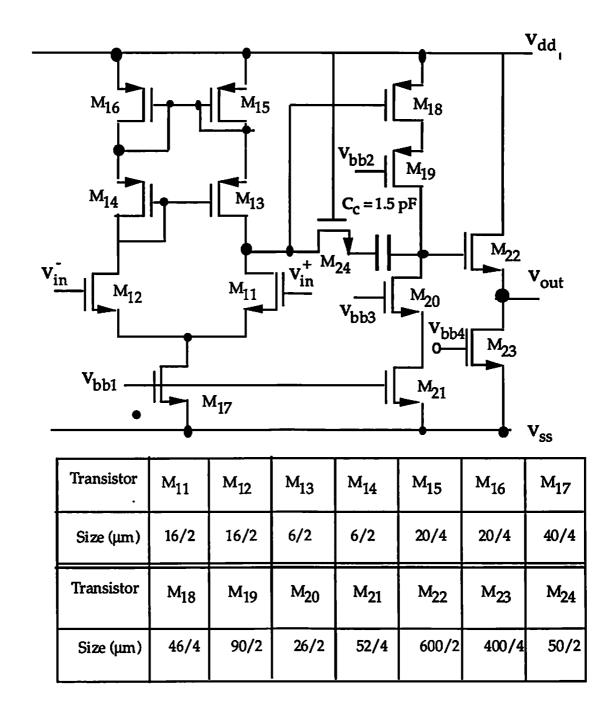

|           | output summing neuron181                                                |

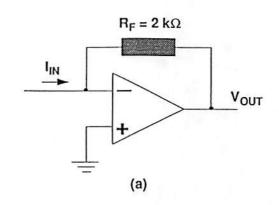

| Fig. 5.9  | A circuit diagram and its associated transistor size of the             |

|           | winner-take-all cell182                                                 |

| Fig. 5.10 | Velocity status register of a hyperneuron that is accessible            |

|           | by the digital co-processor through the digital system bus183           |

| Fig. 5.11 | Neighbor interconnection sender based on a voltage-                     |

|           | scaling digital-to-analog converter184                                  |

| Fig. 5.12 | Neighbor interconnection sender based on a voltage-                     |

|           | scaling analog-to-digital converter185                                  |

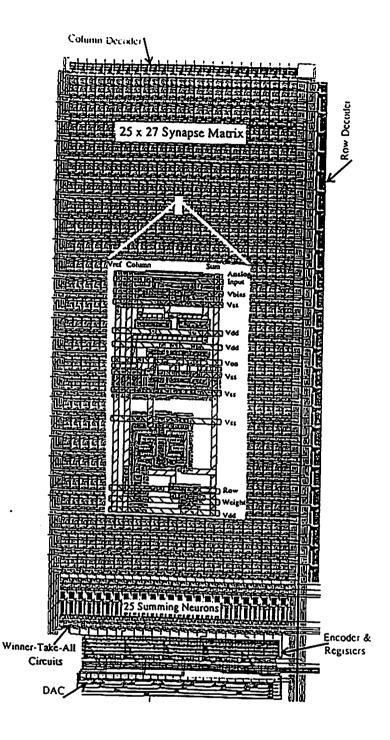

| Fig. 5.13 | The layout of one velocity-selective neuroprocessor. The                |

|           | 25-velocity selective hyperneuron for one image pixel is                |

|           | implemented with a silicon area of 2,482 $\times$ 5,636 $\lambda^2$ and |

|           | contains 25 neurons, 25 x 27 synapse cells186                           |

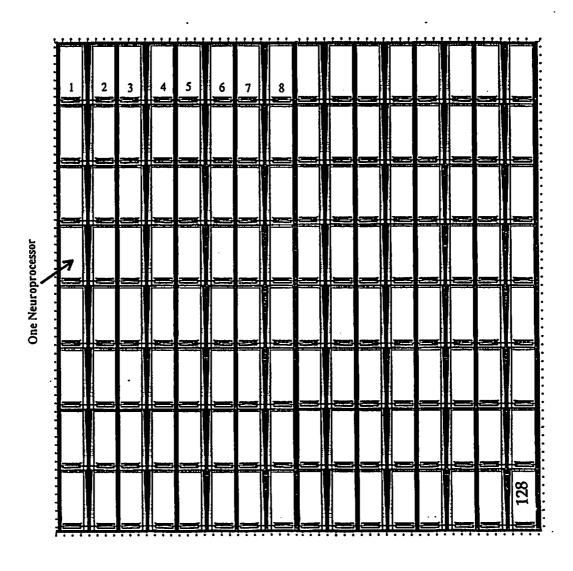

| Fig. 5.14 | The layout of a VLSI array neuroprocessors chip.                        |

|           | It contains 128 neuroprocessor and occupies 1.25x1.17 cm <sup>2</sup>   |

|           | silicon area in a submicron CMOS technology187                          |

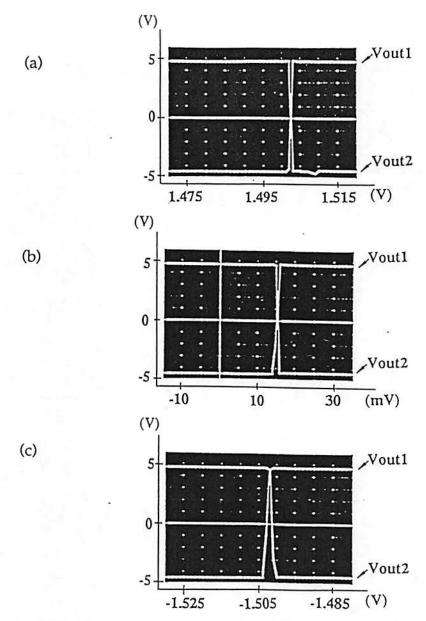

| Fig. 5.15 | The measurement results of the two-stage winner-take-all                |

|           | circuits:188                                                            |

| Fig. 5.16 | System diagram for real-time optical flow computing                     |

|           | using VLSI array neuroprocessors189                                     |

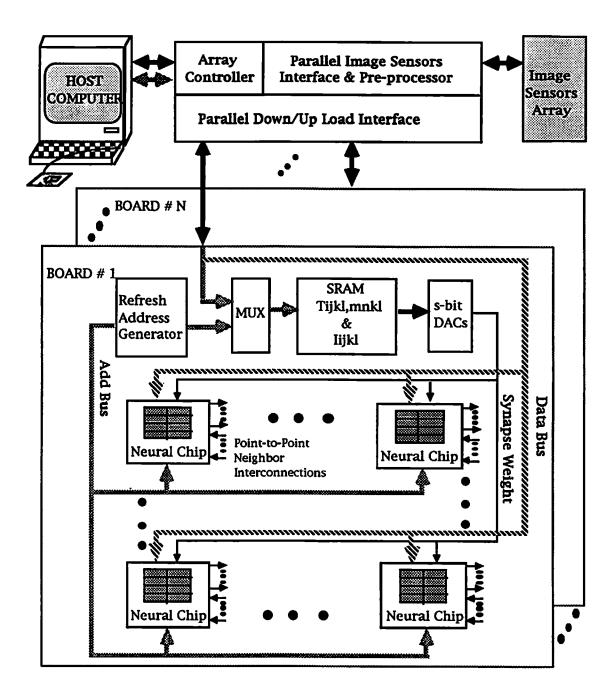

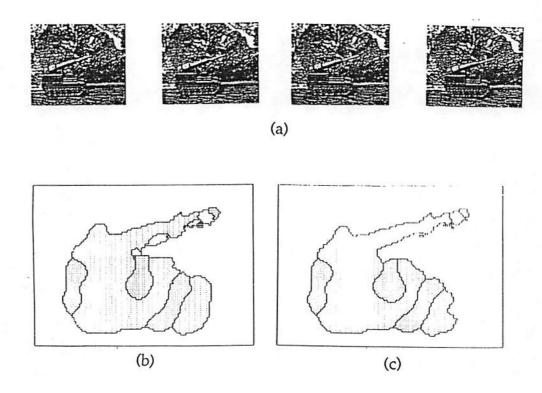

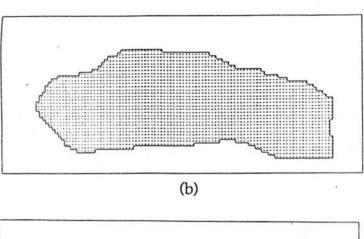

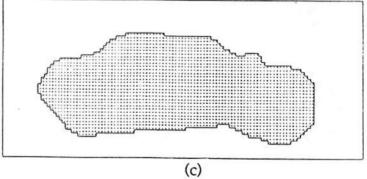

| Fig. 5.17 | System-level analysis on a sequence of four sedan images190             |

| Fig. 5.18 | System-level analysis on a sequence of four sedan images191             |

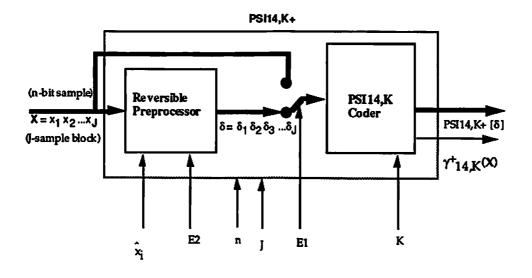

| Fig. 6.1  | High-level functional block diagram of the PSI14,K+                     |

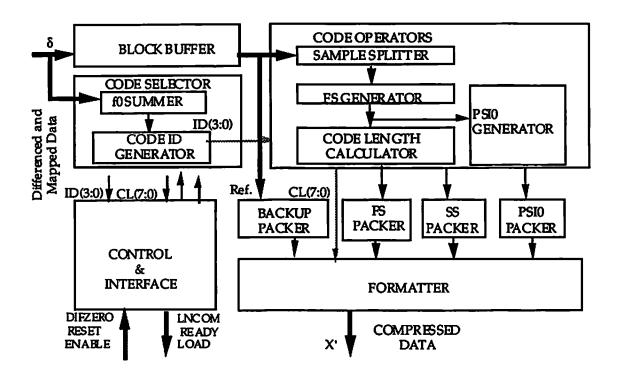

|           | coder205                                                                |

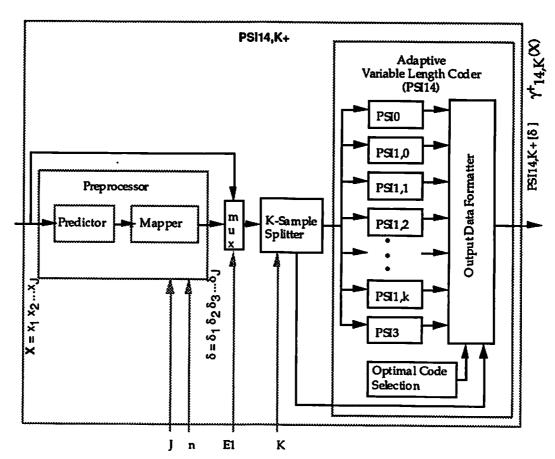

| Fig. 6.2  | An algorithmic structure of the UNC-PSI14,K+ coding205                  |

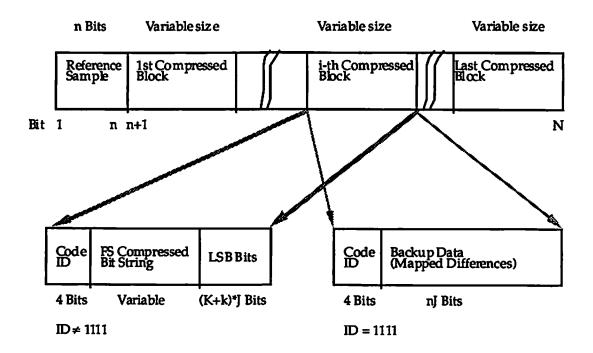

| Fig. 6.3  | The PSI14,K+ compression output format                 | 207         |

|-----------|--------------------------------------------------------|-------------|

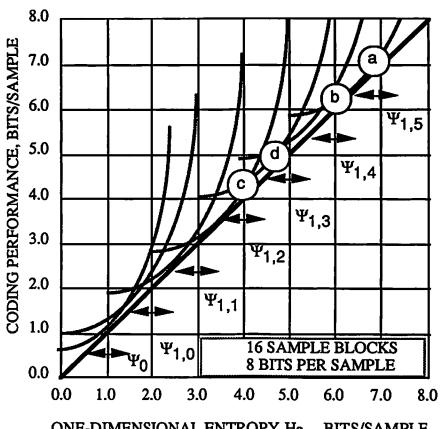

| Fig. 6.4  | Performance of the UNC-PSI14,K+ coder                  | <b>2</b> 10 |

| Fig. 6.5  | An end-to-end high rate communication/storage system   |             |

|           | with source/channel coding                             | 212         |

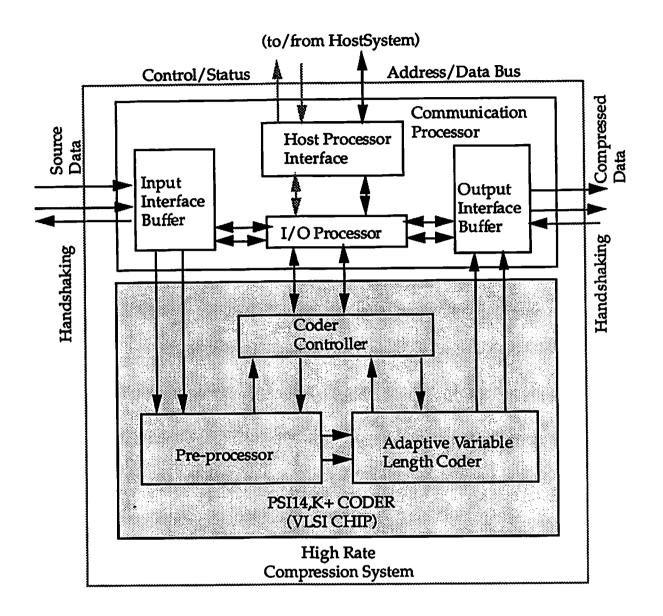

| Fig. 6.6  | A high rate compression system design                  | 213         |

| Fig. 6.7  | Block diagrams for the Preprocessor module             | 214         |

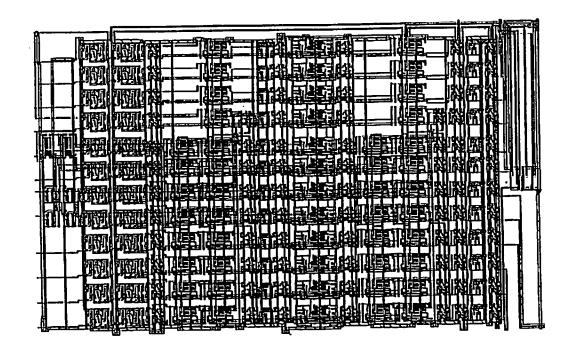

| Fig. 6.8  | A GDSII layout plot of the Preprocessor module         | 214         |

| Fig. 6.9  | Functional Block Design of the PSI14 adaptive variable |             |

|           | length coder.                                          | 217         |

| Fig. 6.10 | A GDS-II layout plot of the 1-μm UNC-PSI14,K+ design   | <b>22</b> 1 |

|           |                                                        |             |

# List of Tables

| Table 3.1 | Hardware performance comparison for variant systolic VQ    |     |

|-----------|------------------------------------------------------------|-----|

|           | designs                                                    | 91  |

| Table 3.2 | Hardware performance comparison for variant binary tree-   |     |

|           | searched VQ designs (codevector projected)                 | 92  |

| Table 3.3 | Pin definition of the raw-codebook binary tree-searched VQ | 93  |

| Table 3.4 | Pin definition of the raw-codebook binary tree-searched VQ | 94  |

| Table 3.5 | Size, power, and speed of BTSVQ-8 chip and its building    |     |

|           | block.                                                     | 95  |

| Table 3.6 | Chip information                                           | 96  |

| Table 3.7 | The SNR and MSE of S2R, BPC, ATR, and LBG for a 4x4-pixel  |     |

|           | window on the 512x512-pixel 256-gray-level girl image      | 97  |

| Table 3.8 | The SNR and MSE of S2R, BPC, ATR, and LBG for a 4x4-pixel  |     |

|           | window on the 256x256-pixel 256-gray-level moon image      | 98  |

| Table 5.1 | Comparison of Neighbor Interconnection Schemes             | 192 |

| Table 5.2 | Measured Network Iteration and Operation Speed             | 193 |

| Table 6.1 | Characteristics of the UNC- PSI14,K+ Chip                  | 220 |

#### **Abstract**

The increasing demands of speed and performance in data compression applications urge the VLSI data compression research. Our VLSI data compression research has been inspired by the neural networks, the parallel/pipelined processing, and the VLSI technologies. The primary objective was to develop effective image compression algorithm and their associated VLSI processors. The scope of our VLSI image compression research covers: (a) lossless image compression and VLSI processors, (b) lossy image compression and VLSI processors, and (c) neural network applications to image compression and VLSI neuroprocessors. The significant research results are presented in the following:

A high-speed image compression processor based on VLSI design of systolic binary tree-searched vector quantizer has been developed. Simulation results show that this design is applicable to many types of image data and capable of producing good reconstructed data quality at high compression ratios. Various design aspects for the binary tree-searched vector quantizer, that include the functionality, testability, and fault tolerance, were thoroughly investigated for VLSI implementation. A specific 8-level binary tree-searched vector quantizer can be realized on a custom VLSI chip that includes a systolic array of eight identical processors and a hierarchical memory of eight subcodebook memory banks. The total transistor count is about 300,000 and the die size is about 8.7 x 7.7 mm² in a 1.0  $\mu$ m CMOS technology.

An adaptive electronic neural network processor that has been developed for high-speed image compression based upon a frequency-sensitive self-organization algorithm. Performances of this self-organization network and a conventional algorithm for vector quantization are compared. The proposed method is quite efficient and can achieve near-optimal results. The neural network processor includes a pipelined codebook generator and a paralleled vector quantizer, which obtains a time complexity O(1) for each quantization vector. A mixed-

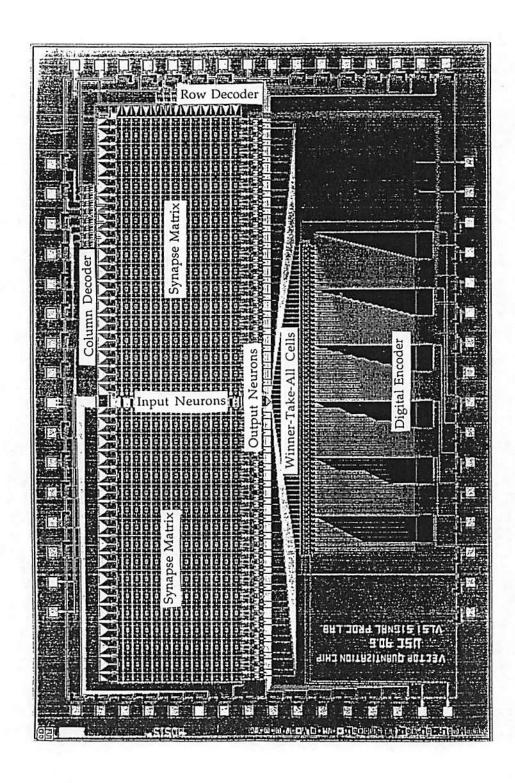

signal design technique with analog circuitry to perform massively parallel computation and digital circuitry to handle multiple-bit address information is used. The prototype neural network processor chip for a 25-dimensional adaptive vector quantizer of 64 codewords was designed, fabricated, and tested. It includes 25 input neurons, 25 x 64 synapse cells, 64 distortion-computing neurons, a winner-take-all circuit block, and a digital index encoder. It occupies a silicon area of 4.6 x 6.8 mm<sup>2</sup> in a 2.0-µm scalable CMOS technology and provides a computing capability as high as 3.2 billion connections per second.

A neural network based motion compression algorithm and its associated VLSI neuroprocessor have been developed. The neuroprocessor design is based on a locally connected multiple competitive neural network developed for high performance optical flow computing systems. The proposed VLSI neuroprocessor design can achieve a high-speed widerange motion estimation and thus an efficient image sequence compression by taking advantage of the massively parallel neural computing architecture and VLSI technology. An extendible VLSI neuroprocessor has been designed with a silicon area of 2,482 x 5,636  $\lambda^2$  in MOSIS scalable CMOS process. The mixed analog-digital design techniques are utilized to achieve compact and programmable synapses with gainadjustable neurons and winner-take-all cells for massively parallel neural computation. Measured results of the programmable synapse, summing neuron, and winner-take-all circuitry are presented. A 1.25 x 1.17 cm<sup>2</sup> chip in a submicron CMOS technology can accommodate 128 velocity-selective neuroprocessors and achieve 166.4 Giga connections per second. Computing of optical flow using one neural chip can be accelerated by a factor of 379 than a Sun-4/260 workstation. Real-time motion estimation on industrial video images is practical using an extended array of VLSI neuroprocessors. Actual examples on moving vehicles are presented.

An efficient VLSI pipelined processor design for high-speed lossless compression based on Rice algorithm has been developed. The Rice algorithm is an adaptive lossless coding scheme that provides near-

optimal performance over a broad range of data entropies. The Rice algorithm is also an efficiently implementable scheme for VLSI realization. A VLSI pipelined architecture was designed to allow compact implementation of a single-chip VLSI compressor. This lossless compressor is named UNC-PSI14,K+ since it implements an advanced version of the Rice 's universal noiseless coding method called PSI14,K+. The chip layout was generated for a 1.0-micron CMOS technology. It occupies a compact chip area of 5.1 x 5.3 mm<sup>2</sup>, with 49,000 transistors, 57 input/output pads, and 6 power/ground pads. The total power dissipation is 0.4 watts at the 40 MHz system clock with a 50% switching duty cycle. This compressor chip is mounted in an 84-pin pin-grid-array package. It can operate up to 40 Mpixels/sec. The potential applications of the proposed lossless compressor include database management systems, scientific instruments, CAE workstations, desktop computing machines, and the data systems that require high-speed compression without fidelity loss.

## Chapter 1

#### Introduction

#### 1.1 Motivation

The goal of data compression is to reduce the communication and storage costs for the data systems where reduction in the volume of transmitted or recorded data is important. The data compression field was intensively studied over the past four decades [1.1-1.11]. In the research field of data compression, important contributions have come from information sciences, computer sciences, signal and image processing, computer engineering, VLSI technology, etc. The increasing demands of speed and performance in data compression applications urge the VLSI data compression research. The major driving forces behind this trend include:

- More demand is placed on the communication and storage sub-systems as technology enhancement advances. Data compression techniques are employed in several key driving applications such as high definition TV, integrated information system, integrated service data networks, and the space-science data system.

- Technology improvements make compact integration of sophisticated data compression systems possible. These technology improvements include the advances of VLSI fabrication technologies and parallel processing architecture such as neural networks [1.12-1.16].

More efforts are still needed to develop high-speed highperformance data compression systems. To achieve the goal of efficient data compression, the following issues need to resolve:

- Due to different characteristics of various data sources, a sophisticated compression system is required to handle all types of source data such as speech, image, video, text, and binary files.

- Due to the intensive computation and real time processing requirements, the implementation of a high-speed data compression system is required to be with special-purpose parallel/pipelined processors.

- The characteristics of compressed data also inevitably add additional requirements to the data systems. Such requirements include more stringent communication quality and buffering management.

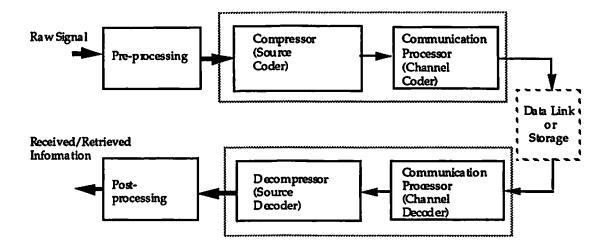

Figure 1.1 shows an end-to-end high rate data system diagram. To achieve a reliable high-speed communication and storage, the source data compression and channel coding become essential portions of the advanced high rate data system. Improvements in the data compression algorithm, architecture, software and hardware implementation, and associated system-level design issues are critical to effectively achieve the goal of data compression. Our VLSI image compression research has been motivated by a need of the high-speed high-performance data compression and inspired by the neural networks, the parallel/pipelined processing, and the VLSI technologies.

Fig. 1.1 An end-to-end high rate communication and/or storage system with the source and channel coding.

### 1.2 Scope and Objective

The scope of our VLSI image compression research covers:

- (a) lossless image compression and VLSI processors,

- (b) lossy image compression and VLSI processors, and

- (c) neural network applications to image compression and VLSI neuroprocessors.

Our work in each above-mentioned research topic includes:

- (a) system-level simulation to compare performances of the candidate algorithms for a targeted application,

- (b) VLSI architecture design of the selected algorithm,

- (c) VLSI functional and structural circuit and layout design,

- (d) prototype chip design and fabrication, and

- (e) testing and measurement.

The primary objective for each research topic was to develop an effective algorithm and its associated VLSI processor. The ultimate objective was to develop a high-speed high-performance image data compression system in special silicon chips or wafers.

## 1.3 Approach: An Integrated Study of VLSI Image Compression

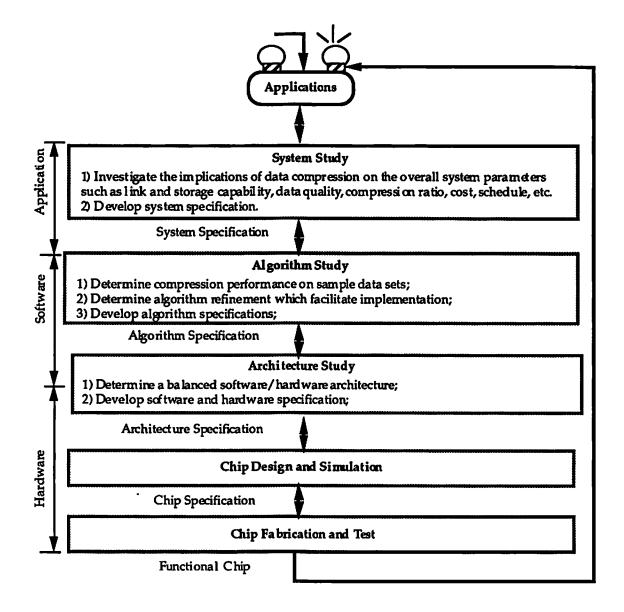

Study on the subject of VLSI image compression involves a broad spectrum of disciplines that include application, algorithm, architecture, and implementation. Figure 1.1 depicts an integrated design methodology that is adopted for our VLSI image compression studies.

System Study The goal of the system study is to develop feasible system specifications. The scope of the system study covers: (a) understanding of the targeted application, (b) investigation of the implications of data compression on the overall system parameters such as link bandwidth, storage capabilities, compression needs, data quality, and so on, (c) system simulation on targeted applications, (d) system refinement to facilitate the feasibility, and (e) development of system specifications.

Algorithm Study The goal of the algorithm study is to develop effective algorithm specifications. The scope of the algorithm study covers: (a) understanding of the system specifications, (b) a survey of candidate algorithms, (c) algorithm analysis on targeted data sample sets, (d) system and algorithm refinement to facilitate the implementation, and (e) development of algorithm specifications.

Architecture Study The goal of the architecture study is to develop balanced hardware/software architecture specifications. The scope of the architecture study covers (a) understanding of the algorithm specifications, (b) parallelism extraction and mapping of the algorithm into architecture, (c) architecture evaluation with software/hardware implementation technologies, (d) algorithm and architecture refinement to facilitate the VLSI implementation, and (e) development of architecture specifications.

VLSI Design and Simulation The goal of the VLSI design and simulation is to develop functional chip specifications. The scope of this task covers (a) understanding of the architecture specifications, (b) select a chip design style/method and associated tools, (c) design functional building blocks and structural primitives to realize the targeted architecture, (d) simulate the

functional design, (e) verify the physical design, (f) design refinement to facilitate the speed-area tradeoffs, the worst-case timing margins, and the testability, and (g) generate a chip specification database.

VLSI Fabrication and Test The goal of the VLSI fabrication and test is to realize the chip specification onto a real chip. The MOSIS provides chip fabrication service through a variety of chip foundries [1.16]. The chip is tested to be functional by using a chip tester and a system testbed.

Design and implementation of the application-specific processors in VLSI are a highly challenging and iterative process. This integrated design method for our VLSI image compression research has been very successful. The success relies on a fundamental understanding of application, algorithm, architecture, and VLSI implementation,

Fig. 1.2 Design methodology for the VLSI image compression processor.

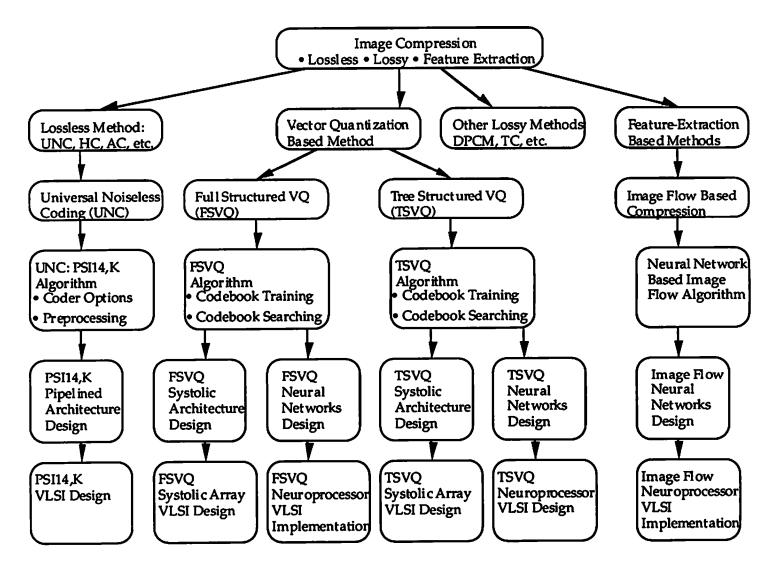

#### 1.4 Overview of the Dissertation

This dissertation contributes to real-time image compression research with emphasis on the hardware development, in particular to the high-speed high-performance VLSI image compressor design. Figure 1.3 shows an organization of various image compression research subjects discussed in this dissertation. The following selected chapters are covered to present our studies on the subject of VLSI image compression:

Chapter 2 starts with a brief introduction of widely used data compression algorithms. Data compression can be divided into two categories: lossless compression and lossy compression. Four lossy data compression algorithms were investigated: predictive coding, block truncation coding, transform coding, and vector quantization. Four types of losses coding algorithm were also investigated: Huffman codes, Rice codes, Limped-Ziv codes, and arithmetic codes. Furthermore, the image compression algorithm using neural-network paradigms were investigated. The limitations, assumptions, and applications for the algorithms were discussed.

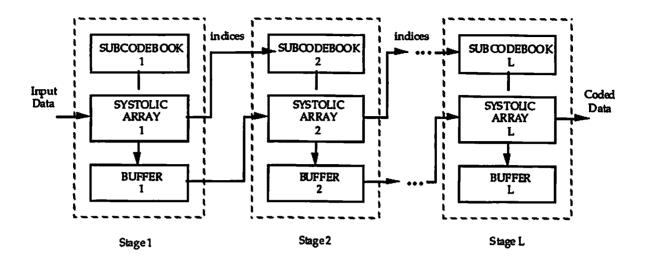

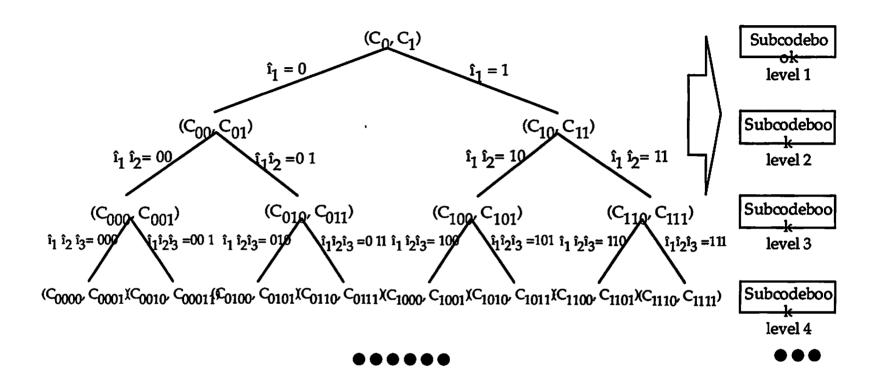

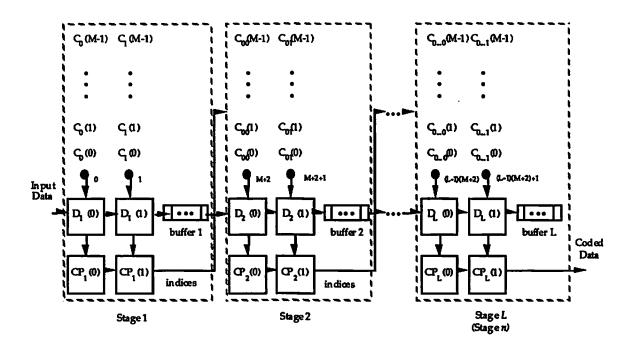

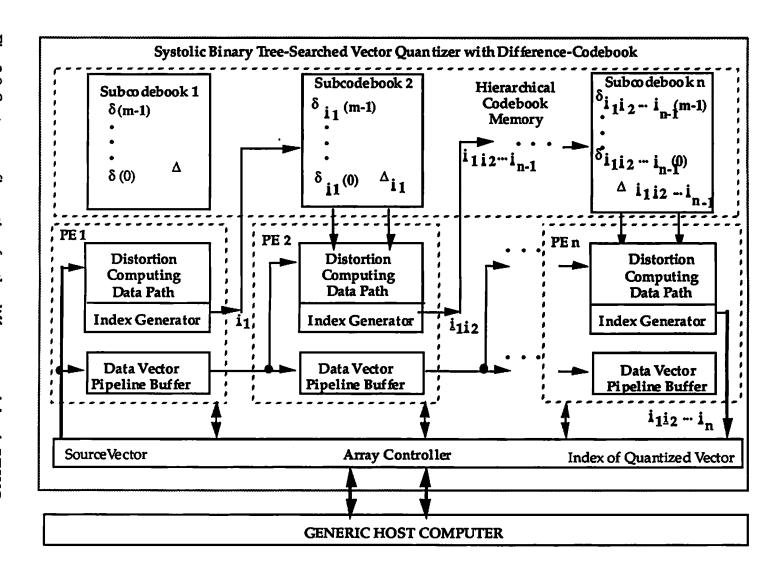

Chapter 3 presents a high-speed image compression processor based on VLSI design of systolic binary tree-searched vector quantizer. Simulation results show that this design is applicable to many types of image data and capable of producing good reconstructed data quality at high compression ratios. Various design aspects for the binary tree-searched vector quantizer, that include the functionality, testability, and fault tolerance, were thoroughly investigated for VLSI implementation. A specific 8-level binary tree-searched

vector quantizer can be realized on a custom VLSI chip that includes a systolic array of eight identical processors and a hierarchical memory of eight subcodebook memory banks. The total transistor count is about 300,000 and the die size is about 8.7 x 7.7 mm<sup>2</sup> in a 1.0 µm CMOS technology. The throughput rate of this high-speed VLSI compression system is 25M pixels per second and its equivalent computation power is 400 MIPS. Portions of this chapter were presented at the 1990 IEEE VLSI Signal Processing, Workshop at San Diego, CA. [1.17], the 1991 Advanced Research in VLSI Conference at Santa Cruz, CA [1.18], and the 1991 IEEE Workshop on Visual Signal Processing and Communications, at Taiwan, Republic of China [1.19].

Chapter 4 presents an adaptive electronic neural network processor that has been developed for high-speed image compression based upon a frequency-sensitive self-organization algorithm. Performances of this self-organization network and a conventional algorithm for vector quantization are compared. The proposed method is quite efficient and can achieve near-optimal results. The neural network processor includes a pipelined codebook generator and a paralleled vector quantizer, which obtains a time complexity O(1) for each quantization vector. A mixed-signal design technique with analog circuitry to perform neural computation and digital circuitry to handle multiple-bit address information is used. The prototype neural network processor chip for a 25-dimensional adaptive vector quantizer of 64 codewords was designed, fabricated, and tested. It includes 25 input neurons, 25 x 64 synapse cells, 64 distortion-computing neurons, a winner-take-all circuit block, and a digital index encoder. It occupies a silicon area of 4.6 x 6.8 mm<sup>2</sup> in a 2.0-µm scalable CMOS technology and provides a

computing capability as high as 3.2 billion connections per second. The experimental results for this neural-based vector quantizer chip and the winner-take-all circuit test structure were also presented. Portions of this chapter were presented at the 1991 IEEE first Data Compression Conference at Snowbird, Utah [1.20], the IEEE international Conference on Acoustics, Speech and Signal Processing, at Toronto, Ontario, Canada [1.21], the 1991 International Joint Conference on Neural Networks, at Seattle [1.22], and the IEEE Trans. on Neural Network, May 1992 [1.23].

Chapter 5 describes a neural network based motion compression algorithm and its associated VLSI neuroprocessor design. The neuroprocessor design is based on a locally connected multiple competitive neural network developed for high performance optical flow computing systems. The proposed VLSI neuroprocessor design can achieve a high-speed wide-range motion estimation and thus an efficient image sequence compression by taking advantage of the massively parallel neural computing architecture and VLSI technology. An extendible VLSI neuroprocessor has been designed with a silicon area of 2,482 x 5,636  $\lambda^2$  in MOSIS scalable CMOS process. The mixed analog-digital design techniques are utilized to achieve compact and programmable synapses with gain-adjustable neurons and winner-take-all cells for massively parallel neural computation. Measured results of the programmable synapse, summing neuron, and winner-take-all circuitry are presented. A 1.25 x 1.17 cm<sup>2</sup> chip in a submicron CMOS technology can accommodate 128 velocity-selective neuroprocessors and achieve 166.4 Giga connections per second. Computing of optical flow using one neural chip can be accelerated by a factor of 379 than a Sun-4/260 workstation. Real-time motion estimation on industrial video images is practical using an extended array of VLSI neuroprocessors. Actual examples on moving vehicles are presented. Portions of this chapter were presented at the 1990 IEEE International Conference of Computer Design at Cambridge, MA [1.24], the 1991 IEEE international Conference on Acoustics, Speech and Signal Processing, at Toronto, Ontario, Canada [1.25], and has been accepted for publication in the IEEE Trans. on Neural Networks [1.26].

Chapter 6 presents an efficient VLSI pipelined processor design for high-speed lossless compression based on Rice algorithm. The Rice algorithm is an adaptive lossless coding scheme that provides near-optimal performance over a broad range of data entropies. The Rice algorithm is also an efficiently implementable scheme for VLSI realization. A VLSI pipelined architecture was designed to allow compact implementation of a single-chip VLSI compressor. This lossless compressor is named UNC-PSI14,K+ since it implements an advanced version of the Rice 's universal noiseless coding method called PSI14,K+. The chip layout was generated for a 1.0-micron CMOS technology. It occupies a compact chip area of  $5.1 \times 5.3 \text{ mm}^2$ , with 49,000 transistors, 57 input/output pads, and 6 power/ground pads. The total power dissipation is 0.4 watts at the 40 MHz system clock with a 50% switching duty cycle. This compressor chip is mounted in an 84-pin pin-gridarray package. It can operate up to 40 Mpixels/sec. The potential applications of the proposed lossless compressor include database management systems, scientific instruments, CAE workstations, desktop computing machines, and the data systems that require high-speed compression without fidelity loss. Portions of this chapter were presented at the 1987 IEEE Aerospace EASCON Conference, Washington [1.27], the 1988 SPIE Conference, Los Angeles [1.28], NASA Technology Briefs, October 1989 [1.29], and the 1991 IEEE First Data Compression Conference, Snowbird Utah [1.30].

Chapter 7 discusses potential future research and development directions that are worth of further investigation.

Fig. 1.3 Various image compression method discussed in this dissertation.

#### References

- [1.1] R. M. Gray, Source Coding Theory, Kluwer Academic Publishers: Boston, MA, 1990.

- [1.2] A. Gersho, R. M. Gray, Vector Quantization and Signal Compression, Kluwer Academic Publishers: Boston, MA, 1991.

- [1.3] J. A. Storer, *Data Compression- Methods and Theory*, Computer Science Press, Rockville, Maryland, 1988.

- [1.4] T. J. Lynch, Data Compression- Techniques and Applications, Lifetime Learning, Wadsworth, 1985.

- [1.5] N. S. Jayant (Ed.), Waveform Quantization and Coding, IEEE Press, 1976.

- [1.6] N.S. Jayant, P. Noll, Digital Coding of Waveforms, Prentice-Hall, 1984

- [1.7] R. J. Clarke, Transform Coding of Images, Academic Press, 1985.

- [1.8] A. N. Netravali, B. G. Haskell, Digital Pictures: Representation and Compression, Plenum Press, 1988.

- [1.9] H. Abut (Ed.), Vector Quantization, IEEE Press, 1990.

- [1.10] M. Rabbani, P. Jones. *Digital Image Compression*, SPIE Publications, 1991.

- [1.11] A. K. Jain, "Image data compression: a review," Proc. of IEEE, vol. 69, no. 3, pp. 349-389, Mar. 1981.

- [1.12] B. W. Lee, B. J. Sheu, *Hardware Annealing in Analog VLSI Neurocomputing*, Kluwer Academic Publishers: Boston, MA, 1991.

- 14

- [1.13] C. A. Mead, Analog VLSI and Neural Systems, Addison Wesley: New York, NY, 1989.

- [1.14] N. Weste, K. Eshraghian, Principles of CMOS VLSI Design- A Systems Perspective, Addison Wesley: Reading, MA, 1985.

- [1.15] E. E. Swartzlander, Wafer Scale Integration, Kluwer Academic Publishers: Boston, MA, 1989,

- [1.16] C. Tomovich, "MOSIS A gateway to silicon," *IEEE Circuits and Devices Magazine*, vol. 4, no. 2, pp. 22-23, Mar. 1988.

- [1.17] W.-C. Fang, C.-Y. Chang, B. J. Sheu, "Systolic tree-searched vector quantizer for real-time image compression," VLSI Signal Processing, IV, H. S. Moscovitz, Kung Yao, R. Jain (Eds.), pp. 352-361 (Chap. 34), IEEE PRESS: Piscataway, NJ, 1991.

- [1.18] W.-C. Fang, B. J. Sheu, "VLSI adaptive image compression," Advanced Research in VLSI: Proceedings of the 1991 University of California/Santa Cruz Conferences, Carlo H. Sequin (Ed.), pp. 371-386, MIT Press, Cambridge, MA, 1991,

- [1.19] O. T.-C. Chen, B. J. Sheu, <u>W.-C. Fang</u>, "Adaptive codebook construction and real-time hardware implementation for binary treesearched vector quantizer," *IEEE Workshop on Visual Signal Processing* and Communications, pp. 35-38, Taiwan, Republic of China, June 1991.

- [1.20] W.-C. Fang, B. J. Sheu, O. T.-C. Chen "A neural network based VLSI vector quantizer for real-time image compression," *IEEE Proceedings on the first Data Compression Conference*, Snowbird Utah, pp. 342-351, IEEE Computer Society Press: Los Alamitos, Apr., 1991.

- [1.21] B. J. Sheu, W.-C. Fang "Real-time high-ratio image compression using adaptive VLSI neuroprocessor," *IEEE Proceedings of International Conference on Acoustics, Speech and Signal Processing*, pp. Toronto, Ontario, Canada, May, 1991.

- [1.22] W.-C. Fang, B. J. Sheu, O. T.-C. Chen, "A real-time VLSI neuroprocessor for adaptive image compression based upon frequency-sensitive competitive learning," *International Joint Conference on Neural Networks*, pp. 429-435, Seattle, WA, July, 1991.

- [1.23] W.-C Fang, B. J. Sheu, O. T.-C. Chen, J. Choi "A VLSI neural processor for image data compression using self-organization networks," *IEEE Trans. on Neural Networks: Special Issue on Neural Network Hardware*, vol. 3, no. 2, May 1992.

- [1.24] W.-C. Fang, B. J. Sheu, "Real-time computing of optical flow using adaptive VLSI neuroprocessors," *IEEE International Conference of Computer Design*, pp. 122-125, Cambridge, MA, Oct. 1990.

- [1.25] W.-C. Fang, B. J. Sheu, J.-C. Lee, "A Neuroprocessor for real-time image flow computation," *IEEE Proceedings of International Conference on Acoustics, Speech and Signal Processing*, pp. 2413-2416, Toronto, Ontario, Canada, May, 1991.

- [1.26] J.-C. Lee, B. J. Sheu, <u>W.-C. Fang</u>, "VLSI neuroprocessors for video motion detection," IEEE Trans. on Neural Networks, (accepted for publication in April, 1992)

- [1.27] J.-J. Lee, W.-C. Fang, R. F. Rice, "Real-time data compressor for EOS-class missions," Proceeding of the 1987 IEEE Aerospace EASCON Conference, Washington, D. C., Oct. 1987.

- [1.28] J. -J. Lee, <u>W.-C. Fang</u>, R. F. Rice, "VLSI universal noiseless compressor for EOS-class missions," Proceeding of the 1988 SPIE Conference, Los Angeles, California, Feb. 1988.

- [1.29] Robert F. Rice, Jun-Ji Lee, <u>Wai-Chi Fang</u>, "VLSI universal noiseless coder", *NASA Tech Briefs*, vol. 13, no.10, Oct. 1989

- [1.30] R. Anderson, J. Bowers, <u>W.-C. Fang</u>, D. Johnson, J.-J. Lee, R. Nixon, "A very high speed noiseless data compression chip for space imaging applications", Proceedings IEEE Data Compression Conference, Snowbird, Utah, April 1991.

# Chapter 2

## **Data and Image Compression**

Efficient compression of data would significantly decrease both the communication and storage costs [2.1]. Data compression can be roughly divide into two categories, lossless compression and lossy compression. A lossless compression algorithm seeks to represent a given data set with the fewest number of bits possible without any fidelity loss while a lossy compression algorithm provides higher compression factors at the expense of some distortions in the reconstructed data set [2.2].

In this chapter, we focus on these algorithms have been investigated for an integrated information processing system [2.12] which has various signal representations including speech, image, video, text, binary file, etc. Section 2.1 review the traditional lossless data compression algorithms. Section 2.2 review the traditional lossy data compression algorithms. Section 2.3 investigated the neural network based data and image compression. The limitations, assumptions, and applications for each algorithm were examined and reported.

### 2.1 Lossless Compression

Lossless compression is usually required in such situations where the compression system must be designed without prior knowledge of the structure or end use of the original data. Lossless coding is a data compression techniques that is employed to compress the data without inducing any distortion in the reconstructed data. Its maximum compression ratio is limited by the entropy of the source data. There are two types of lossless coding algorithm: Huffman coding [2.2,3] and universal noiseless coding [2.7,8]. The universal noiseless coding algorithm only needs to know the probability ordering of the source data while the Huffman coding algorithm requires the knowledge of the probability distribution. The assumption on the knowledge of the probability ordering is more realistic since the source data can be preprocessed (e.g. by taking difference of adjacent pixels). The preprocessed data (e.g. difference image) typically assumes some degree of probability ordering (e.g. higher probability for smaller difference in adjacent pixels).

For this reason, we focus only on the universal noiseless coding technique due to lack of any prior information on the source data statistics. The advantages of the universal noiseless coding are: 1) No distortion in the reconstructed data; 2) No need to know the probability distribution; and 3) simple encoding and decoding procedures. Its drawbacks are: 1) Algorithm performance is more sensitive to channel errors; 2) Output data rate (i.e., compression ratio) is not controllable; and 3) Maximum compression ratio is limited by the source entropy.

Among existing lossless data compression algorithms [2.3-8], the universal noiseless coding (UNC) is an effective method for producing reconstructed data without any fidelity loss. This adaptive algorithm provides excellent performance over a broad range of data contents. A high-

speed UNC coder is therefore proposed to implemented at a low hardware cost by using a VLSI pipelined architecture [2.9-10]. Notice that the noiseless coding technique alone is not feasible to reduce the data volume as required for the advanced data system. It is better suited as a post-processing stage for further reduction of data compressed by a lossy compression algorithm to maximize the compression to distortion noise ratio.

## 2.2 Lossy Compression

Four data compression algorithms were investigated for the advanced data system. There are predictive coding, block truncation coding, transform coding, and vector quantization algorithms. The limitations, assumptions, and applications for each algorithm were examined as the following:

#### 2.2.1 Predictive Coding

The predictive coding technique is a simple coding algorithm that provides a relatively small compression ratio with reasonably good image quality [2.12]. Its major limitation is that it cannot compress data below 1 bit per pixel and its image quality at 1 bit per pixel is marginal. Another limitation is that it provides very limited flexibility in selection of compression ratio versus data quality. If the source data is stationary, the predictor need not be updated, which makes it possible for real-time applications. However, if the source data statistics vary with time, buffering

of the data and retaining of the prediction coefficients is required. Predictive coding is best suited for applications where very simple encoders and decoders are required and the compression ratio requirements are low (i.e., less than 4:1).

Compared to the block truncation coding algorithm, it offers about the same data quality but provides less flexibility in the compression ratio versus data quality trade-off. Also its prediction coefficients would require training of data sets if the source statistics vary significantly. Compared to the transform coding and vector quantization algorithms, the predictive coding algorithm cannot achieve as high a compression ratio and its data quality is usually 2 to 3 dB worse.

## 2..2.2 Block Truncation Coding Algorithm

The block truncation coding (BTC) algorithm [2.16] has the following advantages: 1) simple encoding and decoding procedures; 2) small memory requirements; 3) adaptivity to local image statistics; and 4) selectable compression ratios up to K:1. where K is the number of bits per sample in the original data. Its major limitation is similar to that of predictive coding, i.e., the maximum compression ratio is K:1 and the image quality at this compression ratio is marginal. Another limitation is that at the same compression ratio, the data quality using the BTC algorithm is about 2 to 3 dB worse than that of the adaptive transform coding or the vector quantization algorithm. For the algorithm to perform well, it assumes that the statistics of each data block are primarily characterized by its first two moments. If

higher order statistics exist, the reconstructed image quality degrades. In summary, the BTC algorithm appears to be a promising candidate for a data system requiring small compression ratios, low implementation cost, and some adaptivity to data statistics.

## 2..2.3 Transform Coding Algorithm

The adaptive transform coding algorithm is a technique capable of compressing the image data to a user specified compression factor given that the associated image quality degradation is tolerable [2.13,14,15]. It generally yields better image quality than both the predictive coding and block truncation coding algorithms at the same compression ratio. Its major limitation is that it is computationally intensive in both encoding and decoding, requiring a large number of two dimensional transforms. Another limitation is that it requires a large storage buffer from which the source statistics are derived. It assumes that the statistics of each data block can be well characterized by the lower frequency terms in the spectra such that the bits can be more efficiently assigned to these transform coefficients that the higher frequency terms.

In summary, the adaptive transform coding algorithm is promising for a single-encoder, single-decoder application such as a high-rate communication link that requires both high compression ratio and good data quality.

## 2.2.4 Vector Quantization Algorithm

Vector quantization (VQ) has been show as an effective method for speech waveform coding and image data compression [2.17,18]. It is capable of producing good reconstructed image quality at high compression ratios. As compared to the adaptive transform coding, the primary advantage of the VQ algorithm is its extremely simple decoding procedure, which makes it a promising technique for the single-encoder multiple-decoder data compression systems.

Vector quantization appears to be the most viable technique for the advanced data system. This judgment is based on the reconstructed image quality at the required high compression ratio, regular data flow pattern in the encoder, and a simple decoding procedure (table look-up). By combination of tree-searched VQ and systolic processing, a high throughput compressor can be realized at a low hardware cost.

#### 2.2.5 Summary of Results

Four lossy compression algorithm were evaluated. Among them, predictive coding and block truncation coding are two simple coding algorithms that provide reasonably good image quality at small compression ratios. Their common major limitation is that they cannot compress the data below 1 bit per pixel and the image quality at 1 bit per pixel is marginal. Transform coding and vector quantization are more complex algorithm, however, they are capable of producing good reconstructive image quality at higher compression ratios. The transform coding algorithm achieves high

performance at the cost of high complexity in both the encoder and decoder. Although vector quantization also requires a computationally intensive process in encoding the data, its decoding procedure is a simple table look-up. Moreover, the regular data flow pattern in the vector quantization encoder allows efficient implementation using both parallel and pipelined processing techniques.

The results show that the vector quantization algorithm appears to be the most viable technique for an advanced data system. Besides, universal noiseless coding algorithm is suited as a post-processing stage for further reduction of data compressed by vector quantization algorithm to maximize the compression to distortion noise ratio.

## 2.3 Neural Networks for Data and Image Compression

Artificial neural networks serve an important purpose that is to extract and emulate the functions and operations from biological neural networks for our next generation artifacts. Artificial neural networks also serve as vehicles to study neuroscience by synthesizing low level finding and high level hypotheses together into a artificial system that can be simulated and compared with the behaviors of living systems.

Neural network approaches appear to be very promising for intelligent information processing [2.19-28] due to their massively parallel computing structures and self-organization learning schemes. A number of studies have been reported on using artificial neural networks for VQ and image compression applications [2.29-32]. The existing works in image

compression using neural networks share the same key idea which is performing the feature extraction or classification at the source data to achieve data compression.

## 2.3.1 Associative Memory

J. Solomon et al. applied associative model to do multispectral image compression [2.37]. The approach is based on the minimized energy search which is state dependent. Full information retrieval can be achieved by partial input. The percentage of the spurious state is high if the codewords are not orthogonal. The scheme proposed is similar to ordinary VQ. The codebook is prepaid and stored in the Hopfield Net before encoding. The way to generate codebook is similar to supervised learning. The desired set of primitives are used to train the associative memory. Then the trained associative memory serve as a classifier(encoder) to classify(encode) the image vectors. Whenever a image vector present, the list of stored codewords is searched, and the best match codeword and its index is produced.

#### 2.3.2 Multi-layer Perceptron

G. W. Cottrell et al. used multi-layer perceptron with error back propagation (EBP) learning to do image compression [2.33]. Multi-layer perceptrons are feed-forward nets. The back-propagation algorithm uses a gradient search technique to minimize a cost function equal to the mean square difference between the desired and the actual net outputs.

EBP is a gradient search techniques that may find a local minimum in the LMS cost function instead of the desired global minimum. The local minima in VQ corresponds to clustering two or more disjoint codewords into one. The number of presentations of training data required for convergence is very large (more than 100 passes through all the training data). A three-layer perceptron can form a codebook and then work as an ordinary vector quantization. The way to generate codebook is the supervised BPE learning. Training and testing are separate into two phase.

## 2.3.3 Hierarchy Associative Memory

L. D. Jackel et al. reported the experiment result of image vector quantization using associative memory model and the concept of the hierarchy neural network [2.36]. The scheme proposed is based on associative memory model. Training and testing are separate into two phase. The codebook is prepared before encoding. The desired image vectors are used as training prototypes to train the associative memory. Then the trained associative memory serve as a classifier(encoder) to classify(encode) the image vectors. The VQ proceeds by first matching image vector to the best mothership and then matching to the appropriate rowboat by using hierarchy neural networks. The scheme is similar to an ordinary VQ. An unique point has be made is the use of neural net hierarchy in considering the practical memory size of ANN chip.

#### 2.3.4 Winner-Take-all Competitive Network

J. G. Daugman et al. modeled the actually neurobiologically recorded receptive profiles with 2-D Gabor and treat these simulated receptive profiles as the visual primitive to do vector quantization with winner-take-all model. The generation of codebook is by supervised training the winner-take-all nets with the known 4,096 visual primitives. [2.34]. In this image data VQ compression scheme, each (8x8) pixel region is represented by a single 12-bit quantity which specifies the victor in the winner-take-all competition among 4,096 candidate visual primitives. The compression ratio about 40:1 (0.1875 bits/pixel) was reported.

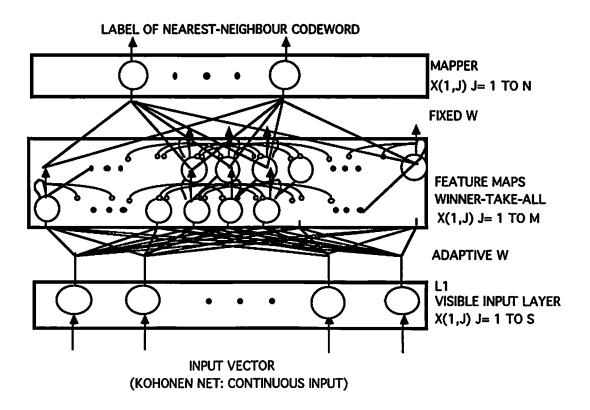

#### 2.3.5 Kohonen's Self-Organizing Feature Maps

Kohonen's algorithm creates a learning vector quantizer (LVQ) by adjusting weights from common input nodes to M output nodes arranged in a two dimensional grid as shown in Fig. 2.1. Output nodes are extensively interconnected with many local connections. Continuous-valued input vectors are presented sequentially in time without specifying the desired output. After enough input vectors have been presented, weights will specify cluster or vector centers that sample the input space such that the point density function of the vector centers tends to approximate the probability density function of the input vectors [2.24]. Kohonen's net does not perform the iterative K-means training algorithm (LBG algorithm). Instead, each new pattern is presented only once and weights are modified after each presentation. The Kohonen net does, however, form a pre-specified number

of clusters as in the K-means algorithm, where the K refers to the number of clusters formed. This algorithm can perform well in noise because the number of classes is fixed, weights adapt slowly, and adaptation stops after training. This algorithm is thus an ordinary VQ when the number of clusters desired can be specified before use and the amount of training data is large relative to the number of clusters desired. It is similar to the LBG algorithm in this respect.

Fig. 2.1 Structure of Kohonen's self-organizing feature maps.

As shown in Fig. 2.1, the network consists of two layers of units, a linear input layer and an internal processing layer. The internal processing

layer contains inhibitory connections and provides a "top-down" training signal to connections between the two layers. Two dimensional array of output nodes used to form feature maps. Every input is connected to every output node via a variable connection weight. Kohonen's algorithm to perform VQ using self-organizing feature maps is described in the following:

## Algorithm: Kohonen's self-organizing feature maps

## Step 1: Initialize Weights

Initialize weights from N inputs to the M output nodes to small random values. Set the initial radius of the neighborhood of each node.

## **Step: Present New Input**

(Note: No classification provided.)

## **Step 3: Compute Distance to All Nodes**

Compute distance dj between the input and each output node j using

$$N-1$$

$$d_{j} = \sum_{i=0}^{N-1} [x_{i}(t) - w_{ij}(t)]^{2}$$

where  $x_i$  (t) is the input to node i at time t and  $w_{ij}$  is the weight from input node i to output node j at time t.

## Step 4: Select Output Node with Minimum Distance (Winner)

Select the node j\* as the output node with minimum dj.

## Step 5: Update Weights to Node j\* and Neighbors

Weights are updated for node j\* and all nodes in the neighborhood defined by NE<sub>j\*</sub>(t). New weights are

$$w_{ij}(t+1) = w_{ij}(t) + \eta(t)[x_i(t) - w_{ij}(t)]$$

For j belong to  $NE_{j^*}$  and  $0 \le i \le N-1$ .

$\eta(t)$  is a gain term (0<  $\eta(t)$  <1) that decreases in time.

(Weights eventually converge and are fixed after the gain term is reduced to zero.)

Step 6: Repeat by Going to Step 2

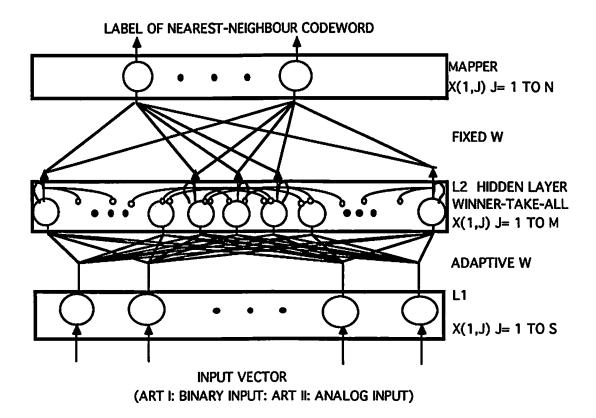

## 2.3.6 Grossberg's Adaptive Resonance Theory (ART) Network

The Carpenter/Grossberg's Adaptive Resonance Theory (ART) network [2.26-28] consists of attentional subsystem and orienting subsystem. Familiar events are processed within an attentional subsystem, which is a two-layer competitive learning network.

ART network [2.28] forms clusters and is trained without supervision. This net implements a clustering algorithm that is very similar to the simple sequential leader clustering algorithm described in [2.41]. The ART is completely described using nonlinear differential equations, including extensive feedback. In typical operation, the differential equations can be shown to implement the clustering algorithm presented in the following:

Algorithm: Carpenter/Grossberg's Adaptive Resonance Theory (ART)

Step 1. Initialization

$$\mathsf{t_{ij}}(0) = 1$$

$$b_{ij}(0) = 1/(1+N)$$

$0 \le i \le N-1$

$0 \le j \le M-1$

Set  $\rho$ ,  $0 \le r \le 1$

In these equations  $b_{ij}(t)$  is the bottom up and  $t_{ij}(t)$  is the top down connection weight between input node i and output node j at time t. These weights define the exemplar specified by output node j. The fraction  $\rho$  is the vigilance threshold which indicates how close an input must be to a stored exemplar to match.

## Step 2. Apply New Input

## **Step 3. Compute Matching Scores**

N-1

$$\mu_i = \sum_{i=0}^{N-1} b_{ij}(t) x_i \qquad 0 \le j \le M-1$$

In this equation  $\mu_j$  is the output of output node j and  $x_i$  is element i of the input which can be 0 or 1.

## Step 4. Select Best Matching Exemplar (Winner)

$$\mu_{j^*} = \max \{\mu_j\}$$

This is performed using extensive lateral inhibition as in the maxnet.

## Step 5. Vigilance Test

$$| | T.X| | = \sum_{i=0}^{\infty} t_{ij} x_i$$

If  $||T.X|| / ||X|| > \rho$  then go to Step 6, otherwise goto Step 7.

(i.e. Number of one bits in common normalized by the number of one bits in input.)

## Step 6 Disable Best Matching Exemplar

The output of the best matching node selected in Step 4 is temporarily set to zero and no longer takes part in the maximization of Step 4. Then go to Step 3. Step 7A (Training). Adapt Best Matching Exemplar

$$t_{ij}*(t+1) = t_{ij}*(t) \times_i$$

$$N-1$$

$$b_{ij}*(t+1) = t_{ij}*(t)\times_i / (0.5 + \Sigma t_{ij}*(t)\times_i)$$

$$i = 0$$

## Step 7B (Testing). Output the Label of Best Matching Exemplar

## Step 8. Repeat by Going to Step 2

(First enable any nodes disabled in Step 6 for new input data)

The structure of VQ using ART net is shown in Fig. 2.2. The adaptation of best matching exemplar only happen during codebook training phase. In the testing phase, the ART works as a self-adjusting search to find the best match from the learned codewords.

Fig. 2.2 Structure of VQ using ART.

#### 2.4 Conclusion

For lossless data compression, the universal noiseless coding (UNC) is an effective method for producing reconstructed data without any fidelity loss. This adaptive algorithm provides excellent performance over a broad range of data contents. A high-speed VLSI design of the UNC coder will be presented in Chapter 6.

For lossy image compression, the vector quantization algorithm appears to be the most viable technique for an advanced data system. Various design aspects for the VLSI vector quantization, that include the functionality, testability, and fault tolerance, will be thoroughly investigated in Chapter 3.

Image compression and classification is an area that neural network models have been very successful. The progress in artificial neural network technology, especially the mixed-signal VLSI has shown the potential to support a real time adaptive vector quantization for image compression applications [2.42, 2.43]. The follow-up research reported in Chapter 4 will be emphasized on the use of adaptive self-organized neural networks to a VLSI neural network based image compressor.

#### References

- [2.1] A. K. Jain, "Image data compression: A review," Proc. of IEEE, vol. 69, no. 3, pp. 349-389, Mar. 1981.

- [2.2] R. M. Gray, Source Coding Theory, Kluwer Academic Publishers: Boston, MA, 1990.

- [2.3] J. A. Storer, *Data Compression Methods and Theory*, Computer Science Press: Rockville, Maryland, 1988.

- [2.4] J. H. Witten, R. M. Neal, J. G. Cleary, "Arithmetic coding for data compression," Communications of the ACM, vol. 30, pp. 520-540.

- [2.5] T. A. Welch, " A technique for high-performance data compression," IEEE Computer Magazine, pp. 8-18, 1984.

- [2.6] J. Ziv, and A. Lempel, "Compression of individual sequences via variable-rate coding," IEEE Trans. on Information Theory, vol. IT-24, 1978.