### **USC-SIPI REPORT #258**

**Optoelectronic Sorting Networks**

by

Yibin Lu

**March 1994**

Signal and Image Processing Institute UNIVERSITY OF SOUTHERN CALIFORNIA

Department of Electrical Engineering-Systems 3740 McClintock Avenue, Room 404 Los Angeles, CA 90089-2564 U.S.A.

# **Dedication**

To my parents, for their constant love and support.

To my wife and my sons, who fulfill this journey with joy.

## Acknowledgments

First and foremost, I would like to express my deep gratitude to my advisor, Professor Alexander A. Sawchuk, for his guidance and support throughout this work. It was truly an invaluable and wonderful experience for me to work with him both intellectually and personally.

I would also like to thank my dissertation committee: Dr. P. Daniel Dapkus, Dr. B. Keith Jenkins, Dr. Alan Willner, and Dr. C-C Jay Kuo. Their effort and advice have made this work better.

I am graceful to the faculty, staff and friend in Signal and Image Processing Institute (SIPI) for their support during my years at USC. Special thanks go to my officemates and friends, Jeng-Feng Lin, Wei-Feng Hsu and his wife Syying Lee. We share many valuable discussions and great game-time. The friendship and interesting conversations from Dr. Charles Kuznia, Mr. Kuang-Yu Li, Mr. Ching-Chu Huang, and Mr. Chun-Hsiung Chuang are acknowledged.

Last but not least, I would like to express deep love to my parents and my sisters and brother for the love they have given me. Finally, my thanks and love go to my wife Shu-Wen Chang. Her continuous love, care, and support make my PhD dream come true.

### **Abstract**

This dissertation presents an optoelectronic implementation of multistage sorting networks. Volume (3-D) sorting networks which utilize the high spatial bandwidth and parallelism of optics are discussed. Designs for the diffractive optical elements (DOEs) used for the interconnections and optoelectronic compare-and-exchange (C&E) modules used for the dynamic sorting nodes are given.

The first part of this work describes the network properties of various conventional 2-D sorting networks and the development of their corresponding 3-D structures. A merge procedure is proposed for network expansion in 3-D space. A mathematical framework is established, and a detailed analysis of the network performance is given. The decision of choosing a specific network structure depends on two factors: the cost of optical elements and switching elements; and the complexity and reliability of the network.

Designs of optical interconnection systems for one-to-one linear mappings and 2-D folded shuffles are presented in the second part of this work. Our study of the characteristics of Gaussian microbeams propagating in microscaled diffractive optical elements provides a useful method for analyzing the packing limitations and light efficiency of each network structure. In our work, short and long distance linear mapping interconnections are accomplished by using microlens arrays. Various approaches are proposed to implement 2-D folded shuffles. Phase-only blazed gratings and off-axis microlenses are used for space-variant designs, and a demagnifying algorithm is proposed for space-semivariant designs. Mathematically modeled error functions are developed for performance analysis.

The last part of this dissertation describes systematic design methods for the optoelectronic 2 input/ 2 output multifunctional C&E modules. We choose smart pixel optoelectronic devices having both optical and electronic functionality for implementing the logic functions. The particular device technologies used are L-SEEDs, FET-SEEDs, and OEICs. We consider the packing density limitations due to three main factors: optical diffraction, pixel size, and power dissipation. Based on state-of-the-art technology, the analysis shows that the power dissipation of the smart pixel devices currently limits the number of modules that can be integrated in a single chip.

# **Contents**

|   | De  | dication                                    | ii    |

|---|-----|---------------------------------------------|-------|

|   | Acl | knowledgments                               | iii   |

|   | Ab  | stract                                      | iv    |

|   | Lis | t of Figures                                | ix    |

|   | Lis | t of Tables                                 | xviii |

| 1 | Int | roduction                                   | 1     |

|   | 1.1 | Motivation                                  | 1     |

|   | 1.2 | Background                                  | 2     |

|   |     | 1.2.1 Definition.                           | 2     |

|   |     | 1.2.2 Parallel Sorting Architectures        | 3     |

|   |     | 1.2.3 Interconnection Schemes               |       |

|   |     | 1.2.4 Multistage Sorting Networks           |       |

|   | 1.3 |                                             |       |

|   | 1.4 | Thesis Organization                         |       |

|   |     | Contributions                               |       |

| 2 | Pre | evious Work - A Review                      | 17    |

|   | 2.1 | Optical Interconnections                    | 18    |

|   | 2.2 | Optoelectronic Compare-and-Exchange Modules | 23    |

| 3 | Sor | ting in 3-D Networks                        | 25    |

|   | 3.1 | Background                                  | 26    |

|   |     | 3.1.1 Notation and Mapping Functions        | 25    |

|   |     | 3.1.2 Measuring Criteria                    | 27    |

|   | 3.2 | Cylindrical Spanke Sorting Networks         |       |

|   |     | 3.2.1 2-D Structures                        | 30    |

|   |     | 3.2.2 3-D Structures                        | 32    |

|   | 3.3      | Bitonic Sorting Networks                             | 37  |

|---|----------|------------------------------------------------------|-----|

|   | 3.4      | Merged Bitonic Sorting Networks                      | 40  |

|   |          | 3.4.1 2-D Structures                                 | 40  |

|   |          | 3.4.2 3-D Structures                                 | 42  |

|   |          | 3.4.3 Fundamental Operations                         | 42  |

|   |          | 3.4.4 Merging Algorithm                              | 44  |

|   | 3.5      | Network Evaluation                                   | 49  |

|   |          | 3.5.1 Running Time                                   | 49  |

|   |          | 3.5.2 Node Complexity                                | 51  |

|   |          | 3.5.3 Optical Complexity                             | 53  |

|   | 3.6      | Summary                                              | 54  |

| 4 | Lin      | ear Mapping Using Diffractive Microlenses            | 57  |

|   | 4.1      | Characteristics of Gaussian Beams                    | 57  |

|   | 4.2      |                                                      |     |

|   | 4.3      | •                                                    |     |

|   | 4.4      | Long Distance Interconnection                        | 70  |

|   | 4.5      |                                                      |     |

| 5 | 2-D      | Perfect Shuffles Using Diffractive Optical Elements  | 77  |

|   | 5.1      | Background                                           | 77  |

|   |          | 5.1.1 Shifting Properties of 2-D Folded Shuffles     | 78  |

|   |          | 5.1.2 Phase-Only Blazed Grating                      | 82  |

|   |          | 5.1.3 Binary Mask Design                             | 86  |

|   | 5.2      | Space-Variant DOE Designs                            | 88  |

|   |          | 5.2.1 Blazed Gratings                                | 89  |

|   |          | 5.2.1.1 First Design Method                          | 89  |

|   |          | 5.2.1.2 Second Design Method                         |     |

|   |          | 5.2.2 Off-Axis Microlenses                           | 109 |

|   | 5.3      | Space-Semivariant DOE Designs                        | 113 |

|   |          | 5.3.1 Four-Copy Algorithm                            |     |

|   |          | 5.3.2 One-Copy Algorithm                             |     |

|   |          | 5.3.3 Demagnifying Method                            | 115 |

|   | 5.4      | Summary                                              | 120 |

| _ |          |                                                      |     |

| 6 |          | prication Considerations for Multi-level Diffractive |     |

|   | - I lini | rical Elements                                       | 199 |

|   | 6.1   | Limited Resolution                        | 122 |

|---|-------|-------------------------------------------|-----|

|   | 6.2   | Mask Alignment Errors                     | 123 |

|   | 6.3   | Etching Depth Errors                      | 127 |

|   | 6.4   | Summary                                   |     |

| 7 | Opt   | toelectronic Compare-and-Exchange Modules | 133 |

|   | 7.1   | Design Techniques                         | 136 |

|   |       | 7.1.1 Truth Table Minimization            | 136 |

|   |       | 7.1.2 Finite State Machine                | 138 |

|   |       | 7.1.3 Latching Logic                      | 139 |

|   | 7.2   | C&E Module Designs                        |     |

|   |       | 7.2.1 L-SEEDs                             | 141 |

|   |       | 7.2.1.1 Comparison Unit                   |     |

|   |       | 7.2.1.2 Control Unit                      |     |

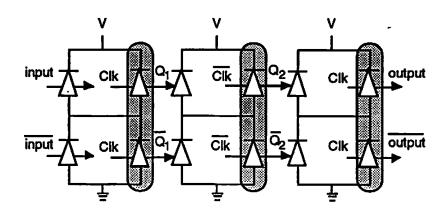

|   |       | 7.2.1.3 Shift Register                    |     |

|   |       | 7.2.1.4 Exchange Unit                     |     |

|   |       | 7.2.1.5 Analysis                          |     |

|   |       | 7.2.2 FET-SEEDs                           |     |

|   |       | 7.2.3 OEICs                               |     |

|   |       | 7.2.4 Performance                         |     |

|   | 7.3   | Packing Density.                          |     |

|   |       | 7.3.1 Module Size                         |     |

|   |       | 7.3.2 Power Dissipation                   |     |

|   | 7.4   | Summary                                   |     |

| 8 | Cor   | iclusions and Future Work                 | 164 |

|   | 8.1   | Conclusions                               | 164 |

|   | 8.2   | Future Work                               |     |

|   |       |                                           |     |

| R | efere | ence                                      | 168 |

# List of Figures

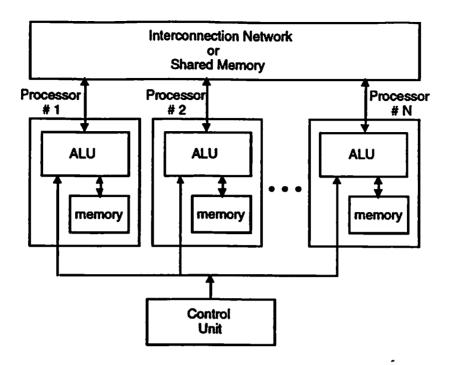

| 1.1 | SIMD computing system                                                                                                                                                                                                                                                                                                                                                                                                       | 4  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

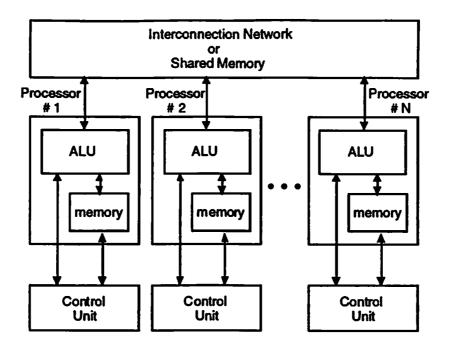

| 1.2 | MIMD computing system                                                                                                                                                                                                                                                                                                                                                                                                       | 5  |

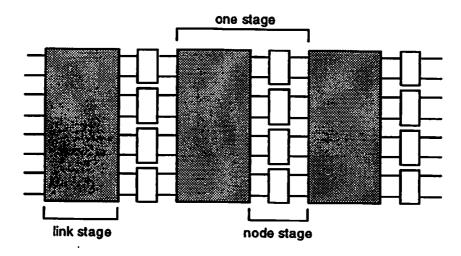

| 1.3 | 2-D multistage sorting network                                                                                                                                                                                                                                                                                                                                                                                              | 8  |

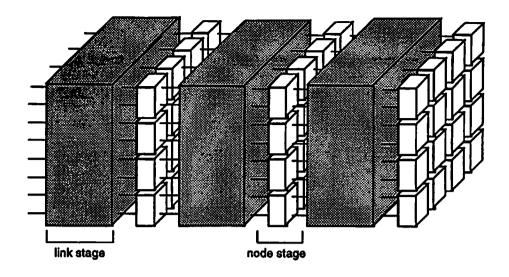

| 1.4 | 3-D multistage sorting network                                                                                                                                                                                                                                                                                                                                                                                              | 9  |

| 1.5 | 1-D perfect shuffle                                                                                                                                                                                                                                                                                                                                                                                                         | 10 |

| 1.6 | 2-D separable shuffle                                                                                                                                                                                                                                                                                                                                                                                                       | 10 |

| 1.7 | 2-D folded shuffle                                                                                                                                                                                                                                                                                                                                                                                                          | 11 |

| 1.8 | Three basic functions of a C&E module. (a) bypass function. (b) minsort function. (c) maxsort function                                                                                                                                                                                                                                                                                                                      | 11 |

| 1.9 | Thesis organization                                                                                                                                                                                                                                                                                                                                                                                                         | 13 |

| 3.1 | Odd-even transposition sorting network with inputs $N=4$                                                                                                                                                                                                                                                                                                                                                                    | 30 |

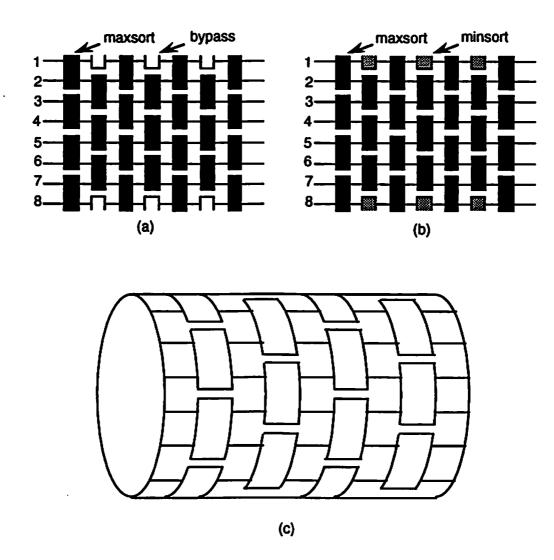

| 3.2 | Architecture of the cylindrical Spanke network (a) type I drawn in a 2-D structure; (b) type II drawn in a 2-D structure; (c) network wrap around in 3-D space. The boxes in (a) and (b) represent individual 2 input/ 2 output C&E modules, the half open boxes represent modules that wrap around and connect input 1 and 8. The black, gray and white colors represent maxsort, minsort and bypass function respectively | 31 |

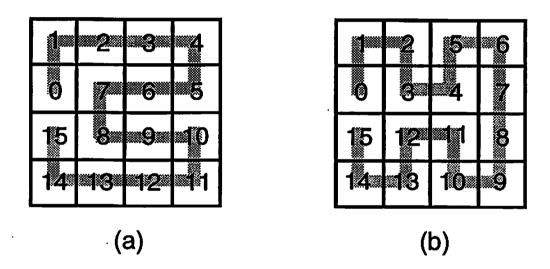

| 3.3 | Sixteen channels are arranged in two types of serpentine raster indexings                                                                                                                                                                                                                                                                                                                                                   | 32 |

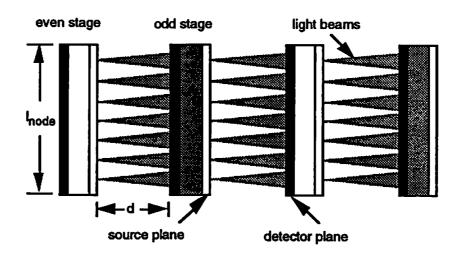

| 3.4 | The 2-D arrangement of 2 input/ 2 output C&E modules for odd and even node stages                                                                                                                                                                                                                                                                                                                                           | 34 |

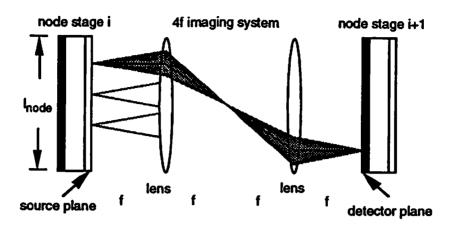

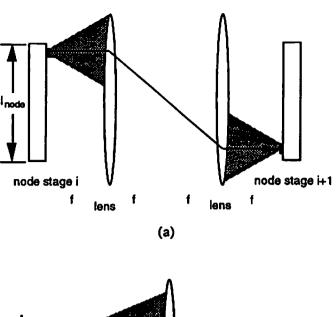

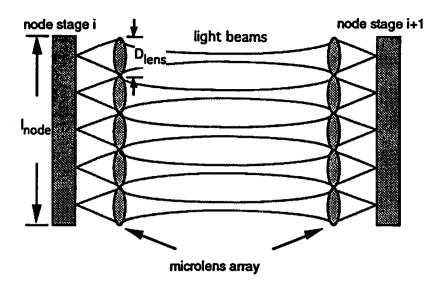

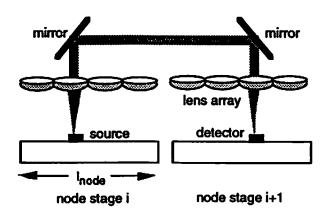

| 3.5        | One-to-one imaging interconnects using 4f imaging systems                                                                                                                                                                                                                                               | 38 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.6        | Directly coupled structure of a one-to-one linear mapping interconnection system                                                                                                                                                                                                                        |    |

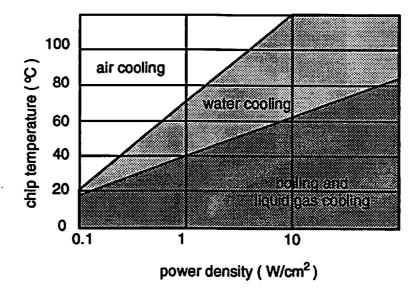

| 3.7        | Cooling regimes of various cooling technologies                                                                                                                                                                                                                                                         | 36 |

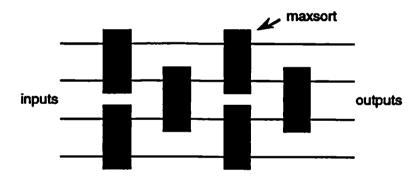

| <b>3.8</b> | Bitonic sorting network based on 1-D perfect shuffle interconnections. Boxes drawn with different shadings represent 2 input/2 output C&E modules performing different functions. Black represents the maxsort function, gray represents the minsort function, and white represents the bypass function | 37 |

| 3.9        | 3-D bitonic sorting network                                                                                                                                                                                                                                                                             | 39 |

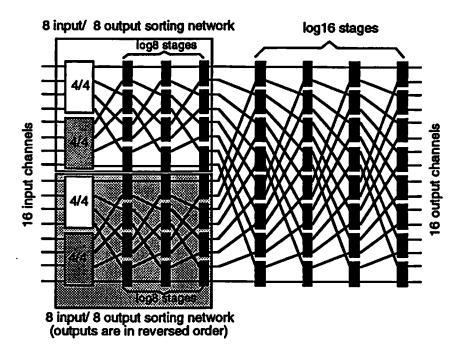

| 3.10       | A 16 input/ 16 output sorting network merged from four 4 input/ 4 output sorting networks. The sorted outputs of the sorting networks bounded by gray boxes are in reversed order                                                                                                                       | 41 |

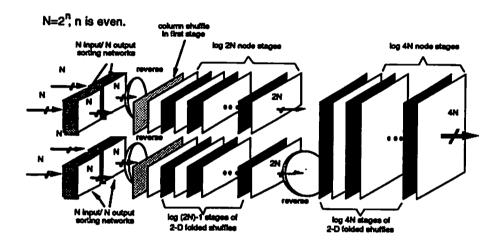

| 3.11       | A 3-D 4N input/4N output sorting network merged from four 3-D N input/N output sorting networks                                                                                                                                                                                                         | 42 |

| 3.12       | 2-D input signal array is reversed by using imaging system                                                                                                                                                                                                                                              | 45 |

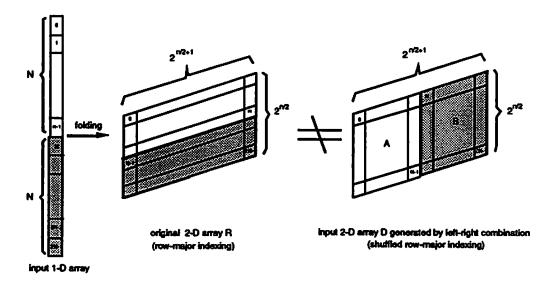

| 3.13       | The 2-D signal array generated using left-right combination has a shuffled row-major indexing instead of its original row-major indexing.                                                                                                                                                               | 46 |

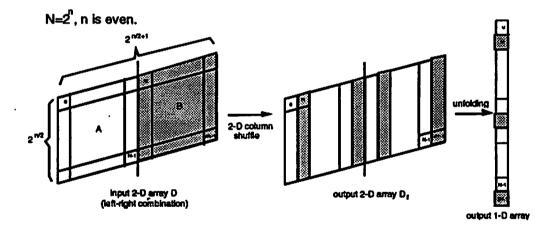

| 3.14       | Left-right combination of two $N \times N$ networks column shuffled in 3-D space                                                                                                                                                                                                                        | 47 |

| 3.15       | System structure of two $N \times 2N$ networks merged into one $2N \times 2N$ network in 3-D space                                                                                                                                                                                                      | 48 |

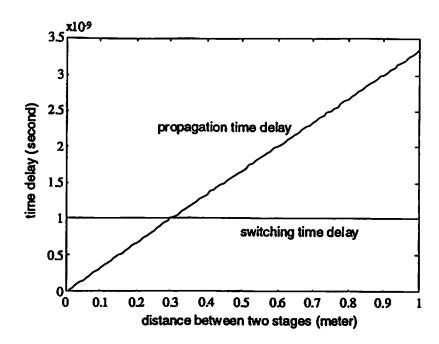

| 3.16       | The comparison between the propagation time delay and the switching time delay based on different value of $d$                                                                                                                                                                                          | 50 |

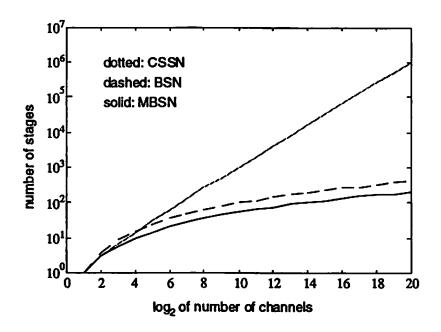

| 3.17       | Total number of node stages versus $\log_2$ of number of channels for three kinds of sorting networks. CSSN represents the cylindrical Spanke network; BSN represents the bitonic sorting                                                                                                               |    |

|      | network; MBSN represents the merged bitonic sorting network                                                                                                                                                                                                                                                                                                                                     | 50 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

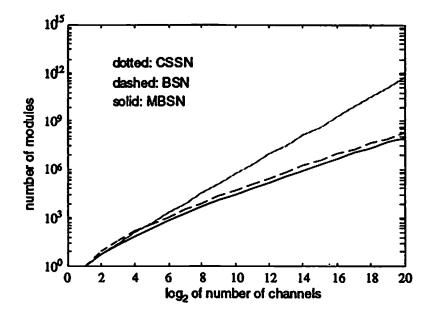

| 3.18 | Total number of 2 input/2 output C&E modules versus log <sub>2</sub> of the number of channels for three kinds of sorting networks. CSSN represents the cylindrical Spanke network; BSN represents the bitonic sorting network; MBSN represents the merged bitonic sorting network                                                                                                              | 52 |

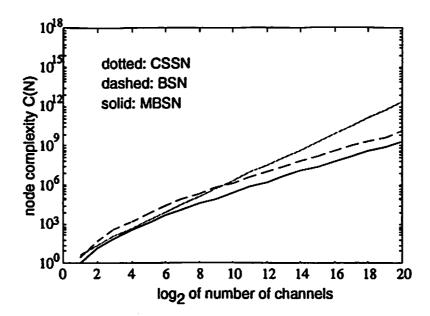

| 3.19 | The node complexity versus $\log_2$ of the number of channels for three kinds of sorting networks. CSSN represents the cylindrical Spanke network; BSN represents the bitonic sorting network; MBSN represents the merged bitonic sorting network                                                                                                                                               | 53 |

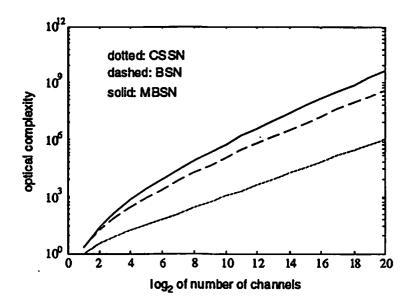

| 3.20 | The optical complexity versus $\log_2$ of the number of channels for three kinds of sorting networks. CSSN represents the cylindrical Spanke network; BSN represents the bitonic sorting network; MBSN represents the merged bitonic sorting network                                                                                                                                            | 54 |

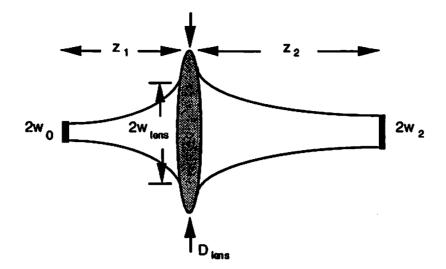

| 4.1  | The characteristics of Gaussian beam propagating and focusing.                                                                                                                                                                                                                                                                                                                                  | 58 |

| 4.2  | Different architectures of imaging systems for linear mapping interconnections having a total length of 4f                                                                                                                                                                                                                                                                                      | 61 |

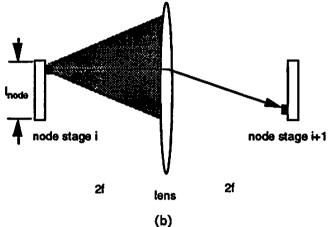

| 4.3  | The lens diameter required to capture 99% of an incident Gaussian beam emitted by a light source with a $5 \mu m \times 5 \mu m$ active area and Gaussian distribution after propagation over a distance $f$ . The horizontal axis is plotted as a function of $f$ -number. Also shown is a typical vertical size $(10 mm)$ of a node stage $(l_{node})$ which will be used in later discussion | 62 |

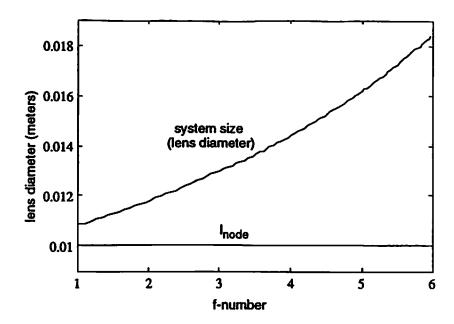

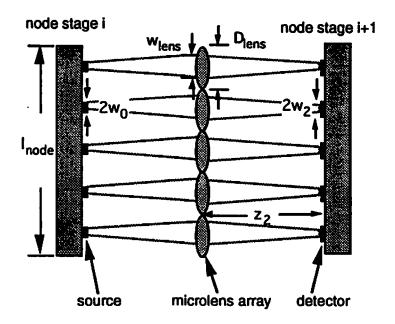

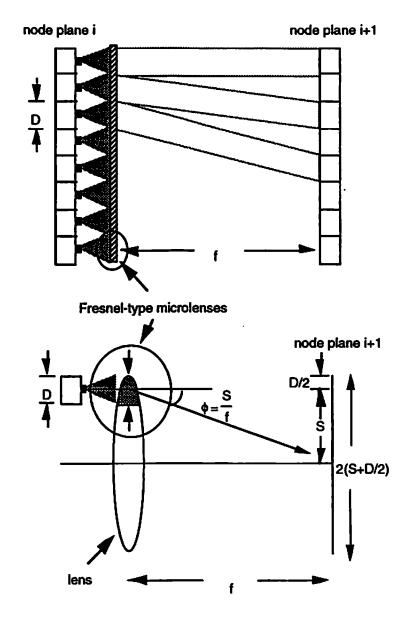

| 4.4  | A linear mapping interconnection system using microlens arrays                                                                                                                                                                                                                                                                                                                                  | 63 |

| 4.5  | Short distance linear mapping system using single microlens array                                                                                                                                                                                                                                                                                                                               | 64 |

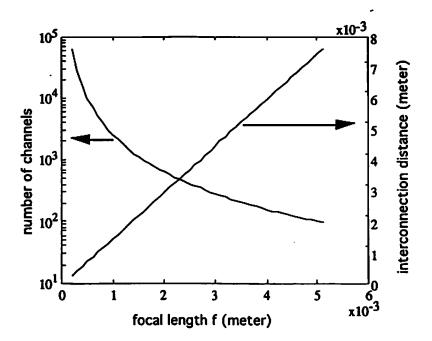

| 4.6  | The number of channels (left vertical scale), and interconnection distance (right vertical scale) versus focal length $f$ . Here we assume the size of node plane is $10  mm \times 10  mm$ , $f$ -number $F\#=5$ , $\lambda=0.8  \mu m$ , and macrolens clipping ratio $k=2$                                                                                                                   | 66 |

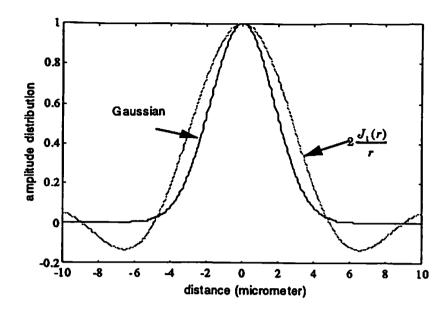

| 4.7  | Gaussian distribution and lens diffraction curves on the detector plane. Here, $w_0=5~\mu m$ , $F\#=5$ , and $\lambda=0.8~\mu m$                                                                                                                  | 68 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

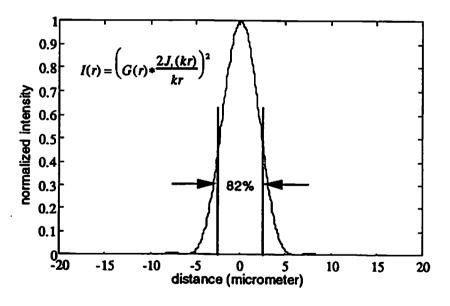

| 4.8  | The intensity distribution of the convolution result. Here, $w_0 = 5 \ \mu m$ , $F\#=5$ , and $\lambda = 0.8 \ \mu m$ . The power focusing on the $5 \ \mu m$ center areas is 82%                                                                 | 68 |

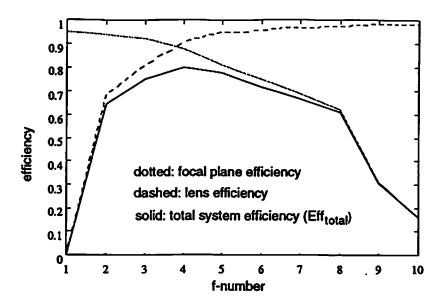

| 4.9  | The variation of different efficiencies based on f-number. Here, $w_0 = 5 \ \mu m$ , and $\lambda = 0.8 \ \mu m$                                                                                                                                  | 69 |

| 4.10 | Interconnection structure for reflection type devices using an imaging system with a pair of microlens arrays                                                                                                                                     | 70 |

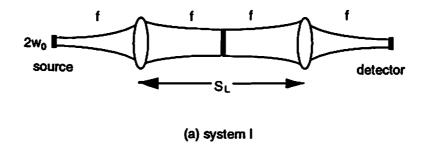

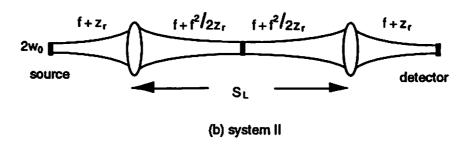

| 4.11 | Two types of long-distance linear mapping systems. Both image the source plane to the detector plane                                                                                                                                              | 71 |

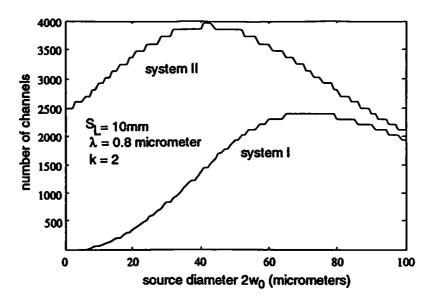

| 4.12 | The maximum number of channels of two types of systems as a function of source diameter $2w_0$                                                                                                                                                    | 72 |

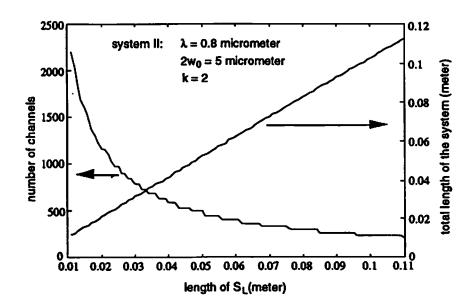

| 4.13 | The maximum number of channels and the total length of the system is plotted as a function of the length $S_L$                                                                                                                                    | 73 |

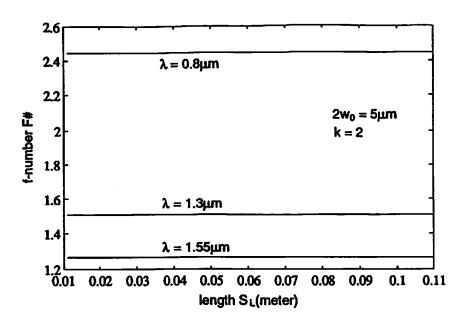

| 4.14 | The required $f$ -number of the microlens as a function of different wavelengths $\lambda$ and length $S_L$                                                                                                                                       | 74 |

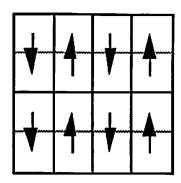

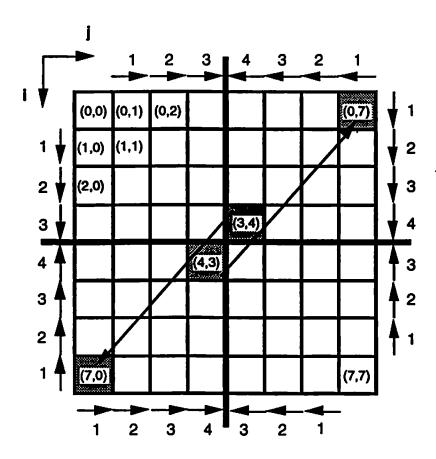

| 5.1  | The shift property of the 2-D folded shuffle in a plane with 64 channels. The arrows around each quadrant represent the shift directions of the rows or columns in that quadrant and the number on the arrows indicates the distance of the shift | 80 |

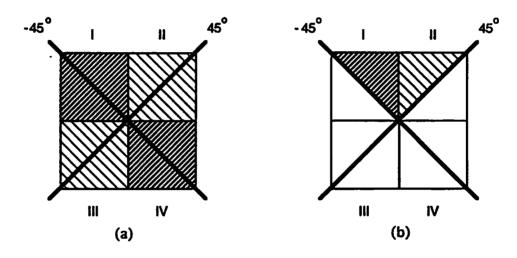

| 5.2  | (a) Reflected-symmetric property of 2-D folded shuffle. (b) Basic pattern to be duplicated                                                                                                                                                        | 81 |

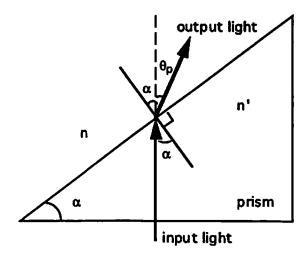

| 5.3  | Normally incident plane wave refracted by a bulk prism                                                                                                                                                                                            | 82 |

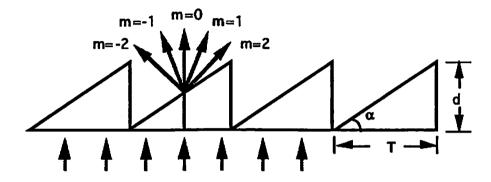

| 5.4  | Phase-only blazed grating made by microprisms. Normally incident plane wave is diffracted to a set of beams with different angle                                                                                                                  | 84 |

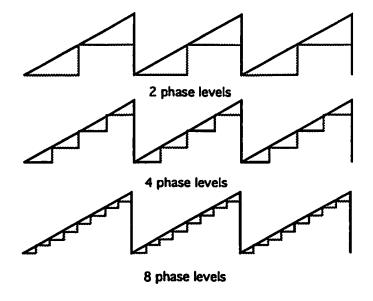

| 5.5  | Multi-level structures of blazed gratings                                                                                                                                                                               | 87  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

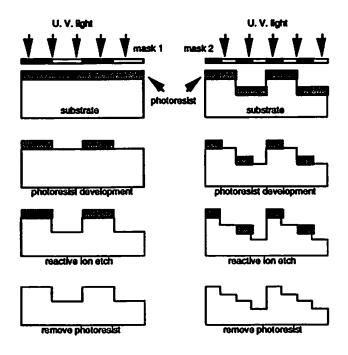

| 5.6  | The fabrication procedure of a four-level grating pattern utilizing two binary masks                                                                                                                                    | 87  |

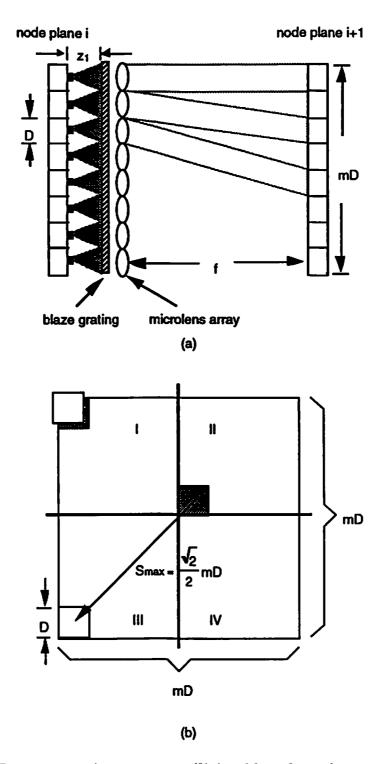

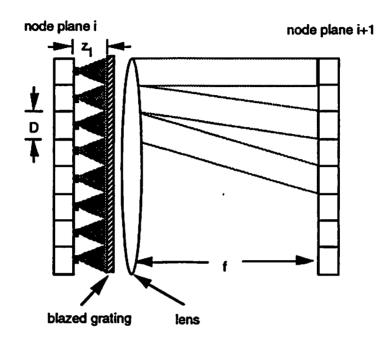

| 5.7  | Interconnection system utilizing blazed gratings and microlens arrays. (a) 1-D system structure; (b) gray and white boxes represent the location of cells before and after a 2-D folded shuffle operation, respectively | 90  |

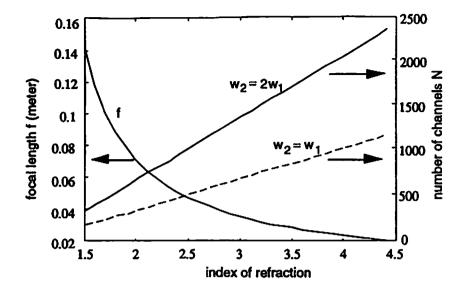

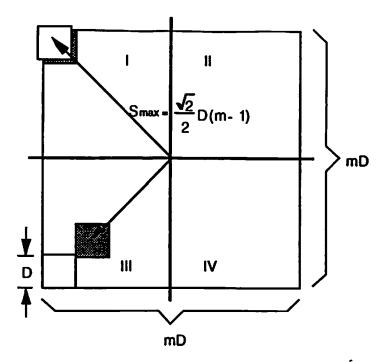

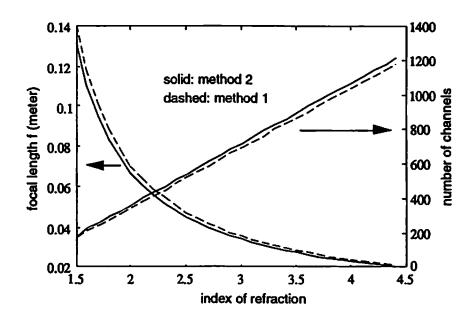

| 5.8  | Total number of channels $N$ and focal length are plotted as a function of the index of refraction. Two criteria $w_2 = w_1$ and $w_2 = 2w_1$ are used                                                                  | 93  |

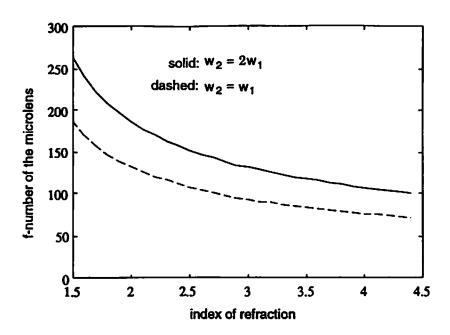

| 5.9  | $f$ -number of the microlens is plotted as a function of the index of refraction. Two criteria $w_2 = w_1$ and $w_2 = 2w_1$ are used                                                                                    | 94  |

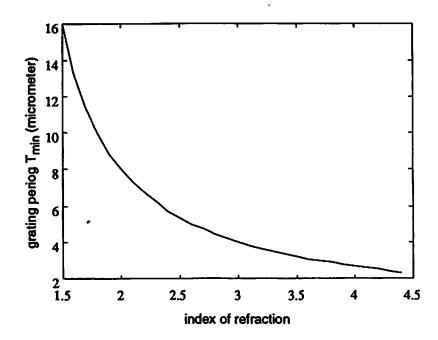

| 5.10 | Minimum grating period $T_{\min}$ is plotted as a function of the index of refraction                                                                                                                                   | 94  |

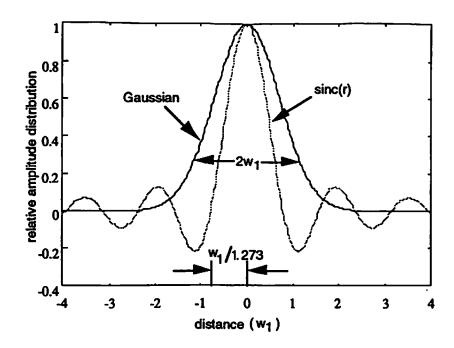

| 5.11 | The PSFs of the Gaussian beam and sinc function at the back focal plane. Here, $w_1 = 1.273\rho$ is equal to the size of the each channel                                                                               | 96  |

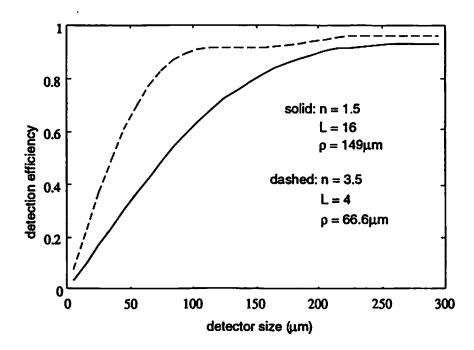

| 5.12 | The detection efficiency of four-level and sixteen-level gratings versus detector size                                                                                                                                  | 96  |

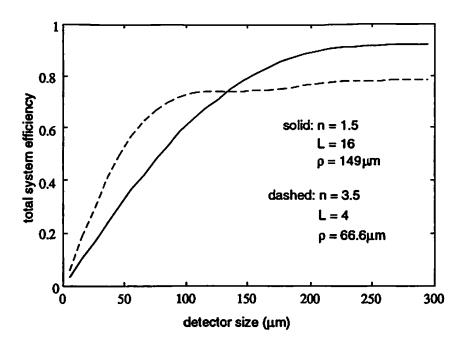

| 5.13 | The total system efficiency of four-level $(n = 3.5)$ and sixteen-level $(n = 1.5)$ gratings versus detector size                                                                                                       | 97  |

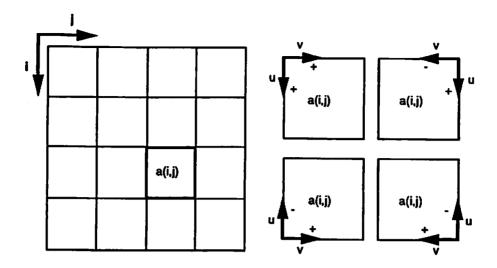

| 5.14 | The location of reference point in each cell $a(i,j)$ during the phase profile design is determined by the positive or negative directions of two vectors $\vec{u}$ and $\vec{v}$                                       | 99  |

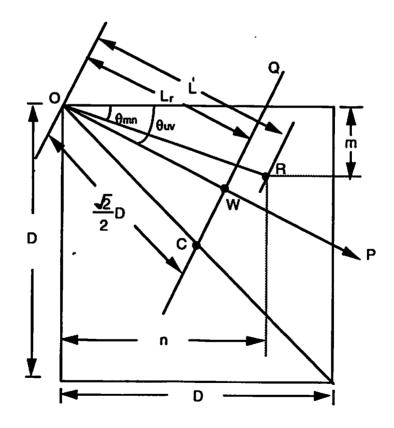

| 5.15 | The geometric relation of a point $R$ in a particular cell                                                                                                                                                              | 99  |

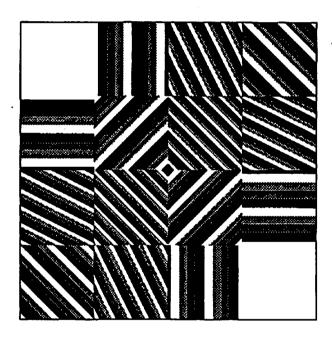

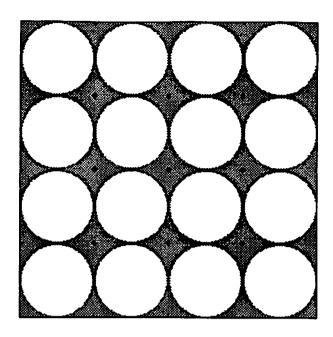

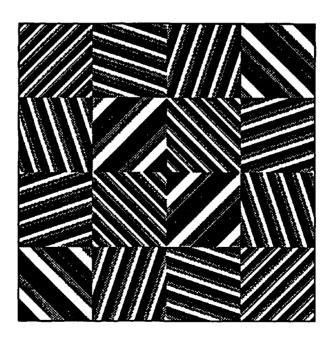

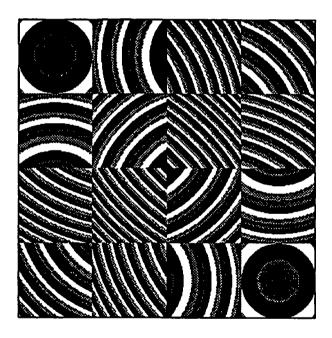

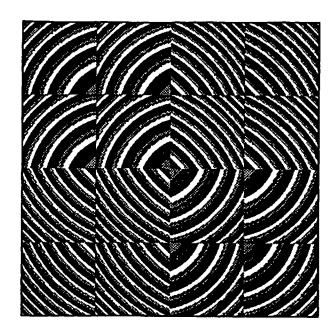

| 5.16 | An array of computer-generated 4×4 four-level blazed grating profiles based on the first design method                                                                                                                  | 101 |

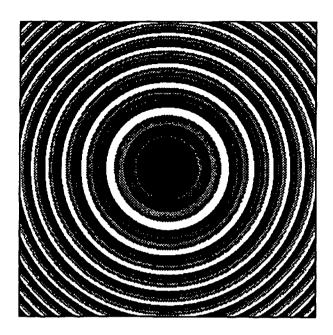

| 5.17 | An array of computer-generated $4 \times 4$ microlenses profiles. Due to high $f$ -number of the macrolens, lens profiles can only be quantized into three levels in each cell                                                                                                                                                                              | 102 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.18 | Four-level DOE patterns based on the first blazed grating design method                                                                                                                                                                                                                                                                                     | 102 |

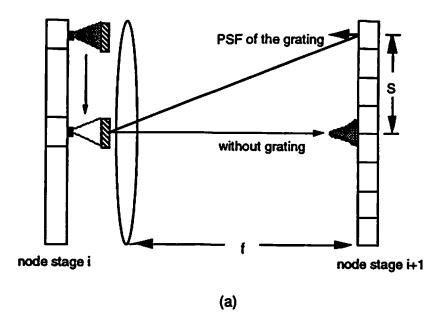

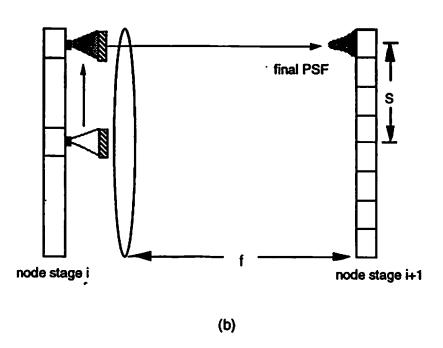

| 5.19 | 1-D interconnection system structure utilizing blazed gratings and a large lens                                                                                                                                                                                                                                                                             | 103 |

| 5.20 | The grating design method for the new system structure: (a) The grating pattern of the cell is generated by calculating the distance between the center point of the node stage $i+1$ and the center point of the destination cell; (b) cell is moved to its original location and the intensity distribution of PSFs at the Fourier plane remain unchanged | 104 |

| 5.21 | The shifting of each cell based on the second design method. Gray and white boxes represent the location of cells before and after a 2-D folded shuffle operation, respectively                                                                                                                                                                             | 106 |

| 5.22 | The total number of channels and the longitudinal size of the systems based on two design methods are compared                                                                                                                                                                                                                                              | 106 |

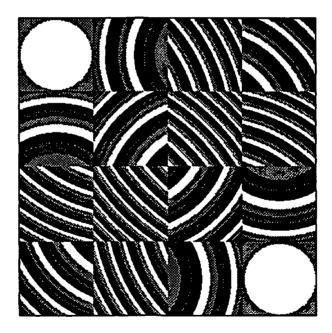

| 5.23 | An array of computer-generated $4 \times 4$ four-level blazed grating profiles based on the second design method                                                                                                                                                                                                                                            | 107 |

| 5.24 | A computer-generated $4 \times 4$ four-level macrolens profile                                                                                                                                                                                                                                                                                              | 108 |

| 5.25 | Four-level DOE pattern based on the second blazed grating design method                                                                                                                                                                                                                                                                                     | 108 |

| 5.26 | 1-D perfect shuffle interconnection system structure using off-axis microlenses                                                                                                                                                                                                                                                                             | 110 |

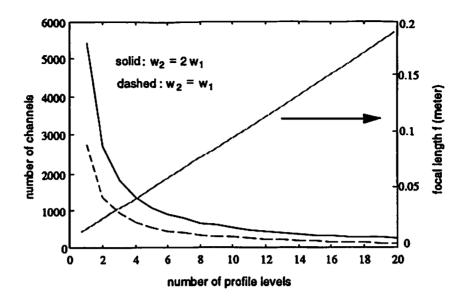

| 5.27 | Total number of channels and focal length versus number of profile levels. Two criteria $w_2 = w_1$ and $w_2 = 2w_1$ are used                                                                                                                                                                                                                               | 111 |

| 5.28 | An array of computer-generated 4×4 four-level off-axis                                                                                                                                                                                                                                                                                                      |     |

|      | microlenses profile                                                                                                                                                                                                                                                                                                                                                                                                                  | 112 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

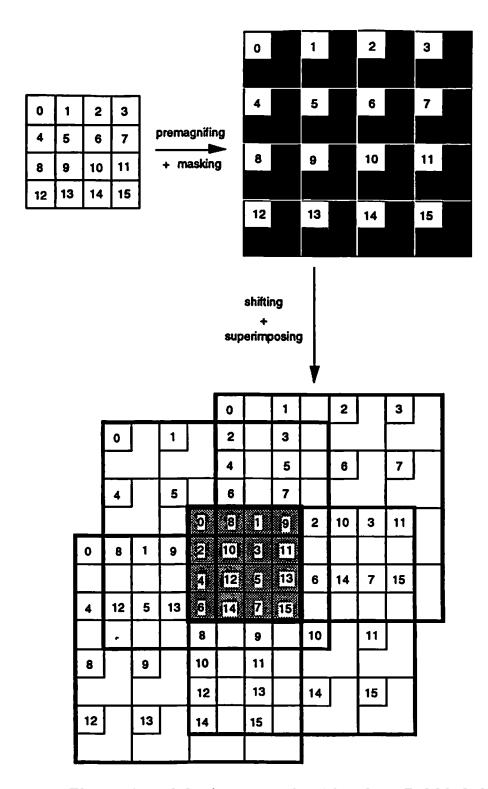

| 5.29 | Illustration of the four-copy algorithm for 2-D folded shuffle.<br>Only the shaded section in the last part of the figure is retained.                                                                                                                                                                                                                                                                                               | 114 |

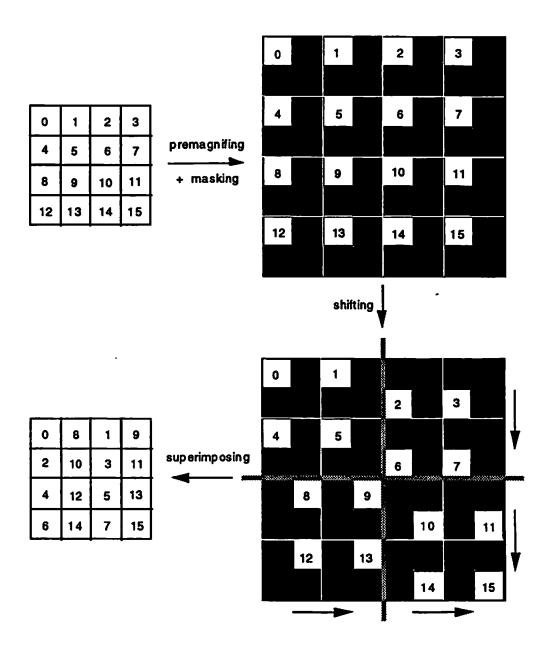

| 5.30 | Illustration of one-copy algorithm for 2-D folded shuffle                                                                                                                                                                                                                                                                                                                                                                            | 116 |

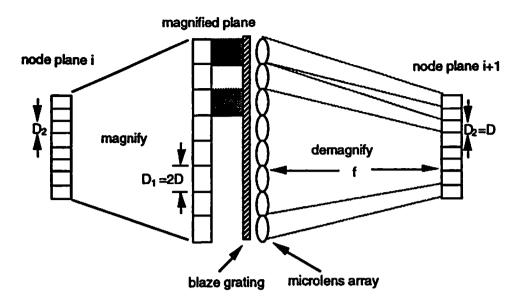

| 5.31 | Illustration of the demagnifying method for achieving a 1-D perfect shuffle                                                                                                                                                                                                                                                                                                                                                          | 117 |

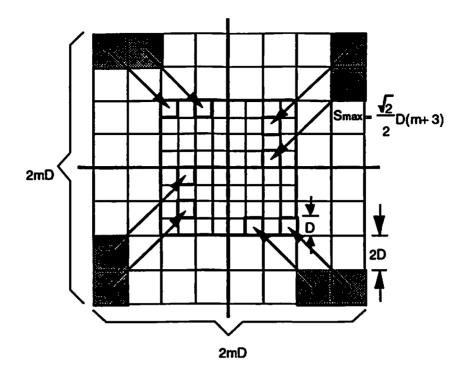

| 5.32 | Illustration of shifting properties of the demagnifying design method in 2-D plane. Gray and white boxes represent the location of cells before and after the operation, respectively. Note that a demagnification of two is utilized to perform a 2-D folded shuffle                                                                                                                                                                | 118 |

| 5.33 | An array of computer-generated $4 \times 4$ four-level DOE profiles based on the demagnification method                                                                                                                                                                                                                                                                                                                              | 120 |

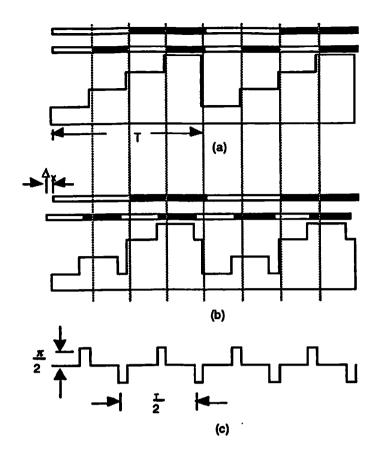

| 6.1  | Effect of mask alignment in multi-level phase profile generation: (a) the ideal 4-level( $K=2$ ) phase profile as a function of position; (b) the phase profile obtained if the second mask is misaligned by an amount $\Delta_z$ ; (c) the effect of the misalignment is equivalent to the phase difference function shown here as a periodic grating with period $T/2$ , duty cycle $\alpha = \Delta_x/T$ , and phases $\pm \pi/2$ | 124 |

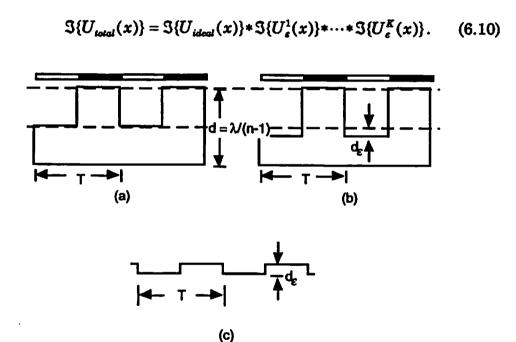

| 6.2  | Effect of etching depth errors in the multi-level phase profile generation: (a) the ideal 2-level profile, (b) the profile obtained if an etching depth error with an amount of $d_{\varepsilon}$ is occurred, (c) the effect of the etching depth error is equivalent to adding a periodic grating in the phase domain with period $T$ , duty cycle 50%, and a phase delay $2\pi d_{\varepsilon}/d$ , where $d=\lambda/(n-1)$       | 128 |

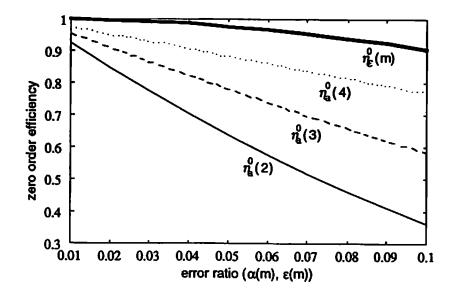

| 6.3  | The effects of misalignments and etching depth errors is plotted as a function of error ratio proportional to $T$ and $d$ , respectively                                                                                                                                                                                                                                                                                             | 131 |

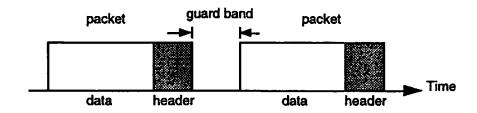

| 7.1  | Data format for packet switching scheme                                                                                                                                                                                                                                                                                                                                                                                              | 133 |

| 7.2  | Synchronized packet switching system                                                                                                                                                                                                                              | 134 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

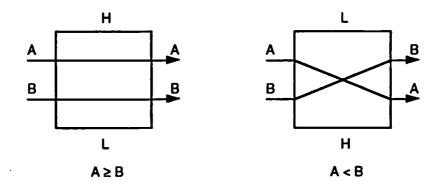

| 7.3  | The 2 input/ 2 output compare-and-exchange switching module                                                                                                                                                                                                       | 134 |

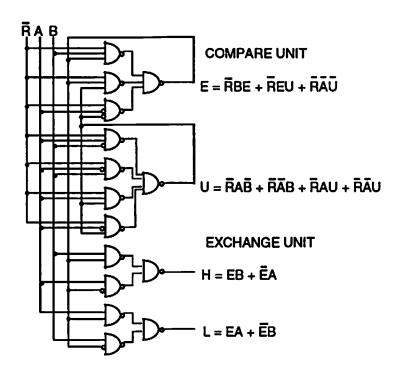

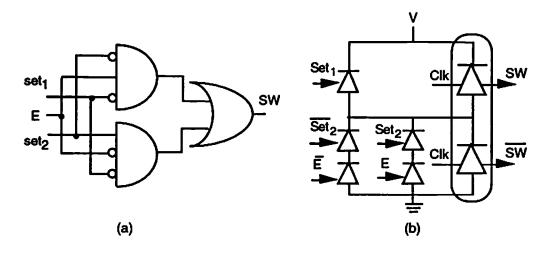

| 7.4  | Compare-exchange NAND gate logic based on truth table minimization techniques                                                                                                                                                                                     | 136 |

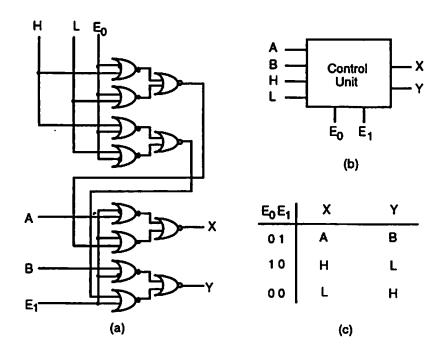

| 7.5  | control unit based on truth table minimization. (a) NOR gate logic, (b) block diagram, and (c) operation table                                                                                                                                                    | 137 |

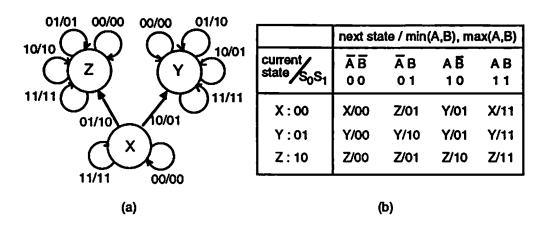

| 7.6  | State transition diagram (a) and state transition table (b) for a compare-exchange unit. The label pairs in the state transition diagram represent the relation between the logic state of the two inputs $A$ and $B$ and two outputs $\min(A,B)$ and $\max(A,B)$ | 138 |

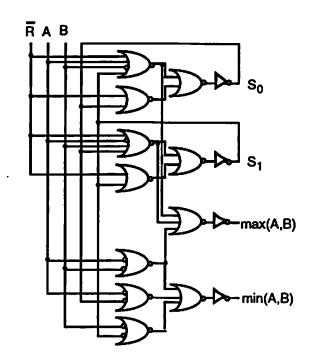

| 7.7  | NOR logic implementation of the state machine of the compare-<br>exchange unit                                                                                                                                                                                    | 139 |

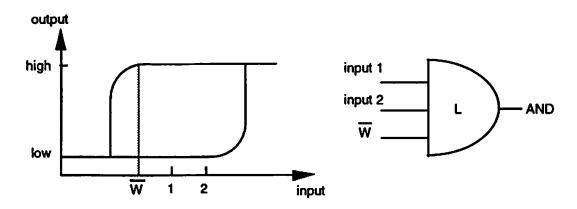

| 7.8  | Transfer function of a latching AND gate                                                                                                                                                                                                                          | 140 |

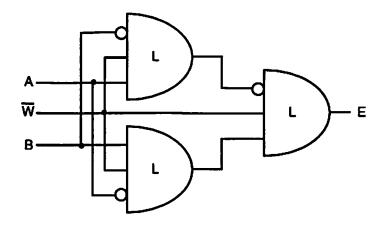

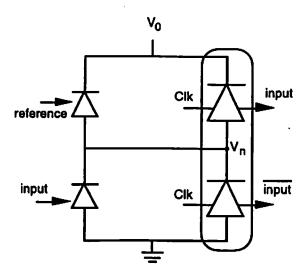

| 7.9  | Latching AND gate implementation of the comparison unit                                                                                                                                                                                                           | 141 |

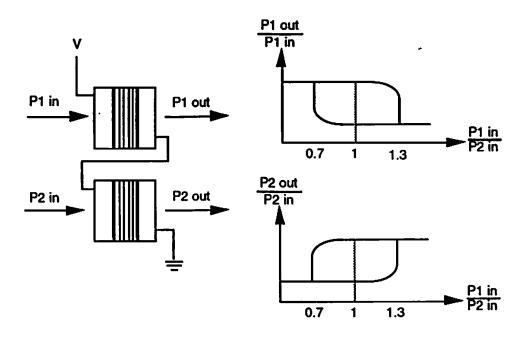

| 7.10 | Symmetric SEED and its input/output characteristic curve                                                                                                                                                                                                          | 142 |

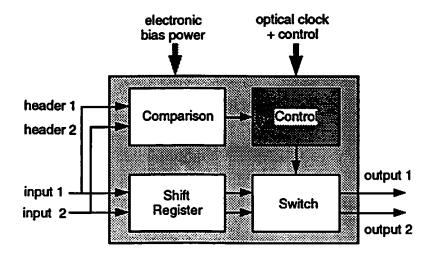

| 7.11 | Block diagram of a multifunctional C&E module based on L-SEEDs                                                                                                                                                                                                    | 143 |

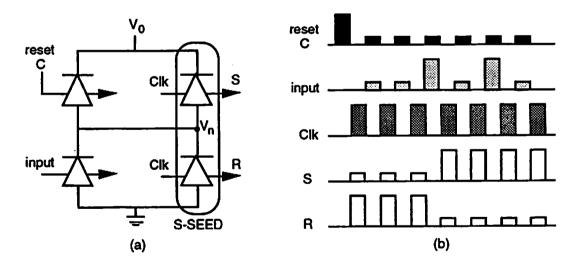

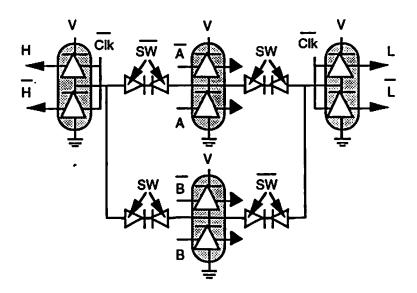

| 7.12 | (a) Latching circuitry based on L-SEEDs; (b) Timing diagram of the L-SEEDs latching circuitry. The diode symbol in the latching circuit represents MQW diodes as in Fig. 7.10                                                                                     | 144 |

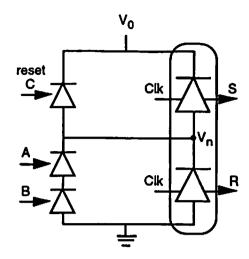

| 7.13 | Latching AND gate based on L-SEEDs                                                                                                                                                                                                                                | 145 |

| 7.14 | Dual-rail signal generator for L-SEEDs circuitry                                                                                                                                                                                                                  | 146 |

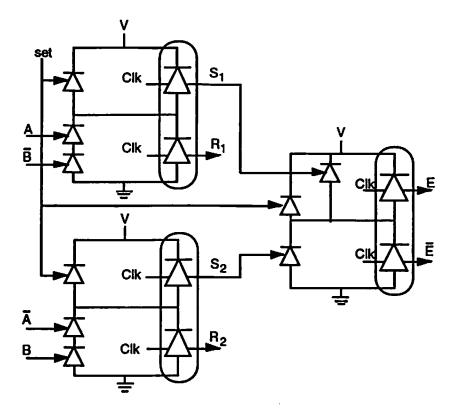

| 7.15 | The comparison unit based on L-SEEDs circuits                                                                                                                                                                                                                     | 147 |

| 7.16 | a) Logic circuit for the control unit; (b) The circuit of the control unit based on L-SEEDs                                                                                                                                                                       | 148 |

| 7.17 | A three-stage shift register based on L-SEEDs                                                                              | 149 |

|------|----------------------------------------------------------------------------------------------------------------------------|-----|

| 7.18 | The exchange unit based on L-SEEDs                                                                                         | 150 |

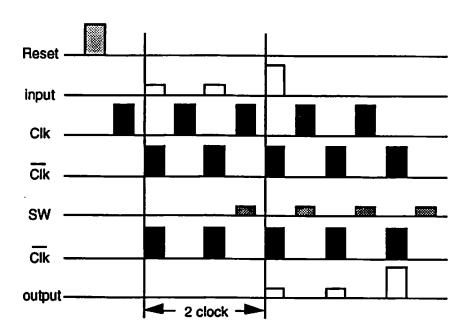

| 7.19 | Timing diagram of the L-SEEDs C&E module                                                                                   | 151 |

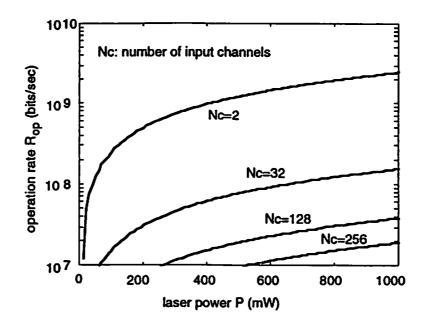

| 7.20 | Relations between operation rate, laser power, and number of input channels in an L-SEEDs-based sorting system             | 153 |

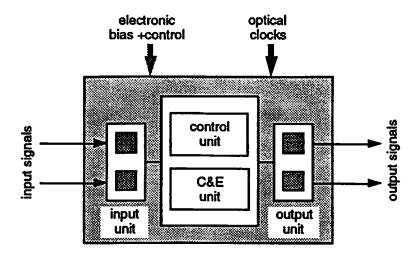

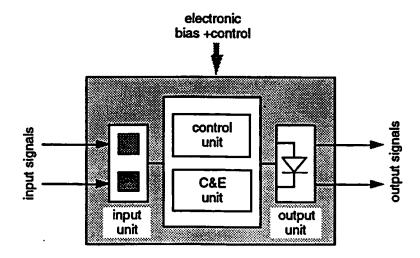

| 7.21 | Block diagram of a multifunctional C&E module based on FET-SEEDs                                                           | 155 |

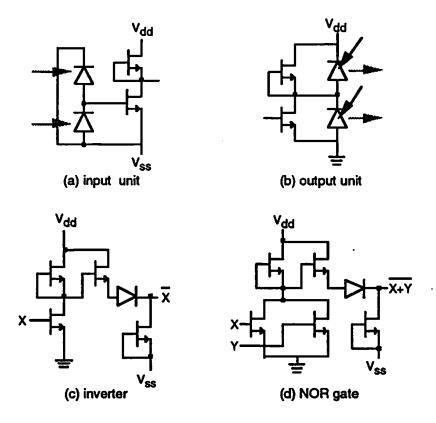

| 7.22 | Schematic diagrams of FET-SEED circuits; (a) input unit, (b) output unit, (c) inverter, and (d) 2 input/ 1 output NOR gate | 156 |

| 7.23 | Block diagram of a multifunctional C&E module based on OEICs                                                               | 157 |

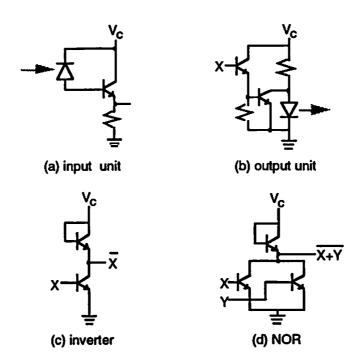

| 7.24 | Schematic diagrams of OEICs; (a) input unit, (b) output unit, (c) inverter, and (d) 2 input/ 1 output NOR gate             | 158 |

# List of Tables

| 1.1 | architectures based on the number of cycles to accomplish a group of FUPs                                                                                                               | 7   |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2 | Performance comparison of three types of interconnection architectures based on the number of cycles to accomplish a sorting operation.                                                 | 7   |

| 3.1 | The optical complexity of optical interconnection systems is classified by the degree of space-variance                                                                                 | 29  |

| 3.2 | The node complexity of all three types of sorting networks                                                                                                                              | 51  |

| 3.3 | The optical complexity of all three types of sorting networks                                                                                                                           | 54  |

| 3.4 | The evaluating results of all three types of sorting networks                                                                                                                           | 55  |

| 4.1 | Summary of short-distance and long-distance (System II) linear mapping systems using microlens arrays. It is assumed that a minimum number of 10 <sup>3</sup> channels can be supported | 76  |

| 5.1 | The first order diffraction efficiency $\eta_1$ of multi-level phase grating $\phi_g$ is calculated for a different number of phase levels                                              | 88  |

| 5.2 | The numerical results of the first method using blazed gratings and microlenses                                                                                                         | 97  |

| 5.3 | The numerical results of the second method using blazed gratings and a large lens                                                                                                       | 107 |

| 5.4 | Numerical results giving the maximum number of channels for<br>the design method using off-axis microlenses                                                                             | 113 |

| 5.5 | The numerical results of the demagnification method using first blazed grating design method                                                                                     | 119 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.6 | Summary of 2-D perfect shuffle interconnection designs based on a 4-level phase diffractive optical element                                                                      | 121 |

| 5.7 | Summary of 2-D perfect shuffle interconnection designs based on a 16-level phase diffractive optical element                                                                     | 121 |

| 6.1 | Zero order efficiencies of extra grating profiles in the last three layers of a 16-level grating profile are calculated as a function of $\alpha$ , ratio of the alignment error | 127 |

| 6.2 | Numerical results of $\eta_{\varepsilon}^{0}$ of a single layer as a function of $\varepsilon(m)$ , the error ratio                                                              | 130 |

| 7.1 | The functions of the control circuit. "\" represents the don't care condition                                                                                                    | 148 |

| 7.2 | Summary of the performance of the C&E module design based on three device technologies                                                                                           | 159 |

| 7.3 | Summary of module packing density based on power dissipation                                                                                                                     | 162 |

| 7.4 | Summary of packing density based on various constraints                                                                                                                          | 163 |

# Chapter 1

## Introduction

#### 1.1 Motivation

With the growing number of areas in which computers are being used, there is an ever-increasing demand for more information processing power than today's machines can deliver. Extremely fast electronic computers and communication networks are being sought for many applications to process enormous quantities of data in reasonable amounts of time. However, it is becoming apparent that it will very soon be impossible to achieve significant increase in speed by simply using faster electronic devices, as was done in the past three decades. This is due, on one hand, to the fact that with today's superfast VLSI circuits more time is needed for data to travel between two devices than it takes for it to be processed by either of them. On the other hand, the reduction of distance between devices through very large scale integration is quickly reaching a limit beyond which the reliability and speed of circuit elements decrease [1].

An alternative solution to achieve very high processing capacity is to use parallel system architectures. Here, different processing units are locally or globally interconnected and they process the information simultaneously. Unfortunately, potential packaging and interconnection bottlenecks of electronic VLSI circuits prevent the development of high density parallel systems. As a result, extensive research efforts have been directed towards free space optoelectronic technologies which utilize the inherent parallelism of optics to provide solutions to the interconnection bottleneck problem. The goal of this research is to explore the potential of utilizing current optoelectronic technologies to construct a special-purpose, 2-D parallel computing architecture, named a sorting network, to transform it into an equivalent 3-D volume architecture, and to evaluate its performance in various ways.

#### 1.2 Background

#### 1.2.1 Definition

The chosen problem of this research is based on the concept of sorting. Let us begin by giving a formal definition of sorting.

Definition 1.1 A set of elements are said to satisfy a linear order "<" if and only if

- 1. for any two elements a and b, either a < b, a = b, or b < a.

- 2. for any three elements a, b, and c, if a < b and b < c, then a < c.

The linear order "<" is usually read "precedes."

**Definition 1.2** Given a sequence  $S = \{x_1, x_2, ..., x_n\}$  of n items on which a linear order is defined, the purpose of sorting is to arrange the elements of S into a new sequence  $S' = \{x'_1, x'_2, ..., x'_n\}$  such that  $x'_i < x'_{i+1}$  for i = 1, 2, ..., n-1.

To get an intuitive understanding of this definition, S can be thought of as a sequence of names to be arranged in alphabetical order. Another example is a sequence of numbers to be arranged in non decreasing order.

#### 1.2.2 Parallel Sorting Architectures

For both practical and theoretical reasons, sorting is one of the most common tasks in general-purpose computation. It was estimated that one fourth of all computer time was devoted to sorting [2]. For example, databases and expert systems often sort the elements of a data structure to simplify searching and the addition of new elements. Furthermore, data manipulation operations like projection, set union, and intersection can be directly implemented by modified sorting algorithms [3]. With the tremendous demand for faster computing speed, and the sharp decline in the price of processing elements, the era of parallel computing systems was born. In the case of sorting we distinguish between two general approaches: multipurpose parallel structures and special-purpose parallel architectures [4].

Multipurpose parallel architectures are destined for computing systems with a broad range of applications. These are usually classified into one of two main categories: single instruction stream multiple data stream

Figure 1.1: SIMD computing system.

(SIMD) computing systems and multiple instruction stream multiple data stream (MIMD) computing system.

An SIMD computing system consists of a number of processors operating under the control of a single instruction stream provided by a central control unit. Figure 1.1 shows the structure of an SIMD computing system with the input and output units omitted. In order to sort a set of data, each processor loads programs and different data into its local memory. During a given time unit, a selected number of processors are active and execute the same instructions such as comparison, addition, or register shifting in a synchronous manner, each on a different data set. In order to be able to exchange data, the processors either communicate through an interconnection network or share a common memory.

Figure 1.2: MIMD computing system.

In an MIMD computing system, processors posses independent instruction cycles and operate asynchronously. Figure 1.2 shows the structure of an MIMD computing system with the input and output units omitted.

Special-purpose parallel architectures are designed with a particular problem in mind. They result in parallel computing systems well suited for solving that problem, but cannot in general be used for other purposes. Sorting networks fall into this class. They consist of a number of special processors arranged in a certain way and connected to each other through communication lines. Such a "constrained" type of sorting scheme is especially interesting because of its applications and its rich underlying theory. In addition to be used for parallel computing, sorting networks also

have important applications in communications. In particular, parallel processor architectures can be interconnected by pipelined sorting networks serving as message passing systems [5]. Similarly, telecommunication packet switches can be based on sorting networks [6].

#### 1.2.3 Interconnection Schemes

Considering an SIMD computing system, most of the processing procedures rely on the interconnection network to perform permutations of data among the processors. There are three most commonly studied interconnection architectures: Mesh, Perfect Shuffle, and Hypercube. We will compare the performance of all three architectures in the case of parallel computing and sorting of N data elements, where  $N = m \times m = 2^n$ . In this thesis, unless indicated otherwise, all logarithms are assumed to be base 2 and are denoted by  $log(\bullet)$ . Thus, we have

$$\log N = n. \tag{1.1}$$

Due to the regularity of data movements within most parallel computing algorithms, the most useful permutations have been studied and a family of permutations called Frequently Used Permutations (FUPs) have been identified [7]. A group of FUPs have been chosen as test permutations and a comparison is made on the number of cycles required for each interconnection architecture to perform the operations [8]. The results are shown in Table 1.1. The Perfect Shuffle and Hypercube all

perform the FUPs in  $O(\log N)$ , except that the Perfect Shuffle architecture needs only one cycle to perform the perfect shuffle permutation. The Mesh requires at least O(N) cycles to perform any of the FUPs.

| FUP                     | Mesh              | Perfect Shuffle | Hypercube |

|-------------------------|-------------------|-----------------|-----------|

| cyclic shift of d units | d                 | $2\log N - 1$   | $\log N$  |

| perfect shuffle         | <i>N</i> -1       | 1               | $\log N$  |

| bit reverse             | $2(\sqrt{N}-1)^2$ | $3\log N/2$     | log N     |

Table 1.1: Performance comparison of three types of interconnection architectures based on the number of cycles to accomplish a group of FUPs.

In the case of parallel sorting operations, processors need to perform the compare-exchange instruction and interconnection networks provide the routing instruction, respectively. The performance of Mesh, Perfect Shuffle, and Hypercube in an SIMD sorting machine has been studied [9, 10, 11] and we summarize it in Table 1.2. The Perfect Shuffle and Hypercube all perform the sorting operation in  $O(\log^2 N)$ . The Mesh requires  $O(\sqrt{N})$  cycles to perform the same sorting operation.

| Sorting                   | Mesh            | Perfect Shuffle | Hypercube     |

|---------------------------|-----------------|-----------------|---------------|

| route steps               | $O(\sqrt{N})$   | $O(\log^2 N)$   | $O(\log^2 N)$ |

| compare-exchange<br>steps | $O(\sqrt{N})$   | $O(\log^2 N)$   | $O(\log^2 N)$ |

| fan-out                   | 4               | 1               | $\log N$      |

| interconnection           | space-invariant | space-variant   | space-variant |

Table 1.2: Performance comparison of three types of interconnection architectures based on the number of cycles to accomplish a sorting operation.

Among all three types of interconnection architectures, the Perfect Shuffle has fast data permutation and routing abilities. Another advantage is that it has a single fan-out structure which avoids the problem of communication conflict between processing units caused by a multiple fanout structure. Thus, we favor the Perfect Shuffle in our system design.

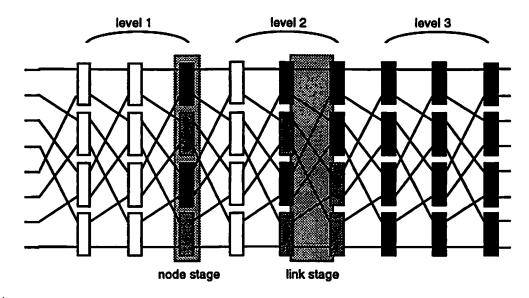

#### 1.2.4 Multistage Sorting Networks

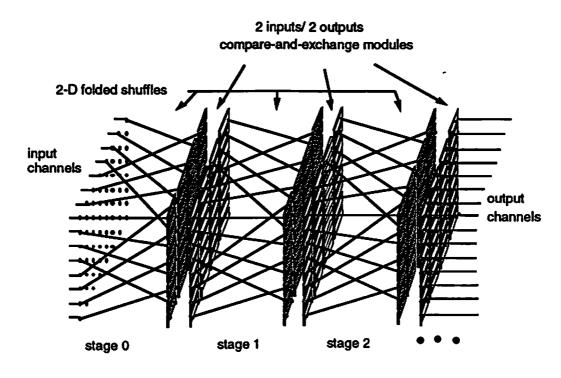

Sorting networks can be described by their construction and data format. A 2-D multistage sorting network, which can be implemented by electronic VLSI technology, has its signal channels and switching units arranged in 1-D arrays (node stages) and the link patterns arranged in planes (link stages) as shown in Fig. 1.3. A 3-D multistage sorting network, on the other hand, occupies a physical volume in space, and has its channels and switching units rearranged in 2-D arrays which are interconnected by link patterns in 3-D space as shown in Fig. 1.4. This structure intrinsically favors an optical implementation.

Figure 1.3: 2-D multistage sorting network.

Figure 1.4: 3-D multistage sorting network.

Multistage networks with different interconnection structures, such as the shuffle-exchange network, Banyan network, etc., can be used as a multistage sorting network. The perfect shuffle interconnection network is of most interest because of its relatively regular and simple structure.

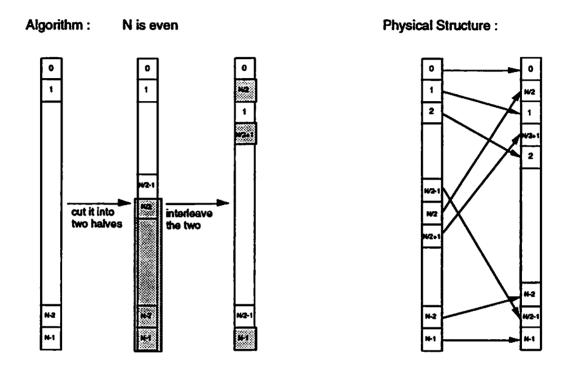

There are two kinds of perfect shuffles: 1-D and 2-D perfect shuffles. In the 1-D perfect shuffle, channels are arranged in a 1-D array and are shuffled in a plane. As shown in Fig. 1.5, The N channels (assuming N is even) are divided into two halves, then these two halves are interleaved.

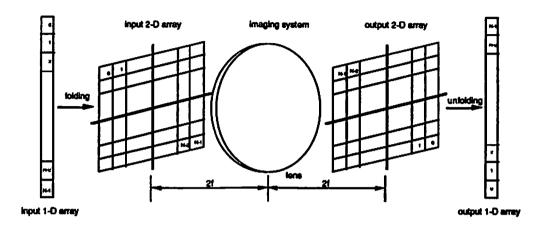

For the 2-D perfect shuffle, channels are arranged in a plane and are shuffled in free space. There are many variations of 2-D perfect shuffle, two of which are the 2-D separable shuffle and the 2-D folded shuffle. The algorithm for a 2-D separable shuffle is performed in two steps as shown in Fig. 1.6. The two steps are to perform 1-D perfect shuffles on the rows and

the columns independently. However, in the 2-D folded shuffle, rows and columns are related in the way that the 2-D plane is a rastered version of a long 1-D channel array as shown in Fig. 1.7. The purpose of 2-D folded shuffle is to perform the 1-D perfect shuffle more efficiently.

Figure 1.5: 1-D perfect shuffle.

1-O perfect shuffle on columns

$N = 2^n$  , n is even.

input 2-D array

Figure 1.6: 2-D separable shuffle.

output 2-D array

Figure 1.7: 2-D folded shuffle.

input 1-D array

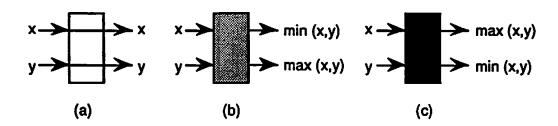

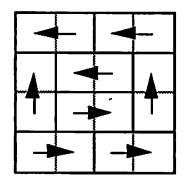

The special processors in the node stages of a multistage sorting network are dynamic switching units called compare-and-exchange (C&E) modules. There are three basic functions of a C&E module: bypass, maxsort, and minsort. These C&E modules and their input-output relations are shown in Fig. 1.8. The bypass function performs a simple

Figure 1.8: Three basic functions of a C&E module. (a) bypass function. (b) minsort function. (c) maxsort function.

output 1-D array

straight-through connection. The maxsort function sorts two inputs so that the input whose label is maximum emerges from the port labeled  $\max(x,y)$  (shown as the top port in Fig. 1.8(c)). The minsort function sorts two inputs so that the input whose label is minimum emerges from the port labeled  $\min(x,y)$  (shown as the top port in Fig. 1.8(b)).

#### 1.3 Objectives

With the increasing demand for solving computation-intensive problems, a volume, dynamic interconnection network that interconnects a 2-D array of channels or processing elements to another is desirable [12]. The objective of this research has been to investigate and study the practicality of a 3-D optoelectronic multistage sorting network utilizing diffractive optics and OEIC technologies. It explores and discusses 3-D structures for various types of planar sorting networks, the network implementation, and the design of optical interconnection elements and dynamic switching units. Both theoretical analysis and practical considerations are included in this work.

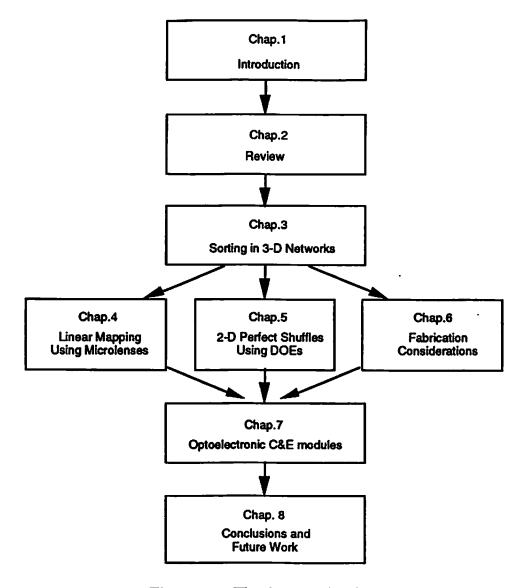

## 1.4 Thesis Organization

The body of the thesis has two main parts. The first part consists of Chapter 3, dealing with network architectures and implementations from a system point of view. The second part in Chapter 4, 5, 6, and 7 is devoted to technological issues, design and performance analysis. Figure 1.9 shows the organization of this thesis.

Figure 1.9: Thesis organization

Chapter 2 reviews the work of sorting algorithms on a variety of sorting networks. It also describes inherent problems of electronic and optical technologies for realizing a sorting network. The rest of Chapter 2 gives previous work done on optical interconnections and optoelectronic C&E modules.

Chapter 3 discusses three different types of multistage sorting networks and the relationship between their 2-D and 3-D structures. A merge procedure is presented for network expansion in 3-D space. The mathematical framework is established in this discussion. Toward the end of the chapter we give a comparison of these networks and summarize the results.

In Chapter 4 optical system designs for one-to-one linear mapping interconnection using microlenses are presented. The characteristics of Gaussian microbeams in on-axis diffractive microlens systems are first studied. Optical system structures for short and long distance interconnections are analyzed later on. In the rest of the chapter we focus on the packing limitations and light efficiency of each structure.

Chapter 5 studies the properties of a 2-D perfect shuffle and implements it using diffractive optical elements (DOEs). Phase-only blazed gratings and off-axis microlenses are used for space-variant designs, and a demagnifying algorithm is proposed for space-semivariant designs. The analysis of packing density and light efficiency is given at the end of each section.

In Chapter 6, we systematically analyze the fabrication problems of the multi-level DOEs discussed in Chapter 4 and 5. Mathematical proofs are given through the discussion.

Chapter 7 is devoted to the design of optoelectronic 2 input/2 output compare-and-exchange modules. The chapter starts with the logic design of C&E modules based on truth table minimization, finite state machines, and latching logic. The device technologies we choose to implement the logic circuits are logic self-electro-optic effect devices (L-SEEDs), field-effect transistor-self-electooptic effect devices (FET-SEEDs), and optoelectronic integrated circuits (OEICs) with built-in detectors and laser sources. Concepts and details are given through each design. The rest of the chapter deals with the packing density limitations considering three main factors: optical limitations due to diffraction, pixel size, and power dissipation. The performance analysis is summarized at the end of this chapter.

Chapter 8 gives a brief conclusion of this thesis. A few suggestions for the future research is given.

#### 1.5 Contributions

In this research, we systematically study, design, and analyze 3-D optoelectronic sorting networks. The contributions of this work are summarized as follows:

- The investigation of various types of structured sorting networks.

- The exploration of corresponding 3-D sorting network structures.

- The development of merging algorithms for the 3-D network expansion.

- The analysis of the reflected-symmetric property of 2-D folded shuffle.

- Novel designs of optical interconnection architectures for the 2-D folded shuffle based on diffractive optical elements.

- Generic designs of computer-generated diffractive gratings for the 2-D folded shuffle.

- The analysis of packing limits based on the characteristics of the light sources and diffractive optical elements.

- Systematic analysis of the efficiency loss of multi-level DOEs caused by lithographic fabrication problems.

- The design of 2 input/ 2 output optoelectronic compare-and-exchange modules based on different optoelectronic devices.

- The analysis of the performance of C&E modules based on the characteristics of the devices and the complexity of the circuitry designs.

# Chapter 2

## Previous Work - A Review

It is known that serial sorting algorithms require at least  $O(N \log N)$  temporal complexity to sort N inputs [2]. Due to the need for rapidly sorting large quantities of information, parallel sorting algorithms which can offer enhanced performance have been studied since at least the 1960's. In 1968, Batcher [13] discovered the bitonic sorting network which has sublinear  $(O(\log^2 N))$  temporal complexity to sort N inputs. The bitonic sorting network can be pipelined in a multistage architecture that requires global interconnection patterns and dynamic switching units. Both electronic technology and optical devices have been considered for realizing these kinds of sorting networks. This includes:

- Electronics: very large scale integrated circuits (VLSI)

- · Optics: lenses, prisms, holograms, etc.

As pointed out by Goodman et. al. [14], VLSI networks suffer from crosstalk, clock-skew, pin-in/pin-out limitations, and delay problems when the interconnections are spatially dense or long distance. Other problems, including high frequency parasitic coupling between circuit elements,

excessive power dissipation, and impedance mismatch, limit the performance of electronically implemented networks. These limitations restrict the utilization of electronics in volume sorting networks. On the other hand, optics has useful properties such as high bandwidth, low crosstalk and inherent parallelism. Thus, optics is ideally suited for providing the interconnections needed in a volume sorting network.

Unfortunately, due to physical and technical constraints, a high speed, power efficient and easily controllable purely optical C&E module has been very difficult to build. A new group of devices called optoelectronic devices have been developed by researchers in order to utilize the capabilities of both optics and electronics for the dynamic switch elements. These devices include spatial light modulators (SLM), liquid crystal light valves (LCLV), self electro-optic effect devices (SEEDs) based integrated circuits, vertical-cavity surface-emitting lasers (VCSELs) based integrated circuits, and optoelectronic integrated circuits (OEIC) [56, 85]. In the remainder of this section, we will review previous work on optical interconnections and optoelectronic C&E modules.

## 2.1 Optical Interconnections

It has been recognized that optical interconnections can provide the global connections needed between the stages of a interconnection network [14, 15]. For example, each bitonic interstage connection pattern can be emulated by a number of stages of optical perfect shuffle interconnections with global, space-variant communications [10]. Optical elements such as

simple lenses, mirrors, and prisms have be used to implement free-space perfect shuffles [16, 17, 18]. However, as the array size and density of new optoelectronic devices in the interconnection networks have increased, and more complex and irregular non-local interconnections are required, it has become more obvious that conventional deflective and reflective optical elements are unable to meet the requirements. New optical elements, such as holograms and micro-optical components, offering unique wavefront transformation capabilities have been proposed to solve these problems.

Diffractive optical elements (DOEs) are phase-only micro-optical components. Some early DOEs were made by Dammann [19] who used computer-designed surface-relief structures and integrated-circuit etching methods to transfer a binary surface-relief pattern to a dielectric or metallic substrate. These versatile devices can be much thinner and lighter than conventional ones because they need to induce changes of only a fraction of a wavelength in the shape of an optical wavefront. Another advantage of DOEs over conventional bulk optics from a manufacturing point of view is the possibility of monolithic integration of different elements such as micro-lenses and gratings as well as aberration correction optics [20].

The growth of integrated-circuit manufacturing technology and the developments in numerical design techniques starting from the 1970s and 1980s has made diffractive optics a real alternative to their conventional counterparts. Design concepts for computer-generated holograms (CGH) for

diffractive elements have existed for decades [21]. The problem with holograms is that, as more and more optical systems operate at low fiber loss, near-infrared wavelengths, volume holographic recording materials become less sensitive and need special exposure procedures. On the other hand, DOEs are fabricated using simpler repeated masking and etching, which makes it possible to fabricate complex binary optical interconnection patterns cheaply and in volume. Thus, diffractive optics has shown its superiority in this area.

Diffractive optics have so far been applied to various research areas, for example, multiple imaging of single objects [19, 22], optical communications [23, 24], laser beam profile shaping [25, 26] and beam combining [27]. The interest in the all-optical digital computers and photonic switching circuit has also led to a very intensive research effort on the design and fabrication of both binary and multi-level DOEs for 2-D beam array generation [28, 29, 30, 31, 32, 33, 34, 35, 36, 37, 38, 39, 40]. Those DOEs perform functions such as power and the clock signal illumination, fan-in, fan-out, and optical interconnection between logic element arrays. In this work, we focus on the implementations of free-space interconnection using diffractive optics.

Extensive research has been done in designing diffractive optical elements for free-space interconnections. From the system design point of view, the proposed implementations for optical interconnections can be classified into following two categories:

Fourier-Plane DOEs: These elements, first pioneered by Dammann [19], are periodic Fourier-type surface-relief structures which generate a given far-field pattern insensitive to the shape of incident light beam. The design of the binary phase pattern of a Fourier-plane DOEs is a complicated numerical problem. Two main design methods that utilize the freedom to optimize the phase of grating functions were proposed in 1970s: the nonlinear parametric optimization technique; and the iterative Fourier transform algorithm. The latter, which based on the Gerchberg-Saxton phase retrieval algorithm [41], is presently the most computer-time efficient technique. Parameter optimization method. first applied to the design of DOEs by Dammann [19] and later also known as the simulated annealing algorithm [42], can always find a global optimum of the phase grating. It is the most efficient of the general-purpose nonlinear design methods. Fourier-plane DOEs have been mostly used as beam splitters for providing equal-intensity, equalspacing spot arrays. They are also capable of generating light spot arrays with irregular patterns and density [43,44]. These elements can serve as space-invariant interconnections which have one-to-many or many-to-many communicating capabilities.

The concept for parallel optoelectronic bus-type and star coupler interconnections (many-to-many) utilizing one single space-invariant diffractive optical system was proposed by Killat [23] and Krackhardt [24], respectively. In their work, a Dammann grating was used as a multiple beam splitter providing simultaneous fan-in and fan-out

capabilities. Morrison [45] demonstrated a novel use of a space-invariant DOE design to create a space-variant Banyan interconnection.

The major drawback of Fourier-plane DOEs is their complicated design process needed because of the position of the transitions and the phase depth must be optimized for the desired beam configuration [46].

Fresnel-Plane DOEs: These elements are essentially multifacet devices, in which each facet deflects and focuses a single incident beam in a prespecified manner. Theoretically, any one-to-one space-variant interconnection can be performed using multifacet Fresnel-plane DOEs. For example, microlens arrays fabricated by diffractive optics technology were applied to 2-D free-space optical interconnections by McCormick [47]. DOEs for optical perfect shuffle interconnection have been proposed by Song [48]. It was designed by calculation of the interference fringes between diverging waves from four point sources and a reference plane wave. A different approach has been taken by Zhan [49], in which a quadrant-encoded grating and spatial filters were used to perform 2-D optical perfect shuffles.

As pointed out above, Fresnel-plane DOEs are essentially diffraction gratings with a different fringe period and orientation in each facet. In the realization of these multifacet elements, it is usually necessary to fabricate multi-level surface-relief profiles to achieve sufficient light efficiency. Currently, mask alignment error is the bottleneck in

fabrication of such structure. More detailed discussion will be given in later chapters.

# 2.2 Optoelectronic Compare-and-Exchange Modules

A compare-and-exchange module performs the job of rearranging inputs according to their values. Two major operations, comparison and exchange, need to be done in a single module. These two operations can be implemented with a variety of optical technologies [50]. The optimal technology depends on the requirements of the application of interest.