# **USC-SIPI REPORT #271**

An Efficient Digital VLSI Neural Processing Element Design for Image Processing

by

Josephine Chia-Fen Chang

October 1994

Signal and Image Processing Institute UNIVERSITY OF SOUTHERN CALIFORNIA

Department of Electrical Engineering-Systems 3740 McClintock Avenue, Room 404 Los Angeles, CA 90089-2564 U.S.A.

To My Parents,

$\begin{array}{c} \textit{Mau-Hsiung Chang} \\ \quad \text{and} \\ \\ \textit{Fu-Hwa Lin}, \end{array}$

for their love and encouragement.

# Acknowledgements

I would like to express my deepest thanks to my research advisor Professor Bing J. Sheu for his guidance and support throughout the course of my Ph.D. research work. I wish to extend my sincere appreciation to Professor Murray Gershenzon, Chairman of Materials Science and Engineering Department, and Professor C.-C. Jay Kuo for serving as my dissertation committee members. I would also like to thank them along with Professor Irving Reed, Professor Richard Leahy and Professor Richard Nottenburg for serving on my qualifying examination committee.

I am very grateful to Professor Leonard Silverman, Dean of the Engineering School; Professor Hans H. Kuehl, Chairman of the Electrical Engineering - Electrophysics Department; Professor Melvin A. Breuer, Chairman of the Electrical Engineering - Systems Department; Professor Kai Hwang, Professor Alice C. Parker, Professor Sidney A. Wielin, Professor Alvin Despain, Ms. Ramona Gordon, Ms. Anna Fong, Ms. Gloria Halfacre and Ms. Susan Moore in the Electrical Engineering Program, for providing me the great research environment for my Ph.D. study at the University of Southern California (USC). This research work was conducted through connections with several research organizations at USC including Center for Neural Engineering (CNE), Signal and Image Processing Institute (SIPI), Center for Photonic Technology (CPT), and MOSIS Service of Information Science Institute (ISI). Very valuable suggesting opinions from Professor Jerry M. Mendel, Professor Michael A. Arbib, Professor Bart Kosko and Professor Ted Berger were highly appreciated.

Discussions with graduated doctoral colleagues from VLSI Signal Processing Laboratory were truly valuable, including Dr. Bang W. Lee and Dr. Joongho Choi on VLSI neural chips design, and Dr. Ji-Chien Lee on digital data bus design, Dr. Wen-Jay Hsu and Dr. Sudhir Gowda on circuit simulation, and Dr. Wai-Chi Fang on image processing. Many thanks to Sa H. Bang and Oscal T.-C. Chen for helping to obtain some simulation results. I also thank Robert C.-H. Chang, Tony H.-Y. Wu, and Vincent W.-J. Wang for managing the computing facility. Interactions with Hiroto Okada and Barton Sano were also very useful.

Family support helped me to finish this dissertation smoothly. I would like to thank my parents, Mau-Hsiung Chang and Fu-Hwa Lin for their love and understanding, my brother Hung-Ming Chang for his encouragement. I am thankful to my cousins Professor Hung-Chun Chang of National Taiwan University for his inspiration of my study in USC; Chia-Lin Chang, Shih-Wen Chao in Los Angeles, and Boa-Chen Yu, Hung-Wen Chang in Berkeley for their continuous kind help since I came to U.S.A.

# Contents

| Li  | st Of | f Tables                   | vii                              |

|-----|-------|----------------------------|----------------------------------|

| Lis | st Of | f Figures .                | viii                             |

| Al  | ostra | ct                         | хi                               |

| 1   | Intr  | roduction                  | 1                                |

|     | 1.1   | Intelligent Machines       | 2                                |

|     | 1.2   | 1.2.1.4 Packaging          | 3<br>5<br>8<br>10<br>12          |

|     | 1.4   |                            | 14<br>15                         |

| 2   | Neu   | ral Network Models         | 16                               |

|     | 2.1   | Biological Neural Networks | 17                               |

|     | 2.2   | 2.2.1 Data Representation  | 18<br>22<br>23<br>24<br>24<br>25 |

|   |     | 2.2.2.2       Multi-Layer Perceptron Networks         2.2.2.3       Kohonen Self-Organizing Feature Map         2.2.2.4       Comparison                                                                                                                       | 28                                                       |

|---|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 3 | Mu  | lti-Level Neural Networks with Optimal Solutions                                                                                                                                                                                                               | 31                                                       |

|   | 3.1 | Simulated Annealing                                                                                                                                                                                                                                            | 32                                                       |

|   | 3.2 | Paralleled Hardware Annealing                                                                                                                                                                                                                                  | 33                                                       |

|   | 3.3 | Analysis Results                                                                                                                                                                                                                                               | 39                                                       |

| 4 | Dig | ital Neural Processing Element                                                                                                                                                                                                                                 | 45                                                       |

|   | 4.1 | Hardware-Software Codesign Methodology                                                                                                                                                                                                                         | 45                                                       |

|   | 4.2 | System Architecture                                                                                                                                                                                                                                            | 47                                                       |

|   | 4.3 | 4.3.1 Back-propagation Learning                                                                                                                                                                                                                                | 50<br>50<br>53                                           |

|   | 4.4 | 4.4.1 Chip Architecture 4.4.2 VLSI Design Considerations 4.4.2.1 Design Process 4.4.2.2 Physical Design Style 4.4.2.3 Logic Style 4.4.2.4 Complementary Pass-Transistor Logic 4.4.3 A Design Example 4.4.3.1 Clock Distribution Scheme 4.4.3.2 Computing Units | 54<br>56<br>59<br>62<br>63<br>63<br>65<br>65<br>66<br>72 |

|   |     | 4.4.3.4 Register File                                                                                                                                                                                                                                          | 73<br>74<br>74<br>76                                     |

| 5 |     |                                                                                                                                                                                                                                                                | 81                                                       |

|   | 5.1 |                                                                                                                                                                                                                                                                | 82                                                       |

|   | 5.2 | Image Compression                                                                                                                                                                                                                                              | 26                                                       |

| 6 Impact of Dissertation Work and Future Directions   | 91 |

|-------------------------------------------------------|----|

| Reference List                                        | 93 |

| Appendix A: Publications Out of the Dissertation Work | 99 |

# List Of Tables

| 2.1 | Comparison between a human brain and artificial neural networks                                                          | 21 |

|-----|--------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Comparison of various neural network models                                                                              | 30 |

| 3.1 | Eigenvalues of a 6-bit A/D decision network                                                                              | 38 |

| 3.2 | Eigenvalues of an 8-bit A/D decision network                                                                             | 38 |

| 3.3 | Critical amplifier gains of a 6-bit A/D decision network                                                                 | 40 |

| 3.4 | Critical amplifier gains of an 8-bit A/D decision network                                                                | 40 |

| 4.1 | Comparison of digital electronic design approaches                                                                       | 55 |

| 4.2 | Performance of selective neural network hardware examples                                                                | 57 |

| 4.3 | Comparison of different design styles                                                                                    | 62 |

| 4.4 | Characteristics of a PE                                                                                                  | 78 |

| 5.1 | A compact instruction set for artificial neural networks                                                                 | 83 |

| 5.2 | Descriptions of the 43 Mcodes                                                                                            | 84 |

| 5.3 | Profile of the instruction set for a 3-layer neural network using back-propagation learning rule after 1,000 iterations. |    |

| 5.4 | Profile of the instruction set for a self-organizing network after 4,096 iterations.                                     | 89 |

# List Of Figures

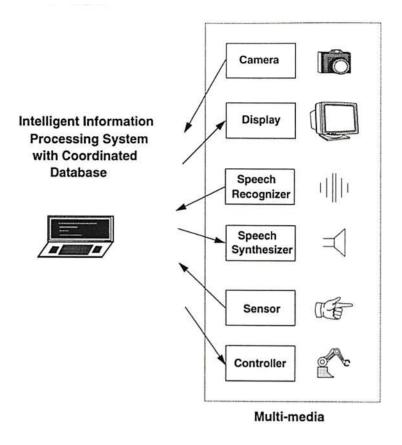

| 1.1  | An integrated intelligent information processing system with multi-media capability. | 3  |

|------|--------------------------------------------------------------------------------------|----|

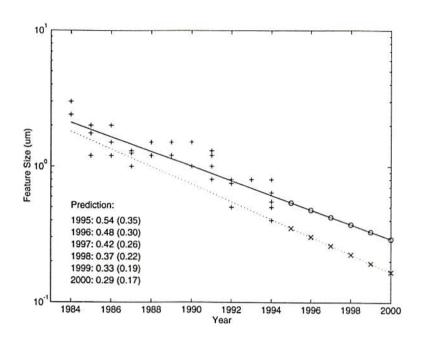

| 1.2  | Trend of transistor feature size in a microprocessor                                 | 6  |

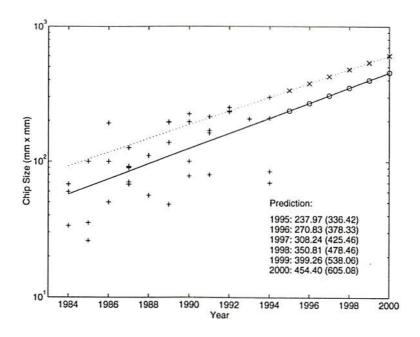

| 1.3  | Trend of microprocessor chip size                                                    | 7  |

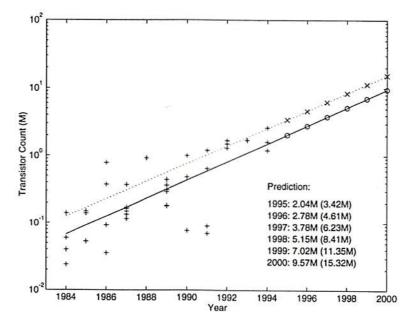

| 1.4  | Trend of number of transistors in a microprocessor                                   | 7  |

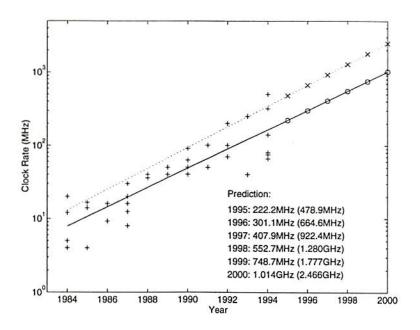

| 1.5  | Trend of clock rates of microprocessors.                                             | 8  |

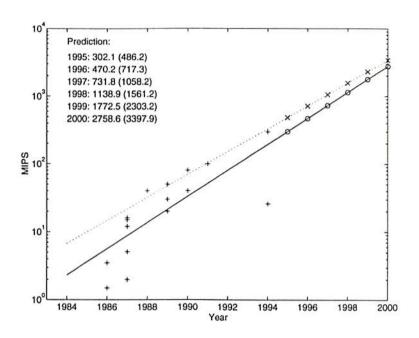

| 1.6  | Trend of performance of microprocessors.                                             | 9  |

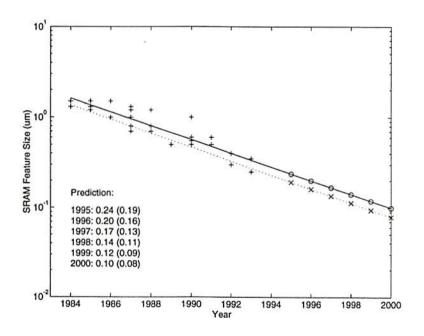

| 1.7  | Trend of transistor feature sizes of SRAM                                            | 9  |

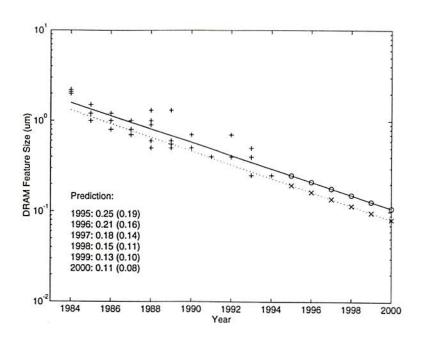

| 1.8  | Trend of transistor feature sizes of DRAM                                            | 10 |

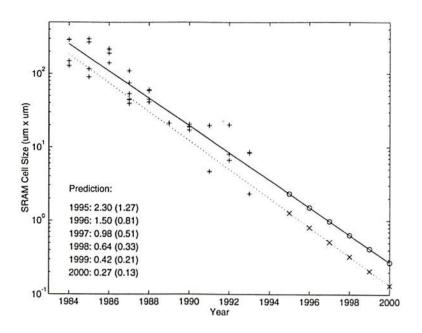

| 1.9  | Trend of SRAM cell size                                                              | 11 |

| 1.10 | Trend of DRAM cell size.                                                             | 11 |

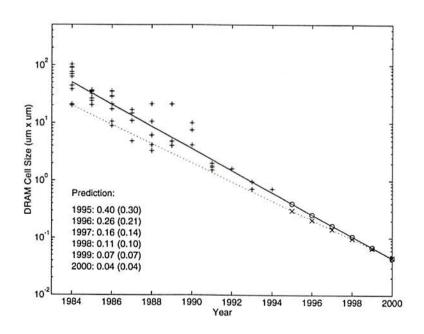

| 1.11 | Trend of power consumption of microprocessor and digital signal processors.          | 12 |

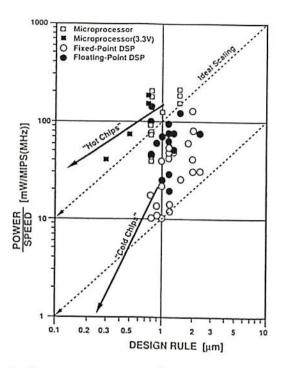

| 1.12 | Trend of pin-count of a chip.                                                        | 13 |

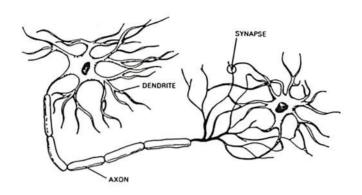

| 2.1  | Biological Neuron.                                                                   | 18 |

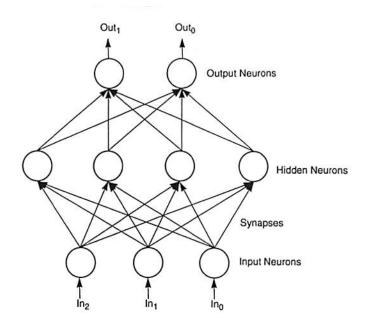

| 2.2  | Architecture of a typical three-layer fully-connected neural network                 | 23 |

| 2.3  | Architecture of a Hopfield network with two-level neurons                            | 25 |

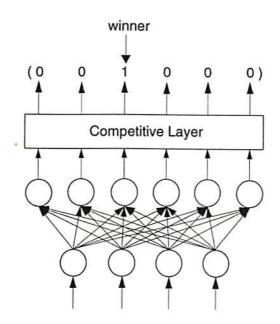

| 2.4  | A basic structure of the self-organizing feature map                                 | 29 |

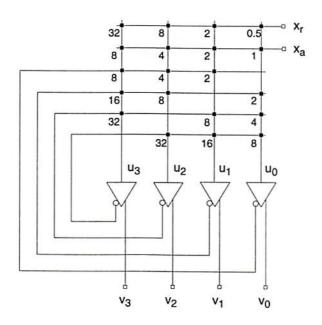

| 3.1  | A Hopfield 6-bit neural A/D decision network with 4-level neurons                    | 34 |

| 3.2  | Transfer function of a 6-bit A/D decision network with. 4-level neurons              | 36 |

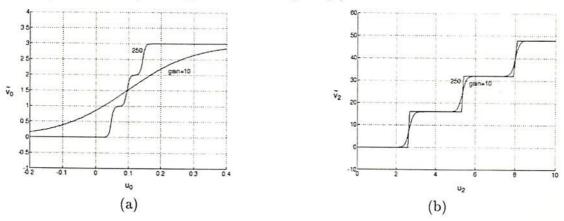

| 3.3  | Plots of the 4-level neuron functions with different controlling gains used in a 3-neuron A/D decision network. (a) Least-significant neuron. (b) Most-significant neuron.                           | 37 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

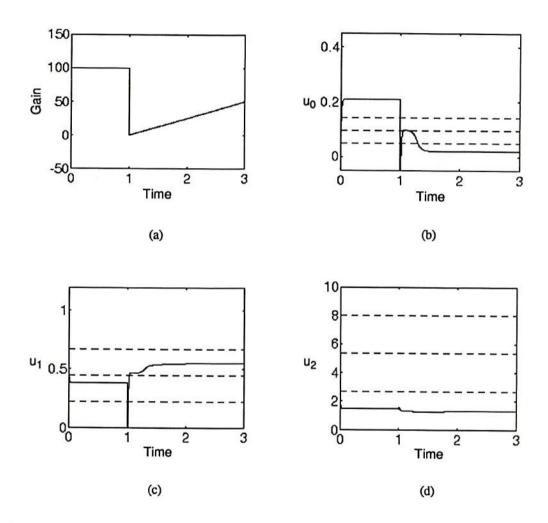

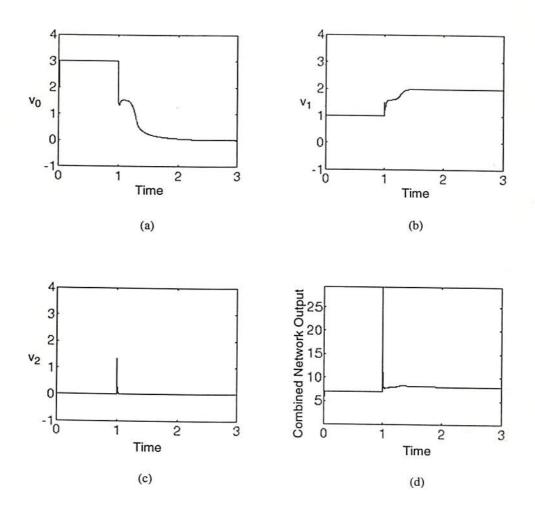

| 3.4  | Time domain responses of the voltages at the neuron input nodes in the A/D decision network when the analog input value $x_a$ is 7.9. (a) Neuron gain. (b) Neuron 0. (c) Neuron 1. (d) Neuron 2      | 41 |

| 3.5  | Time domain responses of the output values of neurons when the analog input value $x_a$ is 7.9. (a) Neuron 0. (b) Neuron 1. (c) Neuron 2. (d) Combined output                                        | 42 |

| 3.6  | The output state trajectory of the A/D decision network                                                                                                                                              | 43 |

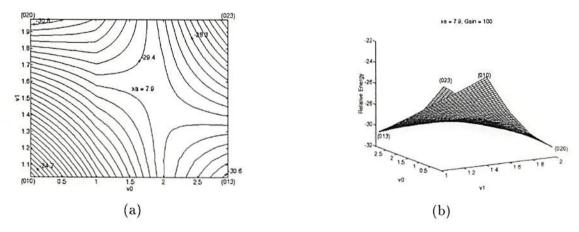

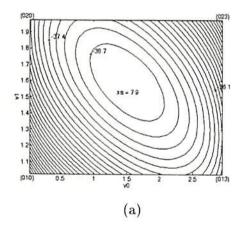

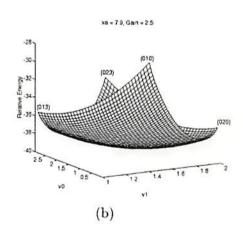

| 3.7  | (a) The energy contour. (b) The energy surface. The voltage at the input node of neuron $u_2$ is kept as 0. $x_a$ is 7.9 and amplifier gain is 100                                                   | 43 |

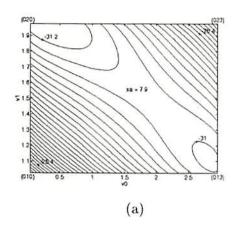

| 3.8  | (a) The energy contour. (b) The energy surface. The voltage at the input node of neuron $u_2$ is kept as 0. $x_a$ is 7.9 and amplifier gain is 10                                                    | 44 |

| 3.9  | (a) The energy contour. (b) The energy surface. The voltage at the input node of neuron $u_2$ is kept as 0. $x_a$ is 7.9 and amplifier gain is 2.5                                                   | 44 |

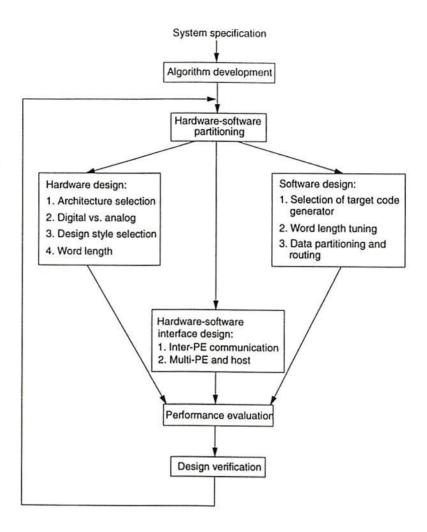

| 4.1  | A general codesign strategy                                                                                                                                                                          | 46 |

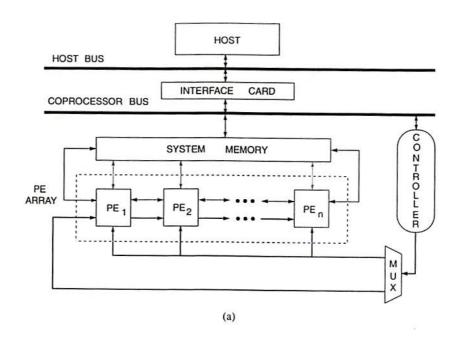

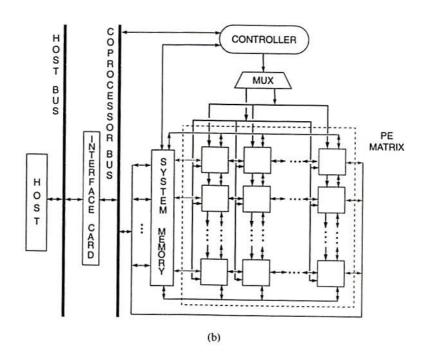

| 4.2  | System architecture for systolic networks. (a) 1-D ring-connected array. (b) 2-D mesh-connected matrix                                                                                               | 49 |

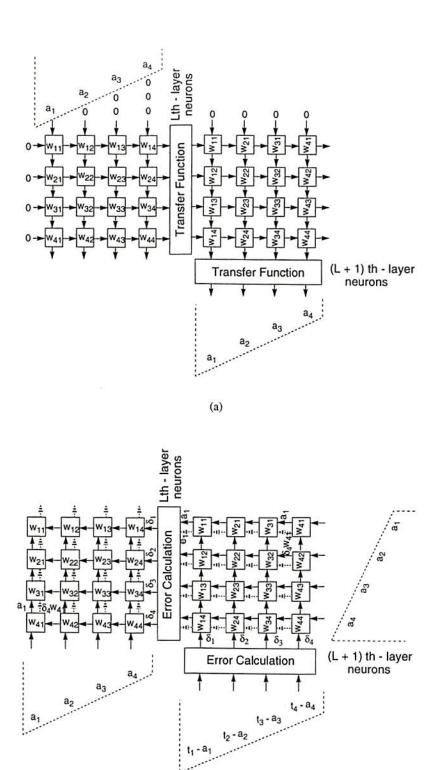

| 4.3  | Mapping diagram of a back-propagation neural network onto a mesh-connected PE matrix. (a) Feedforward propagation phase. (b) Backward error propagation phase                                        | 52 |

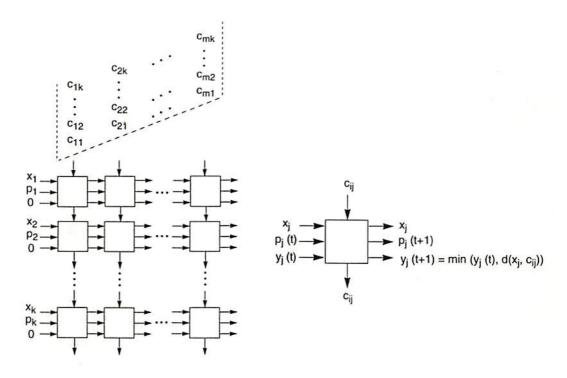

| 4.4  | Mapping diagram of a self-organizing neural network onto a mesh-connected PE matrix                                                                                                                  | 54 |

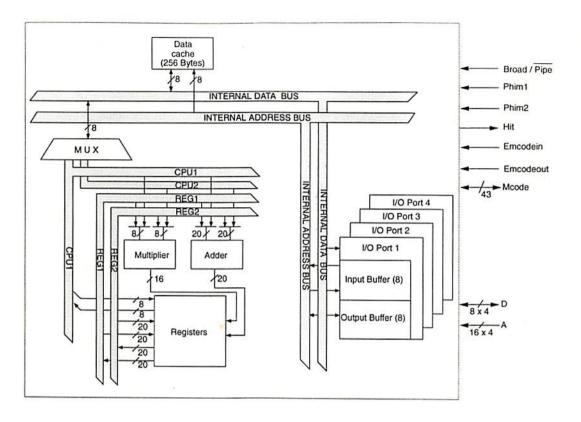

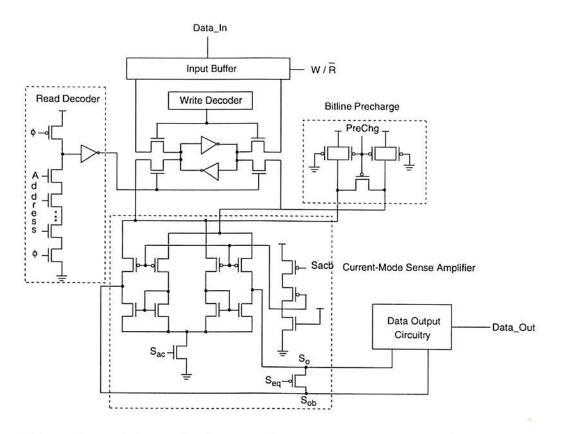

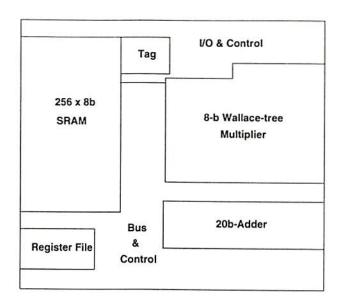

| 4.5  | Building blocks and bus distribution of a processing element                                                                                                                                         | 58 |

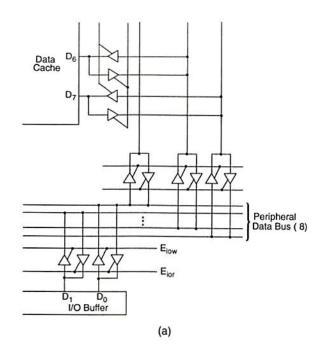

| 4.6  | The external control circuitry for interfacing with the data cache (a) Between the cache memory and the I/O buffer. (b) Between the cache memory and the four bus segments REG1, REG2, CPU1 and CPU2 | 60 |

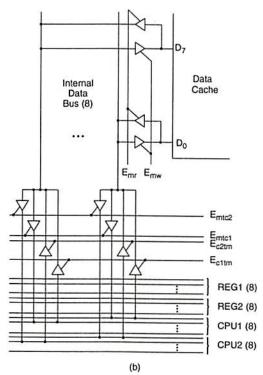

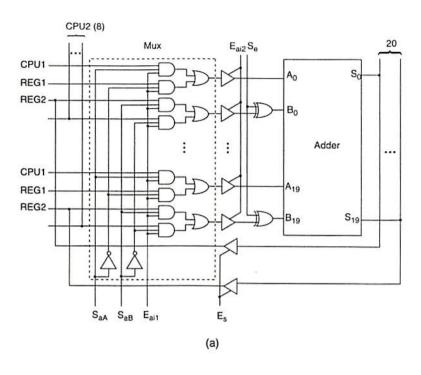

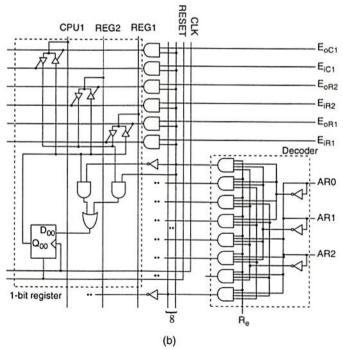

| 4.7  | Required control circuitry (a) For adder. (b) For register file                                                                                                                                      | 61 |

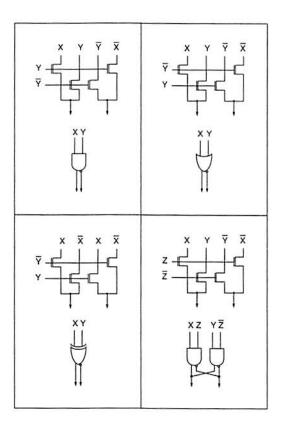

| 4.8  | CPL circuit modules                                                                                                                                                                                  | 64 |

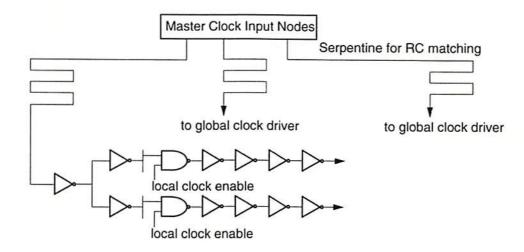

| 4.9  | Clock distribution scheme with selectively power down capability                                                                                                                                     | 66 |

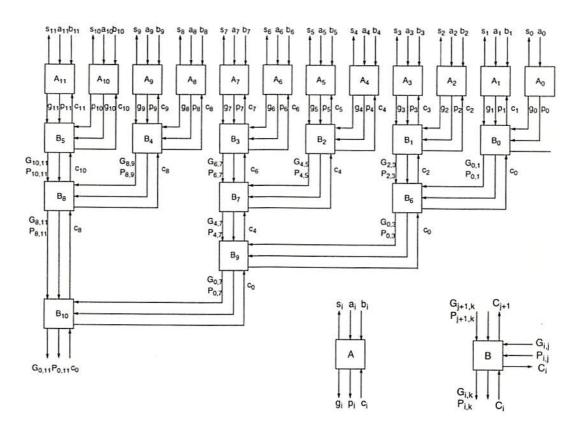

| 4.10 | Block diagram of a 12-bit CLA adder                                                                                                                                                                  | 68 |

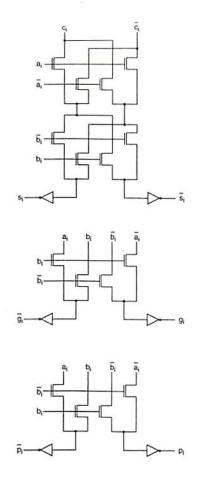

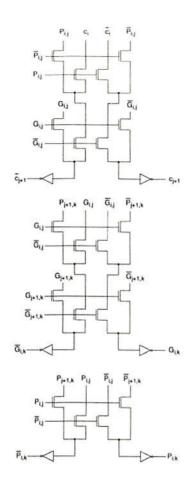

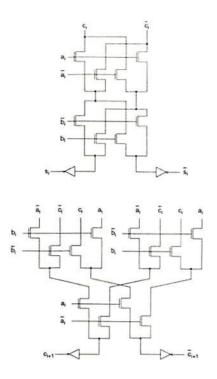

| 4.11 | Circuits in block A                                                                                                                | 69 |

|------|------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.12 | Circuits in block B                                                                                                                | 70 |

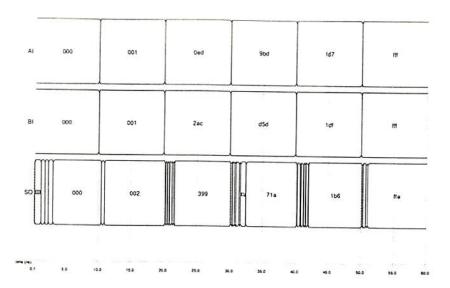

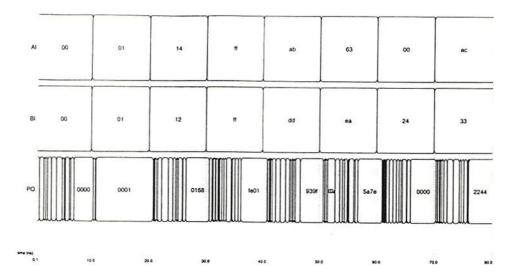

| 4.13 | Result of 12-bit adder after running irsim simulation                                                                              | 71 |

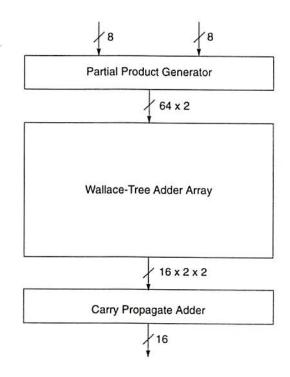

| 4.14 | Functional block diagram of an 8-bit Wallace multiplier                                                                            | 71 |

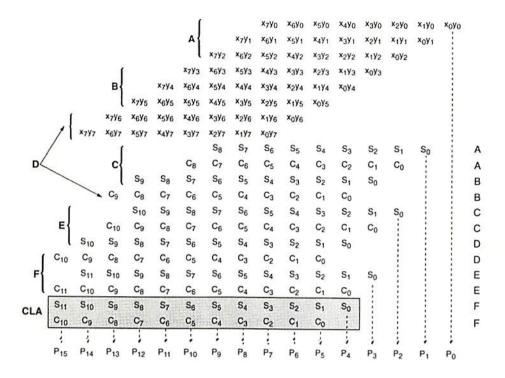

| 4.15 | 8-bit Wallace multiplication                                                                                                       | 72 |

| 4.16 | Circuit diagram of a 1-bit CSA unit                                                                                                | 73 |

| 4.17 | Result of 8-bit multiplier after running irsim simulation                                                                          | 74 |

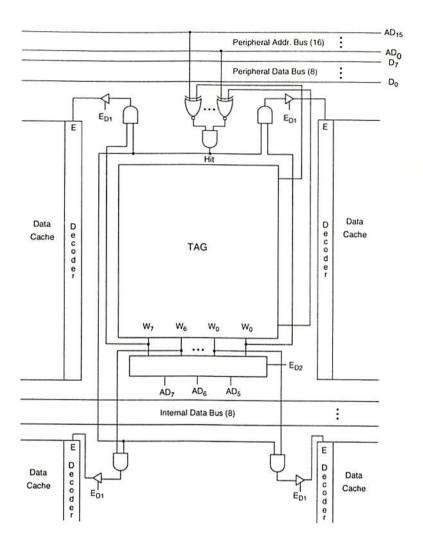

| 4.18 | The control circuitry in the cache memory block                                                                                    | 75 |

| 4.19 | Schematic diagram of selective circuits in the data cache                                                                          | 76 |

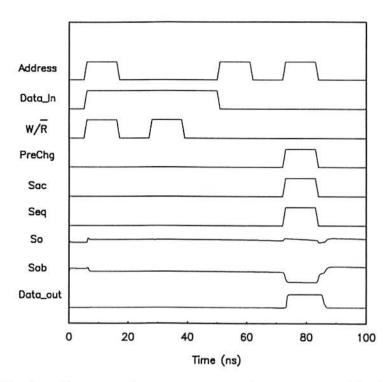

| 4.20 | Timing diagram of memory access in a memory block of 32 word $\times$ 2 bit                                                        | 77 |

| 4.21 | Floorplan of a PE                                                                                                                  | 78 |

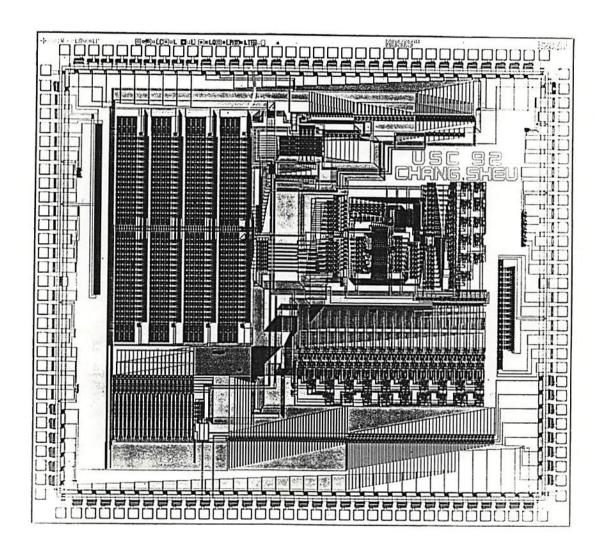

| 4.22 | Die photo of the single PE chip fabricated by a 0.8- $\mu\mathrm{m}$ CMOS technology                                               | 79 |

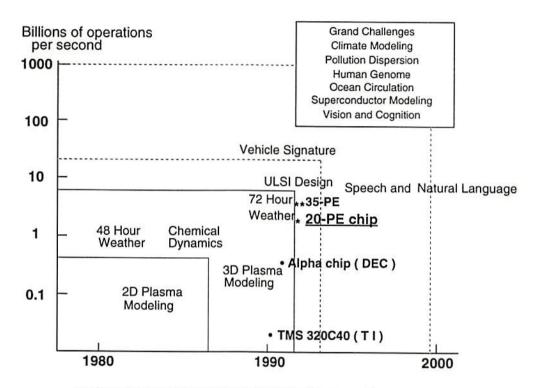

| 4.23 | Performance requirements of several Grand Challenge problems and the relative performance of the proposed multi-PE chips           | 80 |

| 5.1  | Architecture of an integrated intelligent processing system                                                                        | 81 |

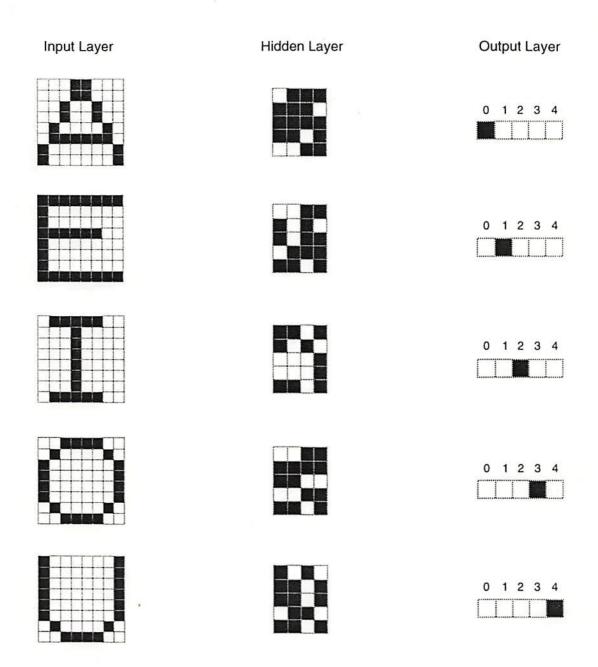

| 5.2  | Application of the back-propagation network to printed character recognition. 1,000 iterations were performed during training.     | 87 |

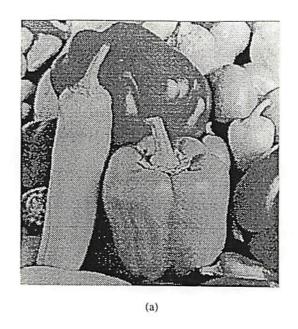

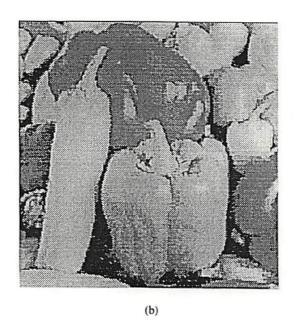

| 5.3  | Image compression on the multi-PE chip using a self-organizing neural network. (a) The original image. (b) The reconstructed image | 90 |

### Abstract

With increasing computing power of a chip implemented by silicon technology, an intelligent machine which possesses basic skills of sensing, signal processing, and moving based on human brain models becomes feasible in the near future. In addition, artificial neural networks have the potential to solve many complex and time-consuming engineering and scientific problems with inherently massively parallel processing architectures. To obtain an optimized solution from a neural network, the paralleled hardware annealing method can be applied. The results on neural networks with multi-level nonlinearities are presented. Hardware using parallel architecture could greatly speedup neural network operations. By using the digital processor design approach, high-precision requirements for neural network algorithms can be easily achieved. A custom-designed digital VLSI processing element (PE) for general-purpose neurocomputing is presented. Detailed communication networks, instruction sets and circuit blocks are created for the one-dimensional ring-connected and two-dimensional mesh-connected systolic array. The reduced instruction set technique and microprogramming skills can be applied to optimize the software control of the processor array. A prototype PE has been designed and fabricated in a  $6.19 \times 5.46 \ mm^2$  microchip by using the 0.8- $\mu m$  CMOS technology from Hewlett-Packard Company through the MOSIS Service. By arranging the PE layout in a ring-connected array architecture, a 20-PE chip is estimated to occupy a silicon area of  $2.09 \times 1.93 \ cm^2$ by using a 0.5- $\mu m$  CMOS technology. A digital signal processor chip can be used to broadcast or pipeline microcodes to all processing elements in an array. This neural PE design is suitable for image processing. System-level simulation results of applications including printed character recognition and image compression based on neural network algorithms using the designed hardware are also presented.

# Chapter 1

### Introduction

Since the outburst of first-generation computers, machine computation capabilities based on Von Neumann sequential processing codes have progressed tremendously because of advances of very large scale integration (VLSI) technologies. Continuous reduction of feature sizes and acceleration of operating speeds pack more and more complicated and sophisticated functional units into a smaller silicon real-estate. Multiple copies of hardware targeting for the same function become possible to be grouped together in a system. The domain of a group can be multiple boards, multiple chips on a single board or a single substrate, or multiple functional units on a single chip.

The trend of moving from serial processing to parallel processing follows a natural rule. Brain cells of animals manipulate things by working cooperatively. One example is animal can run and catch, see and hear at the same time. Although how a brain really functions still remains a puzzle to the mankind, the knowledge that we have accumulated through the research on a brain do give good stimuli to the construction of a new-generation parallel processing computer.

The arithmetic calculating power of a computer so far has far prevailed over human's capability. But for complicated signal processing problems where large quantity of equations with massive amount of data need to be solved in real time, computing speed still need to be improved considerably. In addition, the capability of associating one thing to the other by a computer so far pale in comparison with that of a human today. To perform

associativity is essential for conducting intellectual activities. The parallel processing capabilities of artificial neural networks not only accelerate operating speed, but also have a great potential for associativity. Therefore, importance of research on how to take advantage of properties of artificial neural networks for developing an intelligent machine which has both large computing speed and profound associativity cannot be overemphasized.

# 1.1 Intelligent Machines

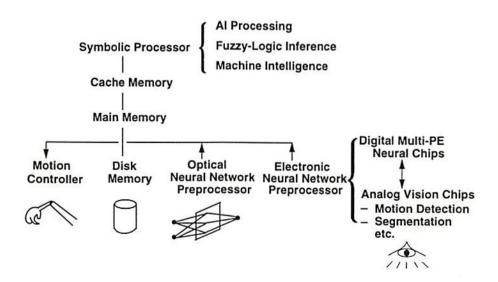

This dissertation is concerned with the design of components in an intelligent machine. The machine is an integrated information processing system which can communicate with the real world through audio and video channels, together with a large database. A configuration of such an intelligent information processing system is shown in Fig. 1.1. High-speed image processing, vision understanding, and smart graphics provide the systems with visual capabilities. Speech recognition and synthesis techniques provide the systems with audio processing capabilities. The system is also equipped with microsensor and controller units to accomplish physical actions. Such a powerful multi-media data-fusion machine can be used in many places, and will help people in their business, education, and daily lives.

An intelligent machine can be equipped with sensors, processors, and actuators [1]. Sensors interact with the environment to capture information relevant to task objectives; processors perform information processing; actuators execute the resultant outputs from processors. Intelligent machines must be able to operate successfully in unanticipated situations. Some decisions might have to be made with incomplete or uncertain information and competing constraints to solve problems and reach correct conclusions.

Predictably, in the coming years during the 90's, a multi-hundred-billion-dollar computer and information-processing industry is emerging, together with a generation of ubiquitous machine intelligence that works intimately with its human creators. For example, reliable person identification, using pattern-recognition techniques applied to visual and speech patterns, could replace locks and keys in many instances [2].

Figure 1.1: An integrated intelligent information processing system with multimedia capability.

### 1.2 Promises of VLSI

With the rapid progress of VLSI technologies during the past five years, to construct an intelligent information processing system which integrates several subsystems for processing different functions becomes highly possible. Currently, multi-million transistors can be integrated on a single chip; computer processors can operate at speed in the range of hundred million instructions per second (MIPS). In 1994, the feature size of 0.25  $\mu m$  has become widely used [3]. Engineers and scientists has already been looking into the next step of linewidth being 0.18  $\mu m$  and below that will be needed to build 1G-bit dynamic random access memories (DRAMs).

The range of power supply has decreased from more than 5 volts to less than 2 volts [4]. The original impetus to lower operating voltages was the need to improve the reliability of fine-geometry devices such as DRAMs. Consumers have two basic complaints about the portable machines: they are too heavy, and battery life often falls far short of the all-day operation that would make them practical. Running systems at a lower power supply can reduce power consumption, extend battery life, and even allow the designer to jettison some of the heavy battery cells. Devices available in low-voltage versions include DRAM, flash memory, gate arrays, microprocessors, and digital signal processors. In addition, lower voltages reduce noise and electromagnetic interference (EMI), factors becoming increasingly important as the computer devices move off the desktop into harsher environments. The low-voltage versions typically run slower, however, because the drain-source current is reduced as the square of the gate-source voltage. Internal capacitors require longer time to charge at the lower current, which then must run at a reduced frequency.

The submicron CMOS technology for arithmetic-oriented superchip implementation and monolithic wafer-scale integration also achieves a functional throughput rate of 10<sup>13</sup> gate-Hz/cm<sup>2</sup> [5]. The use of VLSI circuits can greatly reduce the physical size and enhance the performance and reliability of microelectronic systems. In the microprocessor domain, continuous progresses on reduced instruction set computers (RISC) enables the introduction of the powerful Intel-i860 chip [6], the SPARC chip from Sun Microsystems Inc.[7], the 400-MIPS Alpha chip from Digital Equipment Corporation (DEC) [8], and the PowerPC 601 from IBM, Motorola, and Apple Computer over the past few years. In 1994, a 500-MHz 32-bit processor was announced by NEC Corporation [9]. The 3.1-million transistor Pentium chip from Intel Corporation [10] represents another design category called complex instruction set computers (CISC). Several powerful microprocessors have been announced out of various technologies such as a 300-MHz bipolar ECL microprocessor from DEC [11] and a 3.3-V 0.6-μm BiCMOS superscaler microprocessor from Intel Corporation [12]. In the digital signal processor domain, the TMS320C40 chip from Texas Instruments

Inc.[13] includes 6 communication ports to facilitate various data communication schemes.

A recent announced TMS320C80 chip includes 4 digital signal processors and employs programmable MIMD architecture to reach more than 2 billion operations per second [14].

### 1.2.1 Trends of VLSI Technologies

Intense competition between semiconductor manufacturers expedites the pace of technological development. The technology gap between memory LSIs and logic LSIs is becoming smaller, although the advance of process technology becomes difficult. Along with advances in silicon fabrication techniques, the ability to produce micromachines on a silicon substrate is also improved. In this section, progresses of VLSI technologies over the past decade will be reviewed. From the trend, future prospects of VLSI technologies can be drawn.

### 1.2.1.1 Microprocessors

Microprocessors have been one of the most strongly contested areas. While one decade ago, NMOS technology was the dominant technology, currently, CMOS technology has taken the lead. The feature size of a transistor continue to shrink and submicron technology became available in designing microprocessor since 1991. Recently, 0.4- $\mu m$  technology has been used to implement a microprocessor. Figure 1.2 shows the trend of transistor feature size of a microprocessor. The plus signs in the figure are data mainly collected from the IEEE International Solid-State Circuits Conference. The solid line shown is the line best fits all data, that is, with minimum distances to all collected data. The dashed line is the line best fits data from smallest feature size of every year. The circle signs represent prediction of the next years from the solid line, and the x-mark signs represent prediction of the next years from the dashed line. Figures below will follow similar conventions. From prediction, in the year 2000, a feature size of 0.29  $\mu m$  can be widely used in the production of microprocessors.

Figure 1.2: Trend of transistor feature size in a microprocessor.

On the other hand, the silicon area of a microprocessor chip available has become larger and larger as shown in Fig. 1.3. As a transistor feature size keep on shrinking, and a chip size keep on increasing, the intergration level of a chip becomes enormous. We started to see chips with more than 1 million transistors in 1990. Nowadays, it has become quite common to build million-transistor chips. Predictably, a chip with about 10 million transistors will be quite common in the year of 2000. Figure 1.4 shows the trend of integration level.

Clocking speeds of CMOS microprocessors continuously set tremendous records. Fig. 1.5 shows the increase of clock rates over the past decade, and the prediction of future years up to the year 2000. As Fig. 1.5 shows, the highest achievable clock rate has increased about 18 times over the past decade. From prediction, clock rates can possibly go up to more than 1 GHz by the year 2000. In 1994, low power design becomes a strong design consideration which should be an integral part of the whole design process to keep up with

Figure 1.3: Trend of microprocessor chip size.

Figure 1.4: Trend of number of transistors in a microprocessor.

Figure 1.5: Trend of clock rates of microprocessors.

the competition. When considering low power design, clock rates drop as data from 1994 show.

With a higher clock rate, more operations can be performed for the same period of time. Figure 1.6 shows the trend of MIPS rates. It is expected by the year 1998, more than 1000 MIPS can be reached, and in the year 2000, about 2700 MIPS rate will be possible.

#### 1.2.1.2 Memories

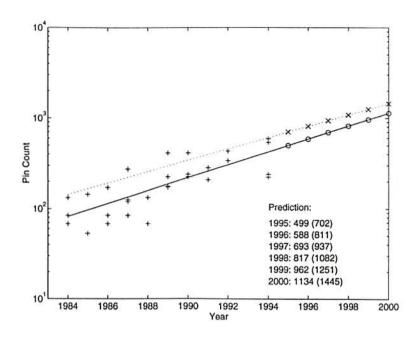

Feature sizes of memories usually are smaller than those of microprocessors. Engineers continue to exploit smaller devices to construct denser static random access memory (SRAM) and dynamic random access memory (DRAM). Figures 1.7 and 1.8 show the trends and predictions of device feature sizes for SRAM and DRAM, respectively. By looking at the two optimistic lines in both figures, we can find both kinds of memories have possibilities of being constructed by devices under 0.1  $\mu m$  in the year 2000.

Figure 1.6: Trend of performance of microprocessors.

Figure 1.7: Trend of transistor feature sizes of SRAM.

Figure 1.8: Trend of transistor feature sizes of DRAM.

From the trends of memory cell sizes as shown in Figs. 1.9 and 1.10, we can find that designers of DRAMs agree in the sizes in 1994. They all design memory cells of 0.72  $\mu m^2$  with 0.25  $\mu m$  technologies. By the year of 2000, a DRAM cell with area smaller than 0.1  $\mu m^2$  can be produced to construct 1G or even 4G-DRAM.

#### 1.2.1.3 Power Consumption

VLSI applications involve both high-end and low-end markets. The high-end markets include high-end workstations with an ultra high-speed CISC/RISC processor, that is, "hot chip". The low-end markets include personal digital consumer products using "cold chip" to realize battery-operated capability. Digital signal processors for digital cellular phones, whose power dissipation is minimized by optimized circuit design are the beginning of the "cold chip". Although the increase rate of clocking speeds will decrease because of supply-voltage scaling and power constraints. Development of "hot chips" will follow the trend discussed previously. On the other hand, the "cold chips" will show a steeper

Figure 1.9: Trend of SRAM cell size.

Figure 1.10: Trend of DRAM cell size.

slope in the power reduction as shown in Figure 1.11 [15] resulting from low-power circuit techniques, optimized architecture and improved system algorithm.

Figure 1.11: Trend of power consumption of microprocessor and digital signal processors [15].

#### 1.2.1.4 Packaging

The pin-count of a chip has increased rapidly as Fig. 1.12 shows. Multi-chip modules (MCMs) in a variety of configurations have emerged over the last few years as a possible method to raise system speed and reduce weight and volume [16]. The predominant focus has been in the digital arena where the ever-increasing chip I/O count has led to poor surface area of a board due to conventional packaging inefficiencies. In addition, as the clocking speeds for digital chips move beyond 50 MHz, packaging becomes a major factor limiting overall system speed. Several benefits result from interconnecting complex chips using a fine-pitch MCM technology. First, because MCM technologies allow chips to be placed next to each other, interconnect parasitics due to conventional packaging of single components and board interconnect length are virtually eliminated. As a result, such

Figure 1.12: Trend of pin-count of a chip.

an implementation yields higher operating frequencies. Second, board area and weight are reduced. An example from General Electric Company is a quad digital-signal processor module implemented in the high density interconnect process. This design uses four TMS320C25 processors and contains 36 tile-packed chips in a  $1.3 \times 1.3 \ in^2$  array. The 12-gram design executes 180 MIPS at clock rates approaching 100 MHz. Implementations of the same design using conventional surface-mount packaging techniques are rated for 40 MHz and are about 5 times larger [17]. Another example is a MCM-based CCITT H.261 codec with 50% reduction in the power dissipation and 98% reduction in the total system area from a board design [18].

# 1.3 Artificial Neural Networks

The capability of processing massive data parallelly by artificial neural networks (ANNs) gives the possibility of generating high-quality signals and images for real-time applications. Also, high performance computing and computer communication networks are becoming

then conducted to justify whether the requirements such as timing constraints are met. If some constraint is violated, some portion of the system must be turned into hardware. The design gradually moves software to hardware. In contrast to this process, a designer can start from a major-hardware system and gradually moves hardware to software according to performance evaluation.

# 1.5 Organization of This Dissertation

The rest of this dissertation is organized as follows.

Chapter 2 introduces the problems in designing a new-generation intelligent information processing machine. The methodologies of applying artificial neural networks to solve these problems will be given together with related work accomplished by other researchers.

Chapter 3 presents the method of applying hardware-based simulated annealing to artificial neural networks for achieving optimal solutions. Analog/Digital (A/D) decision networks constructed from Hopfield-type networks with two-level and multi-level neurons are used in demonstration of the annealing method.

Chapter 4 describes the methodology of using hardware-software codesign techniques in designing neural hardware. Architecture selections of a system and a processor are discussed. Several algorithms of neural networks will be mapped onto the neural system. Details of digital VLSI processing element design is presented.

Chapter 5 covers the software design portion of the processing element. Several realworld applications are demonstrated to show how to use a proposed multi-PE chip.

Chapter 6 summarizes the results of the thesis, points out the impact of the dissertation work, and gives pointers to future research that can be based on this exemplary work at the current status.

Appendix A lists journal and conference publications out of the dissertation work.

increasingly important to scientific advancement, economic competition, and national security. The Federal High Performance Computing and Communications (HPCC) Program has been driven by the recognition that unprecedented computational power and capability is needed to investigate and understand a wide range of scientific and engineering "grand challenge" problems [19]. These are fundamental problems whose solutions are critical to national needs. Examples of grand challenges addressed include: prediction of weather, climate, and global changes; improving research and education communications; and understanding the nature of new materials. The systems which will be discussed in this dissertation will be good candidates for dealing with the HPCC Programs with its fundamental properties of high computing power and high speed.

Different implementation methods have been used for constructing neurocomputers [20]-[22]. Optical and electronic implementations are two main streams. Mature CMOS VLSI technology and existing successfully implemented microcomputers make the electronic implementation immediately attractable. On the other hand, optical implementation has capabilities of achieving high bandwidth, 3-dimensional interconnect ideally. Whereas, the optical approach has several challenges. Efficient weight storage and computation in pure optics is still difficult to do, although improving. Electro-optics has significant conversion problems in that creating photons is hard to do electronically with reasonable cost-performance. Moreover, it is still very expensive to implement optically. Therefore, no volume to bring prices down like the silicon technology [22].

# 1.4 Hardware-Software Codesign

In hardware-software codesign, people consider tradeoffs between hardware and software so as to fulfill behavior and performance goals of a system. Some portions of a system are more suitable to be hardwired to gain higher speed while some portions are preferred to be software programmable. The codesign process can also be considered as a partitioning problem. For example, codesign can start from a system configuration which only consists of software modules on a standard core processor. Performance evaluation of the system is

# Chapter 2

### Neural Network Models

Artificial neural computing has enjoyed a rise in popularity due to advances in VLSI technology and the inability of previous generation computers to quickly and efficiently generalize and learn. They are networks of neurons connected together in layers, processing information asynchronously or synchronously.

Hardware implementation of neural networks utilize a parallel processing structure that has large number of processing elements (PEs) and many interconnections between them. A PE is also sometimes called a processor. A PE performs much simpler functions than a typical central processing unit (CPU) does. In a neural network, each PE is linked to many of its neighbors so that there are the number of interconnections is much larger than that of PEs. The power of a neural network lies in the tremendous number of interconnections.

What has triggered the most interest in neural networks is that models similar to biological nervous systems can actually be made to do useful computations. Furthermore, the

capabilities of the resulting systems provide an effective approach to previously unsolved

problems. However, neural networks can be difficult to train and unsuitable for some

tasks. So why use them? Because they offer valuable characteristics unavailable together

elsewhere. First, they can infer subtle, unknown relationships from data. Second, the networks can generalize, meaning they can respond correctly to patterns that are only broadly

similar to the original training patterns. Generalization is useful because real-world data

is noisy, distorted, and often incomplete. Third, they are nonlinear, that is, they can solve

some complex problems more accurately than linear techniques do. Nonlinear is common, but can be difficult to handle mathematically. Finally, they are highly parallel.

# 2.1 Biological Neural Networks

Neural network architectures are motivated by models of our own brains and nerve cells. A human brain consists of approximately 10<sup>11</sup> computing elements called neurons [23, 24]. They communicate through a connection network of axons and synapses having a density of approximately 10<sup>4</sup> synapses per neuron. A typical neuron has three major regions: the cell body, which is also called the soma, the axon, and the dendrites as shown in Fig. 2.1 [24]. The soma provides the support functions and structure of the cell. The axon is a branching fiber that carries signals away from the neuron, and the dendrites consist of more branching fibers that receive signals from other nerve cells. The connecting point between an axon and a dendrite is the synapse. The synapse is where the neuron introduces its signal which is a pulse to the neighboring neuron. The synapse is capable of changing a dendrite's local potential in a positive or negative direction, depending on the pulse it transmits. The interneuronal transmission is sometimes electrical but is usually effected by the release of chemical transmitters at the synapse [25]. Therefore, it occurs fairly slowly.

A neuron is able to respond to the total of its inputs aggregated within a short period of time. The neuron's response is generated if the total potential of its membrane reaches a certain level. Incoming impulses can be excitatory if they cause the firing of the response, or inhibitory if they hinder the firing of the response. If the excitation exceeds the inhibition by the threshold amount, which is typically  $40 \ mV$  [26], a firing occur. The characteristic feature of the biological neuron is that the signals generated do not differ significantly in magnitude; the signal in the nerve fiber is either absent or has the maximum value. In other words, information is transmitted between the nerve cells by means of binary signals.

Figure 2.1: Biological Neuron [24].

By understanding of the basic concepts of a biological neural network (BNN), it is helpful for the design of a powerful artificial neural network which can solve problems that today's machine cannot accomplish.

### 2.2 Artificial Neural Networks

A traditional Von Neumann machine has a single CPU that performs all of its computations in sequence. A typical CPU is capable of a hundred or more basic commands, including adds, subtracts, loads, and shifts, among others. The commands are executed one at a time, at successive steps of a time clock. In contrast, a neural network processing unit may do only a few commands. Incremental changes are made to parameters associated with interconnections. This simple structure nevertheless provides a neural network with the capabilities to classify and recognize patterns, to perform pattern mapping, and to be useful as a computing tool.

Some of the operations that neural networks perform include [27, 28].

Classification - an input pattern is passed to the network, and the network produces

a representative class as the output.

- Pattern matching an input pattern is passed to the network, and the network produces the corresponding output pattern.

- Pattern completion an incomplete pattern is passed to the network, and the network produces an output pattern that has the missing portions of the input pattern filled in.

- Noise removal a noise-corrupted input pattern is presented to the network, and the network removes some, or all, of the noise and produces a cleaner version of the input pattern as output.

- Optimization an input pattern representing the initial values for a specific optimization problem is presented to the network, and the network produces a set of variables that represents a solution to the problem.

- Control an input pattern represents the current state of a controller and the desired response for the controller, and the output is the proper command sequence that will create the desired response.

A comparison of biological and artificial neural networks can give us a clearer picture of what we have achieved and what need to be done in the future. Table 2.1 lists the comparison. In the table, artificial neural networks are considered in terms of digital implementation. The major difference between biological and artificial neural networks is in the complexity of the synapses. The biological synapses contain many components and active processes. The strength of biological synapses maybe affected by several factors such as size and number of synaptic vesicles; content of synaptic vesicles; influx and outflow of ions; release and uptake rates of neurotransmitters, etc [29].

In contrast, artificial neural networks have relatively simple interconnections. For example, during the feedforward phase in a standard multi-layer perceptron network, an operation can be expressed with a simple linear weighted sum combined with a nonlinear sigmoid function which performs thresholding. Other simple calculations may be done,

such as inhibition and competition. Sometimes, additional terms are added to the summation functions, such as a dependency on past changes, or the addition of second-order terms. However, these do not rival the biological synaptic processes in complexity.

BNNs send signals from one unit to another by means of impulse transmission. ANNs can transfer precise scalar values from unit to unit. Biological impulse transmission takes place at any time and its timing is determined by incoming signals. Artificial networks update their parameters periodically, in discrete time steps. Usually the whole network is updated during some specific period of time. Thus artificial networks can be considered to have synchronous updating, whereas in biological systems the updating is asynchronous. Biological neurons update whenever an impulse arrives, and may also have parameters that decay or change between arrivals.

One advantage of artificial networks is that the scalar values that are transferred from unit to unit can be implemented to be relatively precise. In biological neural networks, a single interconnection does not transfer a precise scalar value. If average firing rate is considered to be the value transferred, then it has limited precision, especially over a short time frame. Biological networks have a built-in temporal structure because impulses can occur at any time, and thus may form temporal patterns. The summation in the two systems must be done differently as a result of their different signaling characteristics.

Biological networks have predetermined wiring at the system level. For example, the major fibers and connections in the visual and auditory systems are the same for different individuals; at a more detailed level the circuitry appears to be different for different individuals. For example, animals with exactly the same genes do not have corresponding neurons with the same dendritic branching structure and topology.

ANNs are usually layered and fully interconnected, with all units in a given layer connected to all units in the layers above and below. Artificial networks can also be sparsely interconnected, or have connections removed selectively after training. Biological networks have layered structures. However, the layers are not simple rows of independent units, as in most artificial networks, and the neurons in each layer or cluster tend to be

Table 2.1: Comparison between a human brain and artificial neural networks.

| Element                     | BNN                                                                           | ANN                                                              |

|-----------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------|

| Organization                | network of neurons                                                            | network of PEs                                                   |

| Components                  | Dendrites and axons Synapses Summer Threshold                                 | Inputs and outputs Weights Summation function Threshold function |

| Architecture                | fixed gross wiring architec-<br>ture, plus variation in<br>detailed structure | usually fully intercon-<br>nected                                |

| Neurons                     | 100 billion                                                                   | usually up to 100                                                |

| Synapses                    | complex                                                                       | simple                                                           |

| Interconnections per neuron | 10,000                                                                        | within 10                                                        |

| Processing                  | analog                                                                        | digital                                                          |

| Technology                  | biological                                                                    | silicon<br>optical<br>molecular                                  |

| Hardware                    | neuron                                                                        | switching device                                                 |

| Switching speed             | 1 msec                                                                        | 10-100 nsec                                                      |

| Updating                    | continuous or asynchronous                                                    | synchronous                                                      |

| Learning                    | as fast as one pass                                                           | slow to converge                                                 |

| Signal                      | pulse transmission                                                            | activity value and con-<br>nection strengths                     |

| Reliability                 | redundancy                                                                    | redundancy                                                       |

densely interconnected to one another, again in contrast to most artificial networks. The layers in biological systems are not fully interconnected with layers above and below in the simplistic way that is found in many artificial systems, as biological connections may be sparse or may involve more than one synapse. Three-dimensional packing considerations discourage fully interconnected topologies for biological systems, and also pose a constraint in designing neurocomputing hardware.

Feature detectors occur in both biological and artificial systems. Distributed representation and processing is a characteristic of both biological and artificial networks. A pattern mapping, for example, uses the entire network, not just a single location in the network, to determine its output pattern given the input pattern. Redundancy, occurs in both biological and artificial networks, can increase the reliability of a system, allowing it to function even when some of the neural units are destroyed. In addition, redundancy may also counteract sources of noise.

Biological networks have the remarkable property of being able to learn in as little as one training presentation. In contrast, artificial networks usually require hundreds or thousands of training presentations in order for learning to take place, and are usually slow to converge.

### 2.2.1 Data Representation

Neural networks are made out of neuron-like nodes that are arranged in layers. Data as passed through weighted connections between nodes. The networks learn by changing the values of their weights. With suitable weights, a network can model any computable function. Figure 2.2 shows a typical three-layer fully-connected feedforward neural network. A neuron and a synapse are two fundamental components in an artificial neural network. Depending on the architecture and dynamics of a network, some additional components may be added. The synapse represents connection between two neurons with a weight value indicating the strength of the connection. The neuron does operations on input data and synapse weights.

Figure 2.2: Architecture of a typical three-layer fully-connected neural network.

#### 2.2.1.1 Two-Level Neuron

A typical two-level neuron can be modeled by

$$S(x) = cf(x - \theta). \tag{2.1}$$

The transfer function f transforms an input value x into one of two output levels. Here,  $\theta$  is the threshold value of the neuron, and the scaling factor c is typically one. The transfer function f is continuously and monotonically increasing [25, 30]. The sigmoid function has been widely used in the neural network research community. This function is a bounded differentiable real function that is defined for all real input values, and it has a positive derivative value everywhere. By using the sigmoid function as the transfer function, (2.1) becomes

$$S(x) = \frac{c}{1 + e^{-(x-\theta)}}. (2.2)$$

Most neural networks in the literature use two-level neurons to classify input signals.

A two-level neuron produces output with 1-bit accuracy. As the number of input signals

increases, the number of synapse weights increases accordingly. A large number of synapse weights will complicate the interconnection wiring between neuron layers, and significantly limit the size of a network to be implemented by a VLSI chip.

#### 2.2.1.2 Multi-Level Neuron

The output of each multi-level neuron represents multiple bits. Therefore, the total network size of a neural network composed of multi-level neurons can be significantly smaller than a conventional network with two-level neurons. The reduction in network size is a highly desirable feature in VLSI neuroprocessor implementation for large-scale applications. Recently, a neuron circuit performing multi-level transfer function has been proposed [31]. To represent a multi-level neuron with m threshold values,  $\theta_0$  to  $\theta_{m-1}$ , a neuron transfer function of the form [31]

$$M(x) = \sum_{j=0}^{m-1} c_j f_j(x - \theta_j)$$

(2.3)

can be used. The scaling factor for the p-th level is  $c_0 + c_1 + \cdots + c_p$ . Therefore, the output level has a step size of  $\Delta k_p = c_p$ . In addition,  $\theta_p < \theta_{p+1}$  holds for  $0 \le p \le m-1$ . The accumulation function M(x) is a monotonically increasing function. Again, by replacing  $f_j$  with the sigmoid function, (2.3) becomes

$$M_s(x) = \sum_{j=0}^{m-1} \frac{c_j}{1 + e^{-(x-\theta_j)}}.$$

(2.4)

### 2.2.2 Major Network Architectures

Over the decades of the exploitation of biological neural networks, several different types of models have been highly discussed and developed. In this section, some major types of neural network architectures will be described. The way of realizing these networks by digital VLSI will be discussed in later chapters.

#### 2.2.2.1 Iterative Networks

In an iterative network, the output nodes of neurons feedback to the input nodes of neurons through interconnecting weights. Typically, iterative networks are started at some initial state, and then are converged to one of a finite number of stable states. There are three basic goals in the design of iterative networks. First, given any initial state, a network should always converge to some stable state. Second, the stable state to which the network converges should be the one closest to the initial state, as measured by some metric. Third, it should be possible to have as many stable states as desired. Some examples are the Hopfield network [32, 33], the Bidirectional Associative (BAM) network [34], the Brain State in a Box (BSB) network [35].

Figure 2.3 shows the architecture of a Hopfield network with two-level neurons. The output of the network changes until a stable state is reached. The initial state of the output has influence on the final output. Some initial states can cause nonconverging outputs. An external input  $x_a$  can be added to the input nodes of neurons to direct the operation of the network.

Figure 2.3: Architecture of a Hopfield network with two-level neurons.

The Hopfield network has two major limitations when used as a content addressable memory. First, the number of patterns that can be stored and accurately recalled is severely limited. If too many patterns are stored, the network may converge to a novel spurious pattern different from all exemplar patterns. Such a spurious pattern will produce a "no match" output when the network is used as a classifier. Hopfield [36] showed that this occurs infrequently when exemplar patterns are generated randomly and the number of classes is less than 0.15 times the number N of input elements or nodes in the network. Therefore, the number of classes is typically kept well below 0.15N. A second limitation of the Hopfield network is that an exemplar pattern will be unstable if it shares many bits in common with another exemplar pattern. This problem can be eliminated, and performance can be improved by a number of orthogonalization procedures [30].

### 2.2.2.2 Multi-Layer Perceptron Networks

The network is usually structured as shown in Fig. 2.2. A neuron in such a network typically multiplies each input by its weight, sums the products, then passes the sum through a nonlinear transfer function to produce an output. The fundamental computation for a neural network is therefore the vector dot-product, and its computational speed depends on executing the underlying multiply-and-accumulate operations efficiently. Each neuron has an extra input called the threshold input, which acts as a reference level or bias for neurons. The intermediate hidden layer enhances the network's ability to model complex functions. The transfer function is usually a sigmoid function. The attenuation at the upper and lower limbs of the S-shape curve constrains the raw sums smoothly within fixed limits. The transfer function also introduces a nonlinearity that further enhances the network's ability to model complex functions [37].

The most popular training algorithm used in these networks is the back-propagation training. Synapse weights are adjusted by the back-propagation technique in the direction opposite to the instantaneous error gradient. Because it is possible to calculate the errors, the training data must contain a series of input patterns labeled with their target output patterns.

During the training time, a network adjusts its synapse weight values through consecutive cycles of feedforward and back-propagation phases until predefined requirements are reached. During the running time, the trained network uses its weight values to obtain outputs through a feedforward phase.

Operations of a feedforward phase can be formulated as,

$$S_j(L) = \sum_{i=1}^{m_L} w_{ji}(L) \cdot a_i(L-1)$$

(2.5)

and

$$a_j(L) = f_j(S_j(L), \theta_j(L)), \tag{2.6}$$

where L represents the layer number,  $w_{ji}(L)$  is the weight between the neuron j in the  $L^{th}$  layer and the neuron i in the  $(L-1)^{th}$  layer, and  $m_L$  is the total number of neurons in the  $L^{th}$  layer.

During a back-propagation phase, a network passes derivatives of output errors back to a hidden layer, using the original weighted connections. Each hidden neuron then calculates the weighted sum of the back-propagated errors to find its indirect contribution to the known output errors. After each input and hidden neuron finds its error value, the neuron adjusts its weights to reduce its error. The weight updating rules can be formulated as follows:

$$\Delta w_{ji}(L+1) = \eta \delta_j(L+1) \cdot a_i(L) \tag{2.7}$$

$$w_{ji}^{new}(L+1) = w_{ji}^{old}(L+1) + \Delta w_{ji}(L+1). \tag{2.8}$$

The calculations for  $\delta_j$ 's are different in the output layer and in the hidden layers. For the output layer:

$$\delta_j(L) = (t_j(L) - a_j(L)) \cdot f_j'(S_j(L)),$$

(2.9)

and for each hidden layer:

$$\delta_j(L) = e_j(L) \cdot f_j'(S_j(L)), \tag{2.10}$$

where

$$e_j(L) = \sum_{k=1}^{m_{L+1}} \delta_k(L+1) \cdot w_{kj}(L+1). \tag{2.11}$$

Here,  $\delta_j$  is the error term in the present layer,  $\delta_k$  is the error term in the next layer,  $t_j$  is the corresponding desired output for the  $j^{th}$  neuron,  $\eta$  is the updating rate and can be either a local variable or a global constant. The equations that change the weights are designed to minimize the sum of the network's squared errors. This minimization has an intuitive geometric meaning. To see it, all possible sets of weights must be plotted against the corresponding sum-of-squares errors. The result is an error surface shaped like a bowl, whose bottom marks the set of weights with the smallest sum-of-squares error. Finding the bottom of the bowl-that is, the best set of weights-is the goal during training.

Back-propagation achieves the goal by calculating the instantaneous slope of the error surface with respect to the current weights. It then incrementally changes the weights in the direction of the locally steepest path toward the bottom of the bowl. This process resembles rolling a ball down a hill and is called *gradient descent*. Since gradient descent always follows the locally steepest path, the back-propagation algorithm can train a network into a local minimum that it cannot escape. This effect depends on the exact path down the gradient, which in turn depends on the initial values of the weights and other factors.

Back-propagation training is a kind of supervised learning. We call it supervised because the desired results are known in advance before learning, weight updating of a network can be directed by minimizing the difference between the actual output and the desired output. On the other hand, there are many cases that we don't know what are the correct responses of a network. Unsupervised learning is performed under these cases. The next network we will discuss is a kind of unsupervised learning.

## 2.2.2.3 Kohonen Self-Organizing Feature Map

The feature mapping algorithm is supposed to convert patterns of arbitrary dimensionality into the responses of one- or two-dimensional arrays of neurons [38, 39, 40]. Learning within

self-organizing feature maps results in finding the best matching neuron cells which also activate their spatial neighbors to react to the same input. Such collective and cooperative learning tunes the network in an orderly fashion by defining some feature coordinates over the trained network. After learning, each input causes a localized response having a position on the neurons' array that reflects the dominant feature characteristics of the input. A basic structure of the self-organizing feature map is shown in Fig. 2.4.

Figure 2.4: A basic structure of the self-organizing feature map.

The Kohonen self-organizing feature map has been shown to be quite effective for vector quantization (VQ) codebook design [41, 42, 43, 44]. For a full-search VQ, N distortion measures between an input vector and N code vectors are computed, and then the code vector, which is nearest to the input data, is chosen. Let  $\vec{X} = x_j$  represents the k-dimensional input vector, and  $\vec{C}_i = c_{ij}$  represents the i-th code vector in the codebook. The required computation is to find the minimum of the distance:

$$\min\left\{d(\vec{X}, \vec{C}_i), \ 1 \le i \le m\right\},\tag{2.12}$$

where

$$d(\vec{X}, \vec{C}_i) = \sum_{j=1}^{k} (x_j - c_{ij})^2$$

is the distortion measure between  $\vec{X}$  and  $\vec{C}_i$ .

### 2.2.2.4 Comparison

In the following, the three types of neural architectures discussed previously along with perceptron, and Boltzmann machine are compared. The perceptron is primarily of historical interest, although it is still occasionally used. It receives inputs from several resources, and determines the output to be either logical-0 or logical-1 depending on the sum of the inputs being smaller than or greater than zero. The Boltzmann machine will be discussed further in the next chapter. Table 2.2 lists the strengths, limitations, and primary applications of the five types of artificial neural networks [45].

Table 2.2: Comparison of various neural network models.

| Neural models               | Example applications                                             | Strength                                                                      | Limitation                                       |

|-----------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------|

| Perceptron                  | linear filters                                                   | early neural network                                                          | cannot recognize complex patterns                |

| Hopfield                    | retrieval of data/images<br>from fragments                       | large-scale integra-<br>tion                                                  | weights not adaptable                            |

| Multi-Layered<br>Perceptron | wide range: speech<br>synthesis to loan-appli-<br>cation scoring | most popular, work<br>well, simple learn-<br>ing rules                        | supervised training<br>with abundant<br>examples |

| Self-organizing<br>Map      | pattern classification                                           | better performance<br>than many algorith-<br>mic techniques                   | extensive learning                               |

| Boltzmann<br>Machine        | pattern recognition for<br>radar/sonar                           | simple network that<br>uses noise function<br>to jump out of local<br>minimum | very long training time                          |

## Chapter 3

# Multi-Level Neural Networks with Optimal Solutions

Search for fast optimization in scientific and engineering applications has drawn researchers' interest in the field of engineering neural networks. A typical neural network for solving optimization problems multiplies input signals with synapse weights, and the summed results are processed by the output neurons.

The gradient descent method is a conventional approach for optimization. It finds the gradient of the cost function to determine the direction for the next processing step. This method suffers from the inherent problem of possibly converging at a local minimum in the cost function. Recently, Yuh and Newcomb [31] presented a method using a correction logic circuit to obtain the optimal solutions for multi-level Hopfield networks. Alspector et al. [46] have pioneered the analog electronic implementation of the Boltzmann machine by adding uncorrelated noise to find the globally optimal solution. Simulated annealing [47, 48] is another important method for searching for the optimal results on digital computers. It is a stochastic process modeled after metallurgical annealing. The metallurgical annealing consists of heating a raw material such as silicon to its melting point, then slowly cooling it based on a predetermined cooling schedule. If the raw silicon is cooled slowly, and a single-crystal seed is provided, atoms will fit into the lattice sites and reach a lower energy equilibrium. The slow decrease of the cooling temperature and the natural tendency towards a minimum-energy state are the key factors of metallurgical annealing and the Czochralski growth of purified semiconductors [49]. Due to a slow cooling schedule in software execution, the simulated annealing method on digital computers requires a lot of

computing time for a complex optimization problem. By constructing a hardware-based parallel annealing technique in analog electronics, the processing speed can be significantly improved.

A high-quality semiconductor crystal can be formed by providing a seed as a guidance in the process of metallurgical annealing. On the other hand, if no seed is provided, the melting semiconductor will be cooled down to an amorphous condition. In hardware annealing, which is an analog hardware version of the mean-field annealing [50, 51], an external bias voltage provides a similar effect as the seed in metallurgical annealing. During the whole annealing process, the constant external bias directs the outcome of a network. If no bias is applied, the output of the network undergoes influence from residual capacitances of the output nodes initially. These capacitances constitute the initial states of the network. Outputs of the network becomes unpredictable if the network goes through the annealing process without the external bias.

## 3.1 Simulated Annealing

The Hopfield network is a recurrent network which finds the stable solution through iterations. Due to the nonlinear property of the network, the output could be stable at one of the local minima. Simulated annealing helps to escape from local minima by using the Boltzmann distribution function as the transfer function of a neuron. Software implementation of simulated annealing uses the the following procedure:

```

Simulated_Annealing(init_state)

begin

stop := false;

while (stop = false)

begin

while (equilibrium is not established)

begin

Temp := some high temperature;

current_state := init_state;

new_state := selection_function(neighborhood of current_state);

```

## 3.2 Paralleled Hardware Annealing

In the Hopfield A/D network, a neuron with m-bit resolution is realized by 2<sup>m</sup> amplifiers connected in parallel with their output currents summed together [31]. The summed current can be converted to the output voltage of the neuron by a current-to-voltage converter. The output voltages are connected back to the neuron inputs through interconnection conductances. An analog input value and a reference voltage are applied to all neurons. In hardware annealing, we change the voltage gain of the neurons in a continuous manner to achieve a similar effect as changing temperature in simulated annealing. Recently, some researchers have discussed methods of how to construct a gain-adjustable amplifier [52, 46, 53].

In the following, an analog-to-digital (A/D) decision network is used to illustrate the properties of using hardware-annealing in Hopfield networks with multi-level neurons because the optimal solution of an A/D decision network is always known [32, 33, 54].

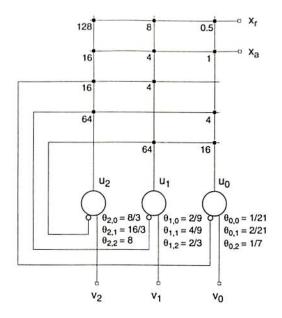

A schematic diagram of a 6-bit A/D decision network by using three 4-level neurons are given in Fig. 3.1. A governing equation for the *i*-th neuron in an N-neuron network can be expressed as

$$C_i \frac{du_i}{dt} + G_i u_i(t) = \sum_{j \neq i, j=0}^{N-1} G_{ij} v_j(t) + I_i(t),$$

(3.1)

Figure 3.1: A Hopfield 6-bit neural A/D decision network with 4-level neurons.

and

$$I_i(t) = G_{ri}x_r(t) + G_{ai}x_a(t), \tag{3.2}$$

where  $C_i$  and  $G_i$  are the equivalent total capacitance and conductance at the input node of the *i*-th neuron,  $G_{ij}$  is the conductance between the *i*-th and the *j*-th neurons,  $x_r$  is the reference voltage,  $x_a$  is the input analog voltage,  $G_{ri}$  and  $G_{ai}$  are the conductances connecting  $x_r$  and  $x_a$  to the *i*-th neuron. The voltage at the input node of the *i*-th neuron is  $u_i(t)$ , and the output voltage of the *j*-th neuron is  $v_i(t)$ .

The energy function for the network can be expressed as

$$E = -\frac{1}{2} \sum_{i=0}^{N-1} \sum_{j \neq i, j=0}^{N-1} G_{ij} v_i v_j - \sum_{i=0}^{N-1} I_i v_i + \sum_{i=0}^{N-1} G_i \int_0^{v_i} g_i^{-1}(v) dv,$$

(3.3)

where  $g(\cdot)$  is the voltage transfer function of the amplifier. The time derivative of the energy function is

$$\frac{dE}{dt} = -\sum_{i=0}^{N-1} \frac{dv_i}{dt} \left[ \sum_{j \neq i, j=0}^{N-1} G_{ij} v_j - G_i u_i + I_i \right]. \tag{3.4}$$

Substituting (3.1) into (3.4), we can obtain

$$\frac{dE}{dt} = -\sum_{i=0}^{N-1} \frac{dv_i}{dt} C_i \frac{du_i}{dt} = -\sum_{i=0}^{N-1} C_i g_i^{-1}(v_i) \left[ \frac{dv_i}{dt} \right]^2.$$

(3.5)

Since  $C_i$  is a positive value,  $\frac{dE}{dt} \leq 0$  if  $g_i(\cdot)$  is chosen to be a monotonically increasing function. The operation of the network evolves in the direction of decreasing the energy of the network until the equilibrium state is reached.

The function of an A/D decision network is to find a digital word which is a best representation of the analog input signal  $x_a$ . The synapse weight values can be determined by minimizing the squared value of the difference between the input analog value and the corresponding digital representation [31]

$$E_o = (x_a - \sum_{i=0}^{N-1} m^i v_i)^2. \tag{3.6}$$

After expanding (3.6) and dropping the constant term  $x_a^2$ , we obtain,

$$\hat{E}_o = -\frac{1}{2} \sum_{i=0}^{N-1} \sum_{j \neq i, j=0}^{N-1} (-m^{i+j}) v_i v_j - \sum_{i=0}^{N-1} m^i x_a v_i + \frac{1}{2} \sum_{i=0}^{N-1} m^{2i} v_i^2.$$

(3.7)

By assuming uniform spacings between the neighboring threshold values and the output levels in the decision network, i.e.,  $\Delta\theta$  and  $\Delta k$  as defined in page 24 are constants, (3.3) can be reformulated as

$$E = -\frac{1}{2} \sum_{i=0}^{N-1} \sum_{j \neq i, j=0}^{N-1} G_{ij} v_i v_j - \sum_{i=0}^{N-1} (I_i - \frac{1}{2} G_i \Delta \theta_i \Delta k_i) v_i + \frac{1}{2} \sum_{i=0}^{N-1} G_i \Delta \theta_i \Delta k_i v_i^2.$$

(3.8)

By equating corresponding items in (3.7) and (3.8), we can obtain

$$G_{ij} = -m^{i+j}, (3.9)$$

$$I_i = m^i x_a + \frac{1}{2} G_i \Delta \theta_i \Delta k_i = G_{ai} x_a + G_{ri} x_r,$$

and

$$G_i \Delta \theta_i \Delta k_i = m^{2i}.$$

Here,  $\Delta\theta_i$  is the increment in the threshold value, and  $\Delta k_i$  is the increment in the outputlevel value at the *i*-th neuron. The weights, inputs and thresholds for the neurons from (3.9) are clearly labeled in Fig. 3.1. The negative conductances  $G_{ij}$ 's are implemented by taking results from the inverted outputs of the neurons. The  $G_{ri}$ 's are determined by setting  $x_r$  to be one.

Let us carefully examine the transfer function of the A/D decision network. Assume that all neurons are biased in the linear region. In the steady state condition,

$$u_i = \frac{\sum_{j \neq i, j=0}^{N-1} G_{ij} v_j + G_{ri} x_r + G_{ai} x_a}{G_i}$$

(3.10)

and

$$\theta_{i,k} \le u_i < \theta_{i,k+1} \tag{3.11}$$

for the k-th level at the i-th neuron. Substituting (3.10) into (3.11), we can obtain

$$\frac{-\sum_{j\neq i,j=0}^{N-1} G_{ij}v_j + G_i\theta_{i,k} - G_{ri}x_r}{G_{ai}} \le x_a < \frac{-\sum_{j\neq i,j=0}^{N-1} G_{ij}v_j + G_i\theta_{i,k+1} - G_{ri}x_r}{G_{ai}}.(3.12)$$

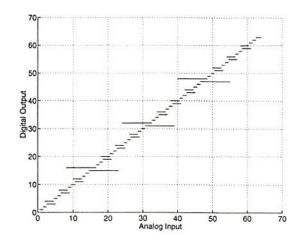

Figure 3.2 shows the plot of the transfer function of a three-neuron A/D decision network.

All the possible states determined by (3.12) are included. The output value of each neuron

Figure 3.2: Transfer function of a 6-bit A/D decision network with. 4-level neurons.

can be classified into one of four distinct levels. Please note that for some analog input values, the network can converge to different digital representations which correspond to multiple local minima in the energy function. For example, when the input value is 19.8, the output value may be 15, 19 or 20 depending on the initial conditions of the network.

A multi-level Boltzmann neuron function [31] can be modified from (2.4):

$$M_b = \sum_{i=0}^{m-1} \frac{c_i}{1 + e^{-\eta(x-\theta_i)}} \tag{3.13}$$