## **USC-SIPI REPORT #321**

### A Deep Submicron Drain-Current and Charge Model for MOS Transistors

by

**Hung-Min Jen**

August 1998

Signal and Image Processing Institute UNIVERSITY OF SOUTHERN CALIFORNIA

Department of Electrical Engineering-Systems 3740 McClintock Avenue, Room 404 Los Angeles, CA 90089-2564 U.S.A.

## Acknowledgments

I would like to express my deepest thanks to my research advisor Professor Bing J. Sheu, Department of Electrical Engineering and with joint appointment at Department of Biomedical Engineering, for his guidance and support throughout the course of my Ph.D. research. I wish to extend my sincere appreciation to Professor Sandeep Gupta, Department of Electrical Engineering, and Professor Michael Khoo, Department of Biomedical Engineering, for serving on my dissertation committee. I would also like to thank them along with Professor Murray Gershenzon, Department of Material Science, and Dr. Philip Tai for serving on my qualifying examination committee.

I am very grateful to Professor Leonard M. Silverman, Dean of the Engineering School; Professor Hans H. Kuehl, Chairman of the Electrical Engineering - Electrophysics Department; Professor Robert A. Scholtz, Chairman of the Electrical Engineering - Systems Department; Professor Chrysostomos (Max) L. Nikias, Director of Integrated Media Systems Center, which is an Engineering Research Center of National Science Foundation; Ms. Ramona Gordon, Ms. Anna Fong, Ms. Gloria Halfacre in the Electrical Engineering Program, for providing such a great research environment for my Ph.D. study at the University of Southern California. This research work conducted through connection with several research organizations within USC including Integrated Media Systems Center (IMSC), Center for Neural Engineering (CNE), Signal and Image Processing Institute (SIPI), and Information Sciences Institute (ISI).

Valuable industrial support for this research was made possible through Dr. David R. Pehlke, Wireless Technology Manager, Rockwell International Corp./Science Center. Supplementary support was also provided by Dr. James Cable, Advanced Technology Manager, VHSIC Program Manager of TRW Electronic

System Group; Dr. Michael Schroter, Design Automation Center Manager, Rockwell Semiconductor Systems; and Dr. Christian Enz, Design Automation Principal Engineer, Rockwell Semiconductor Systems.

Valuable discussions with graduate doctoral colleagues from VLSI Multimedia Laboratory were truly stimulating, including Dr. Sudhir M. Gowda (now Research Staff Member at IBM T. J. Watson Research Center, Yorktown Heights, NY), Dr. Robert C. Chang (now Associate Professor at National Chung Hsing University, Taiwan), Dr. Tony H. Wu (now Senior Design Engineer at Divio Inc., Sunnyvale, CA), Dr. Eric Y. Chou (now Member of Technical Staff at HP Communication Semiconductor Solutions Division, San Jose, CA), Dr. David C. Chen (now Marketing Specialist at United Semiconductor Corp., Taiwan). Many thanks to Alex Y. Park, Richard H. Tsai, Michelle Y. Wang, Austin K. Cho, Wayne, C. Young, Suat U. Ay, John S. Lee, James J. Cho, and Jim C. Tai for friendly interaction.

I am eternally grateful to my parents, Yi-Hui Cheng and Lu-Yu Cheng, and my sisters, Chiao-Min Cheng, Chiao-Hsin Cheng, and Chieh-Wen Cheng, for their love and support throughout all these years. This research work was partially supported by National Science Foundation under Grants ECS-9322279.

## Contents

| Li | st O | Tables          |                  |         |        |           |     |      |    |   |     |    |   | v               |

|----|------|-----------------|------------------|---------|--------|-----------|-----|------|----|---|-----|----|---|-----------------|

| Li | st O | Figures         |                  |         |        |           |     |      |    |   |     |    |   | vi              |

| 1  | Intr | oduction        |                  |         |        |           |     |      |    |   |     |    |   | 1               |

|    | 1.1  | Deep-Submicro   |                  |         |        |           |     |      |    |   |     |    |   | 2               |

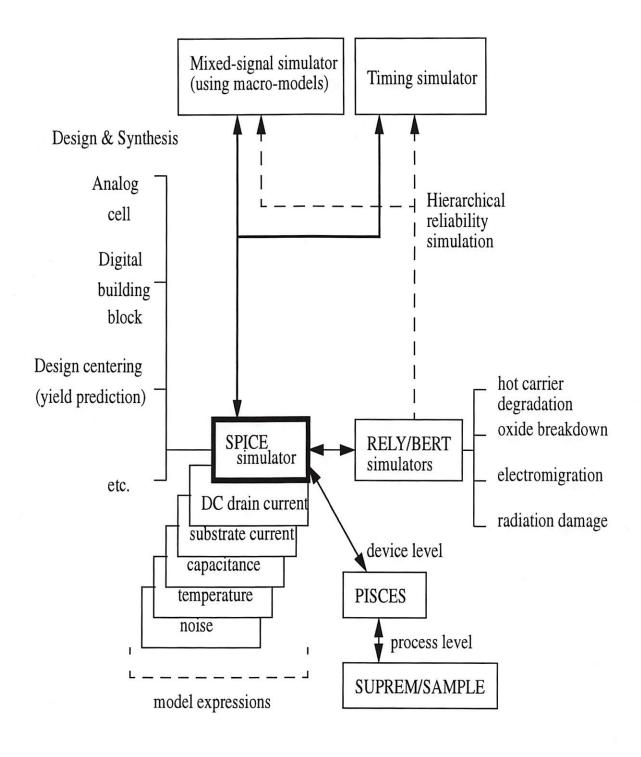

|    | 1.2  | Mixed-Signal V  | LSI Design Env   | vironme | ent .  |           |     |      | ٠  |   |     |    |   | 4               |

| 2  | MO   | S Transistor M  | Iodeling for (   | Circuit | Sim    | ulati     | on  |      |    |   |     |    |   | 12              |

|    | 2.1  | First-Generatio | n MOS Transis    | tor Mo  | dels . |           |     |      |    |   |     |    |   | 15              |

|    |      | 2.1.1 The Lev   | el-1 Model       |         |        |           |     |      | •  |   |     |    |   | 15              |

|    |      | 2.1.2 The Lev   | rel-2 Model      |         |        |           |     |      |    |   |     |    |   | 15              |

|    |      | 2.1.3 The Lev   | el-3 Model       |         |        | 100 300 0 |     |      |    |   |     |    |   | 16              |

|    | 2.2  | The Second-Ger  |                  |         |        |           |     |      |    |   |     |    |   | 18              |

|    |      | 2.2.1 The BSI   | M Model          |         |        |           |     |      |    |   |     |    |   | 18              |

|    |      |                 | Level-28 Mode    |         |        |           |     |      |    |   |     |    |   | 20              |

|    |      | 2.2.3 The BSI   | M2 Model         |         |        |           |     |      |    |   |     |    |   | 21              |

|    | 2.3  | The Third-Gene  |                  |         |        |           |     |      |    |   |     |    |   | 22              |

|    |      |                 | M3 Model         |         |        |           |     |      |    |   |     |    |   | 22              |

|    |      |                 | S Model-9        |         |        |           |     |      |    |   |     |    |   | 24              |

|    |      |                 | V Model          |         |        |           |     |      |    |   |     |    |   | $\overline{24}$ |

|    | 2.4  | Table Look-up   |                  |         |        |           |     |      |    |   |     |    |   | 25              |

|    | 2.5  | Future Needs    |                  |         |        |           |     |      |    |   |     |    |   | 26              |

| 3  | The  | Unified Short   | -Channel MC      | )S (S-0 | смо    | S) T      | ran | sist | or | М | ode | [د |   | 33              |

| _  | 3.1  | Drain Current 1 |                  |         |        | ,         |     |      |    |   |     |    |   | 35              |

|    | 0.1  |                 | ld Voltage       |         |        |           |     |      |    |   |     |    |   | 38              |

|    |      |                 | Mobility         |         |        |           |     |      |    |   |     |    |   | 41              |

|    |      |                 | nversion Curren  |         |        |           |     |      |    |   |     |    |   | 43              |

|    |      |                 | -Length Modul    |         |        |           |     |      |    |   |     |    |   | 46              |

|    |      |                 | version Region   |         |        |           |     |      |    |   |     |    |   | 47              |

|    |      | 3.1.6 Unified   | Drain Current    | Express | ion    | • •       |     | ٠.   | •  | • |     |    | • | 48              |

|    | 3.2  | Experimental R  |                  |         |        |           |     |      |    |   |     |    |   | 50              |

|    | 3.3  | Unified Charge  |                  |         |        |           |     |      |    |   |     |    |   | 62              |

|    | 0.0  | Chilled Charge  | Capacitatice IV. | iouci . |        |           |     |      |    |   |     |    |   | UZ              |

|                           |      | 3.3.1   | The Charge Model                                                  |

|---------------------------|------|---------|-------------------------------------------------------------------|

|                           |      | 3.3.2   | Channel-Charge Partitioning Methods: 40/60, 0/100, 50/50 . 67     |

|                           |      | 3.3.3   | The Capacitance Model                                             |

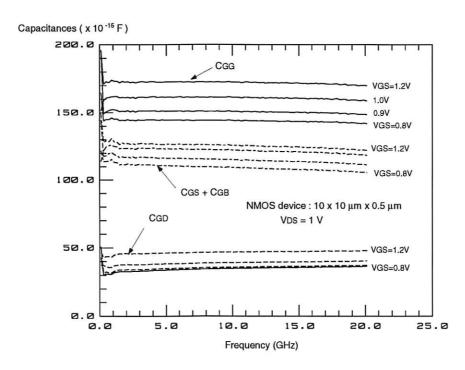

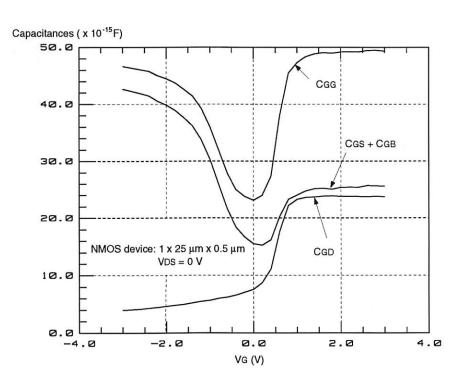

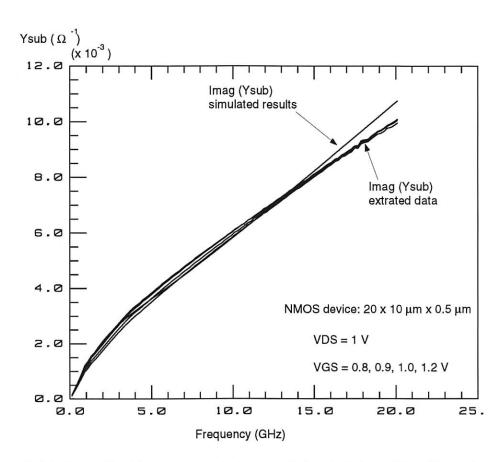

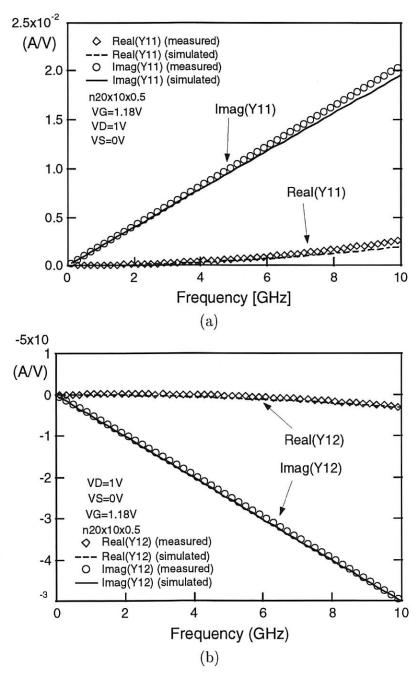

|                           | 3.4  | Exper   | imental Results of Charge/Capacitance Model 69                    |

| 4                         | Par  | ameter  | Extraction 80                                                     |

|                           | 4.1  | Prope   | rties of Parameters of The S-CMOS Model                           |

|                           |      | 4.1.1   | Primary Physical Parameters 81                                    |

|                           |      | 4.1.2   | The Fitting Parameters                                            |

|                           |      | 4.1.3   | The Smooth-Function Parameters                                    |

|                           | 4.2  | Extra   | etion Strategy                                                    |

|                           |      | 4.2.1   | Optimization Method                                               |

|                           |      | 4.2.2   | Geometric Space                                                   |

|                           | 4.3  | The E   | fficient DC Parameter Extraction for S-CMOS 87                    |

|                           |      | 4.3.1   | The Parameter Extraction Procedure 87                             |

|                           |      | 4.3.2   | S-CMOS Model Extractor in MATLAB                                  |

| 5                         | Imp  | lemen   | tation in SPICE-3f3 Circuit Simulator 99                          |

|                           | 5.1  | SPICE   | E-3f3s implementation of S-CMOS model                             |

|                           | 5.2  | Simula  | ation Results of Selected Circuits Using S-CMOS Model 104         |

|                           |      | 5.2.1   | Charge Conservation Property                                      |

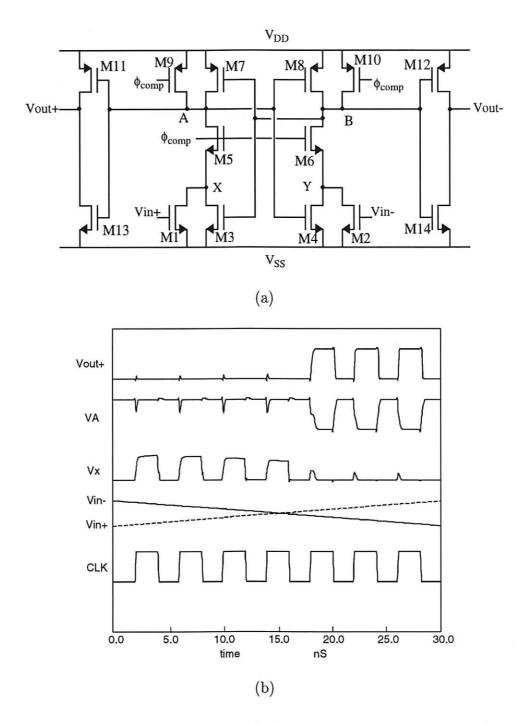

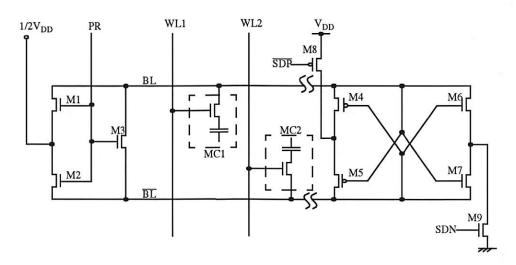

|                           |      | 5.2.2   | Domino Logic Gate                                                 |

|                           |      | 5.2.3   | Folded-Cascode Operational Amplifier                              |

|                           |      | 5.2.4   | Analog Comparator                                                 |

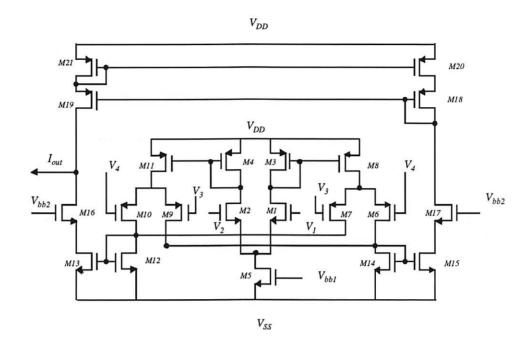

|                           |      | 5.2.5   | Wide-Range Gilbert Multiplier                                     |

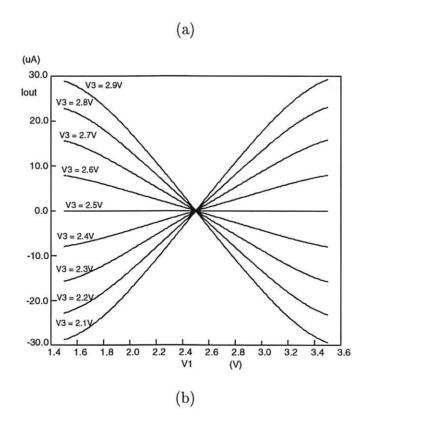

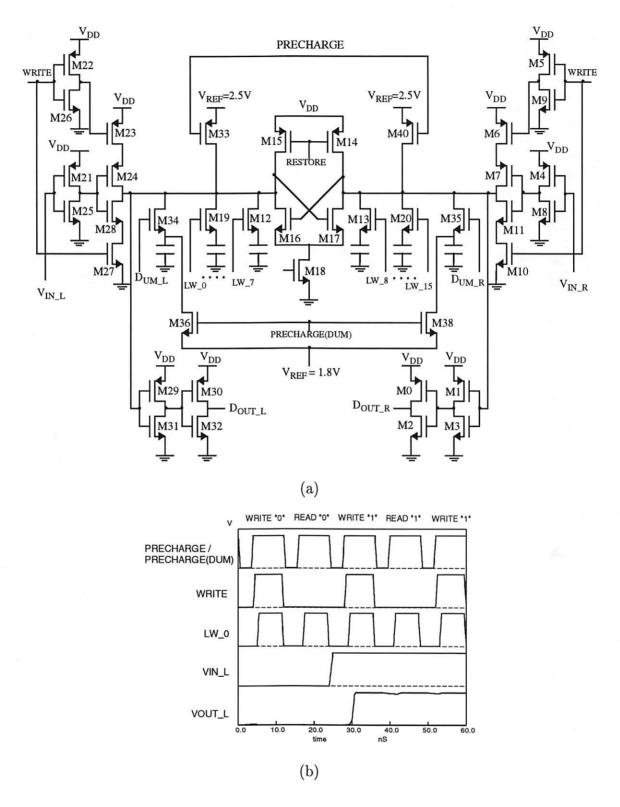

|                           |      | 5.2.6   | DRAM Memory Circuit                                               |

| 6                         | Disc | cussion | and Conclusion 118                                                |

| Aı                        | pen  | dix A   |                                                                   |

|                           | List | of Mod  | el Equations                                                      |

|                           | A.1  | DC M    | odel                                                              |

|                           | A.2  |         | ctances                                                           |

|                           | A.3  | Charg   | e/Capacitance Model                                               |

| $\mathbf{A}_{\mathbf{I}}$ | ppen | dix B   |                                                                   |

|                           | RF I | MOS T   | cansistor Modeling and Parameter Extraction Valid up to 10-GHz130 |

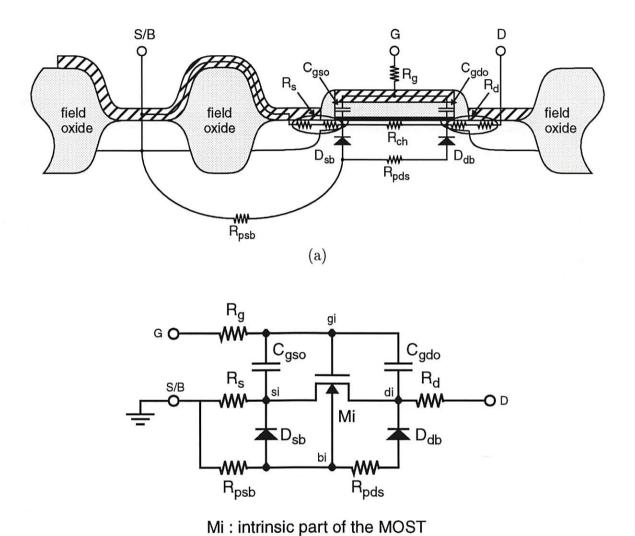

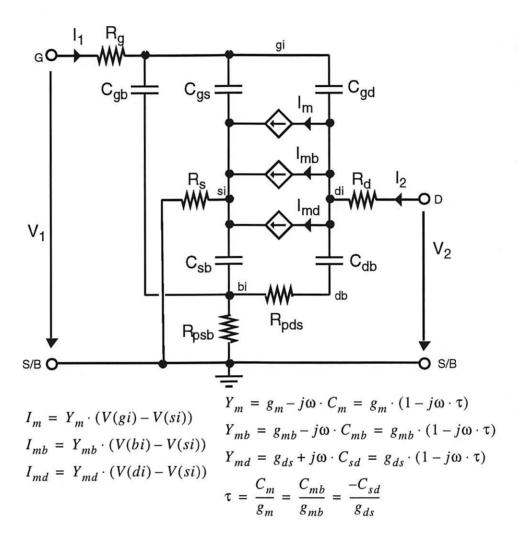

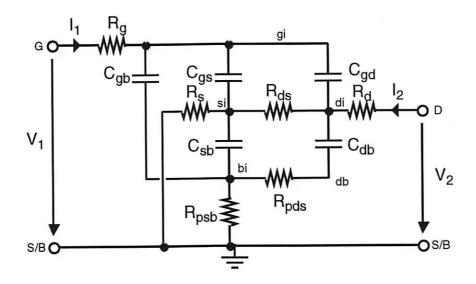

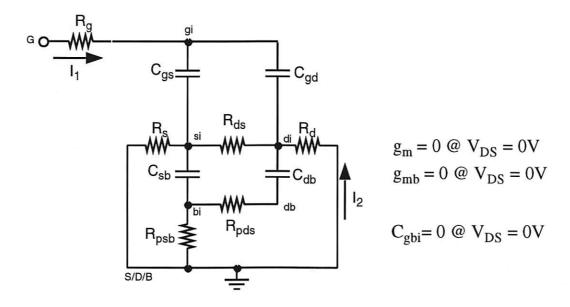

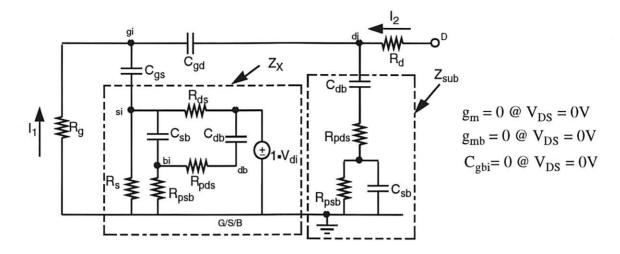

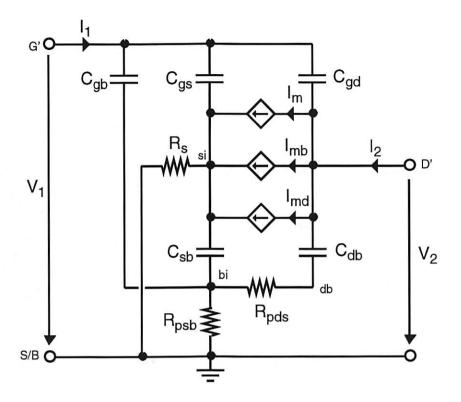

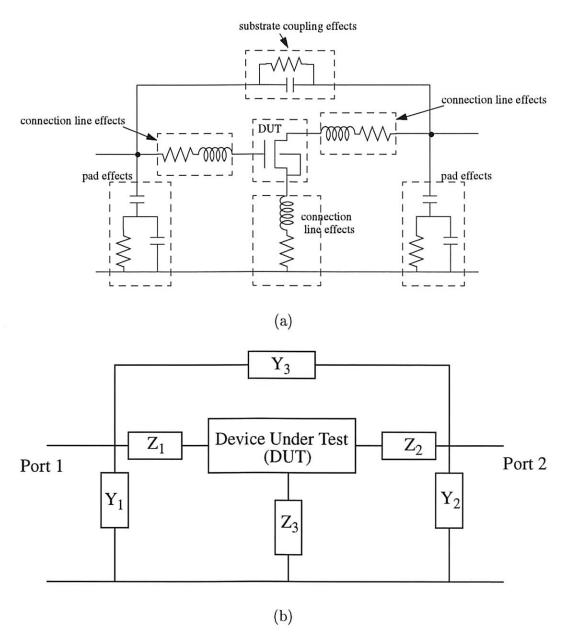

|                           | B.1  |         | Signal Equivalent Circuit of MOS Transistors at RF 132            |

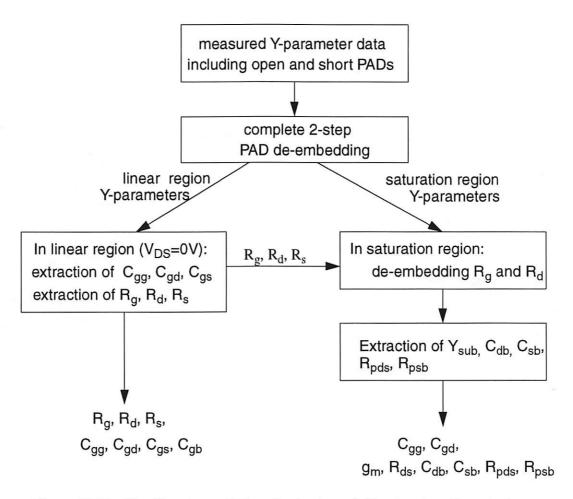

|                           | B.2  | Y-Par   | ameter Analysis of The Two-Port MOS Transistor in Triode          |

|                           |      |         | 1                                                                 |

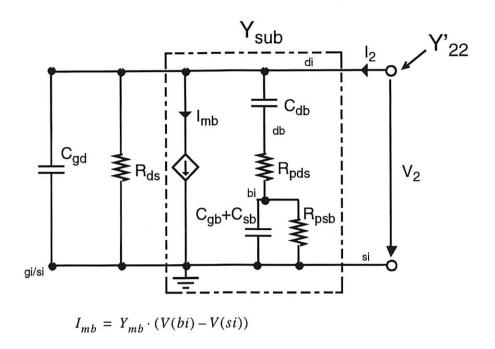

|                           | B.3  | Y-Par   | ameter Analysis of The Two-Port MOS Transistor in Saturation      |

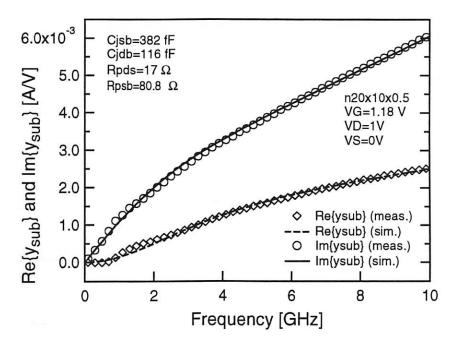

|                           |      |         | n                                                                 |

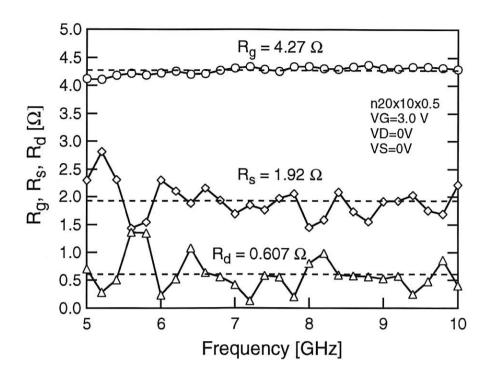

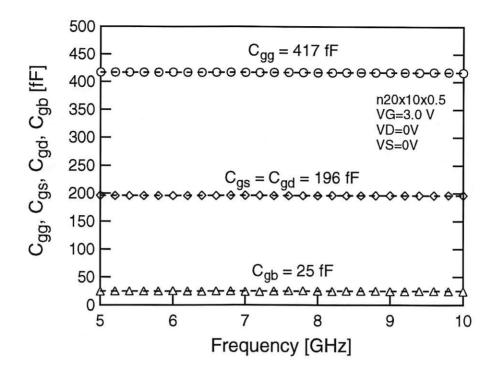

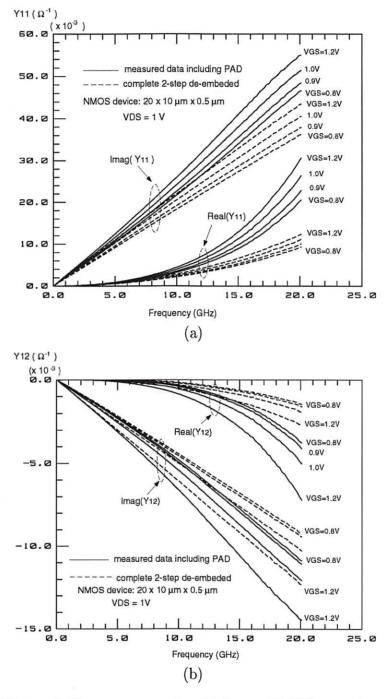

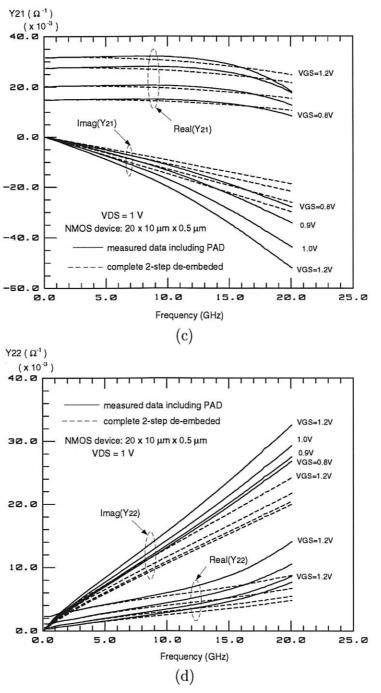

|                           | B.4  | Experi  | mental Results and Discussion                                     |

| Appendix C                                            |                                                       |    |     |   |     |                |                |   |   |   |    |  |     |

|-------------------------------------------------------|-------------------------------------------------------|----|-----|---|-----|----------------|----------------|---|---|---|----|--|-----|

| High                                                  | n-Frequency MOS Transistor S-Parameter Measure        | me | ent | a | no  | 1]             | PA             | I | ) | D | e- |  |     |

|                                                       | embedding                                             |    |     |   |     |                |                |   |   |   |    |  | 160 |

| C.1                                                   | Test Equipment and Testing Structure                  |    |     |   |     | •              | •              | ě |   |   |    |  | 160 |

| C.2                                                   | Testing Procedure                                     |    |     |   |     |                |                |   |   |   |    |  | 161 |

| C.3                                                   | Complete Two-Step PAD De-embedding                    |    |     |   |     |                |                |   |   |   |    |  | 162 |

| Appendix D S-CMOS Model Parameter Extraction Programs |                                                       |    |     |   | 170 |                |                |   |   |   |    |  |     |

| Appendix E SPICE Input Files of The Select Circuits   |                                                       |    |     |   |     |                |                |   |   |   |    |  |     |

| Appen<br>List                                         | dix F of Publications Achieved from Dissertation Work | •  |     |   |     | 3. <b>•</b> // | 3 <b>•</b> 3 € |   |   |   | 1. |  | 196 |

## List Of Tables

| 2.1 | Comparison between Level-2, BSIM, BSIM3v3 and S-CMOS models. 29                                                                                          |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1 | Device parameters and their typical values of S-CMOS model for a 0.5 $\mu m$ technology                                                                  |

| 4.1 | S-CMOS model parameters for a 0.5 $\mu m$ technology. (a) Primary physical parameters. (b) Secondary physical parameters. (c) Smooth function parameters |

| 5.1 | Performance of the folded-cascode operational amplifier                                                                                                  |

| 6.1 | The advanced features of the S-CMOS model                                                                                                                |

| C.1 | An example of the input controlling variables of HP-8510 network analyzer for MOS transistor S-parameter measurement 168                                 |

## List Of Figures

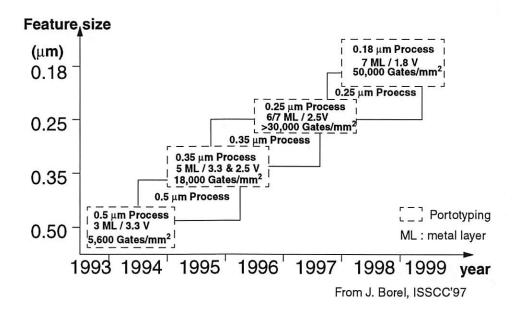

| The advanced VLSI CMOS technologies trend [4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

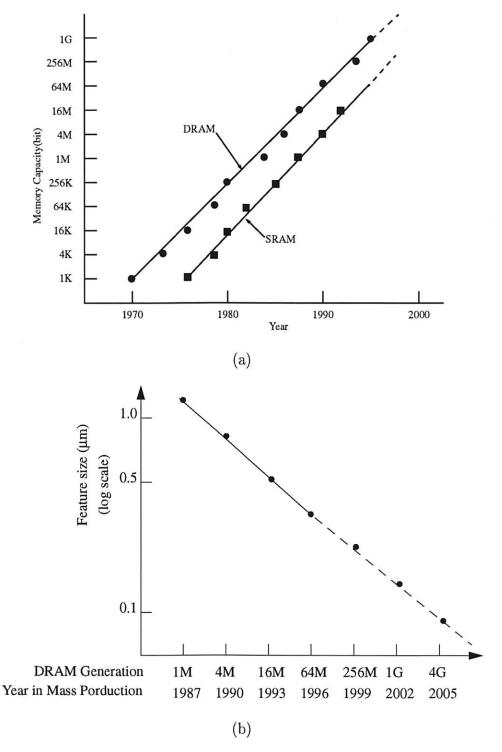

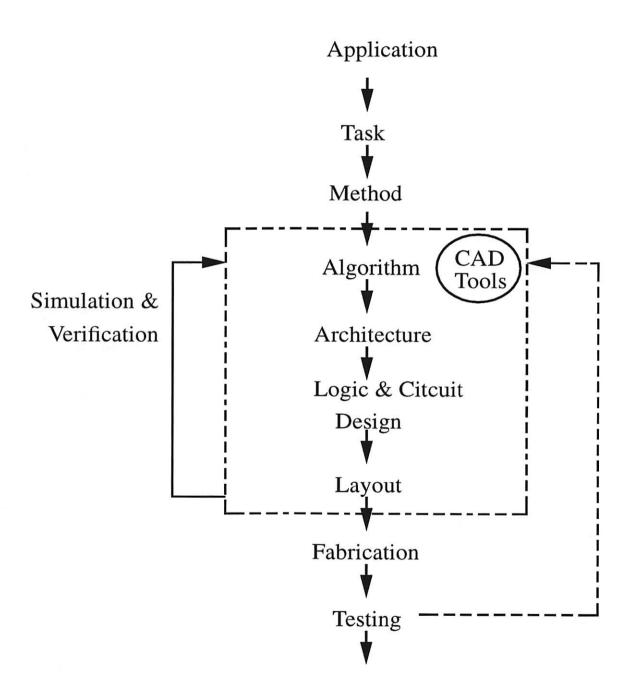

| CMOS memories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3<br>5                                                                         |

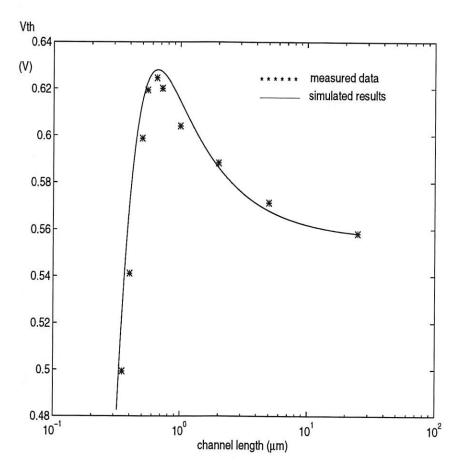

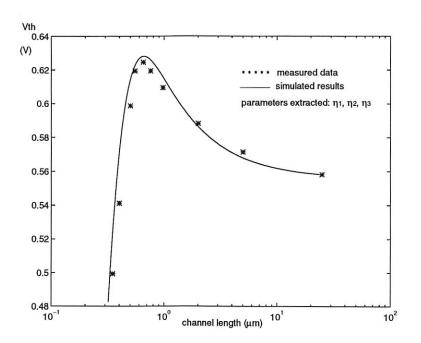

| Plot of the measured and modeled threshold voltage versus channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                |

| length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40                                                                             |

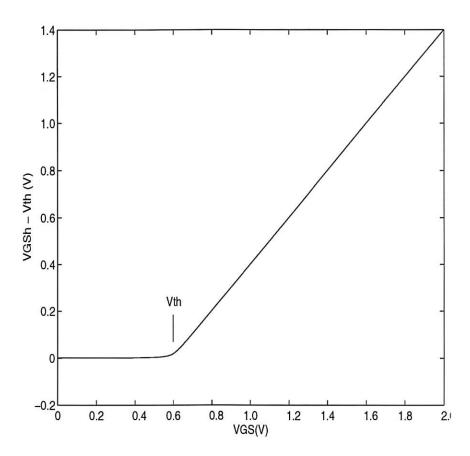

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 41                                                                             |

| zero in weak-inversion region                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43                                                                             |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45                                                                             |

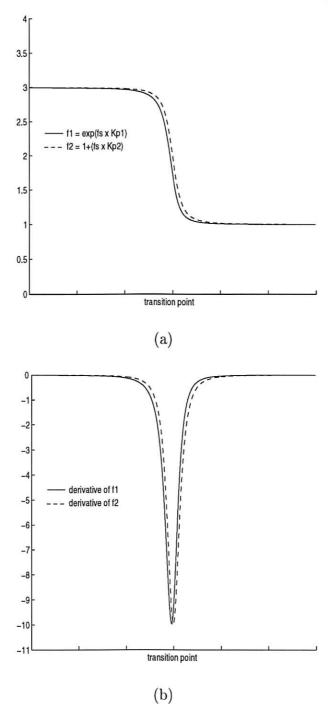

| The sigmoid function, $f_s$ , used for smoothing the drain current equa-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                |

| ğ ğ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 49                                                                             |

| parameters $K_{p1} = 1.1$ and $K_{p2} = 2$ . (a) Functions, $f1$ and $f2$ . (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                |

| 1 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53                                                                             |

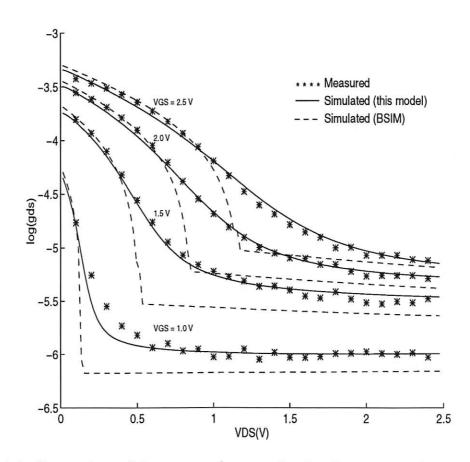

| Comparison of the measured versus simulated output conductance values of a short-channel ( $L=0.3~\mu m$ ) NMOS transistor. The pro-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |

| posed model accurately simulates the output conductance character-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                |

| The second secon | 54                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                |

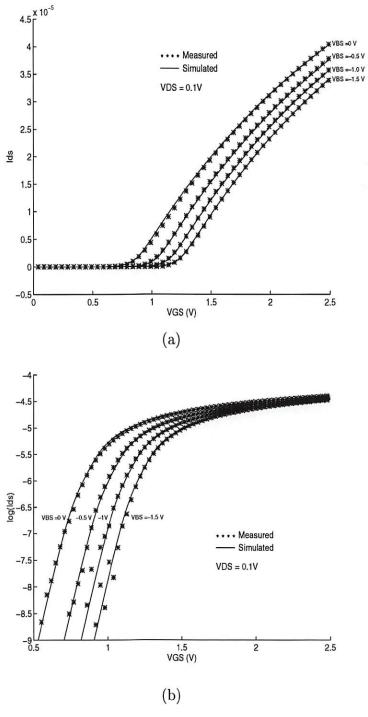

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                |

| model. (a) On a logarithmic scale. (b) On a linear scale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 56                                                                             |

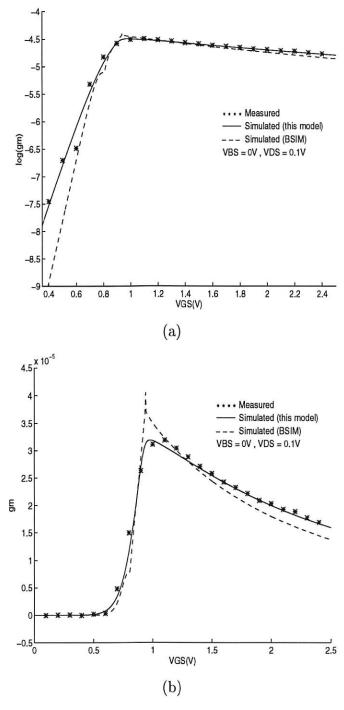

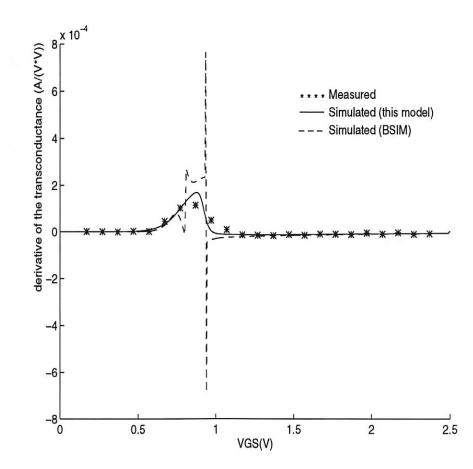

| Comparison of the derivative of transconductances with respect to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                |

| $V_{GS}$ for both the BSIM and the proposed S-CMOS model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Advances in fabrication technologies used for mass-production of CMOS memories |

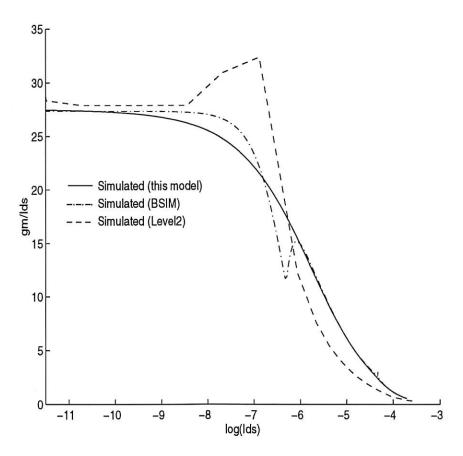

| 3.12  | $g_m/I_{DS}$ versus $I_{DS}$ plot for the benchmark test suggested by Tsividis                                                               |     |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

|       | and Suyama [1]. The result of the proposed model shows smooth                                                                                | 50  |

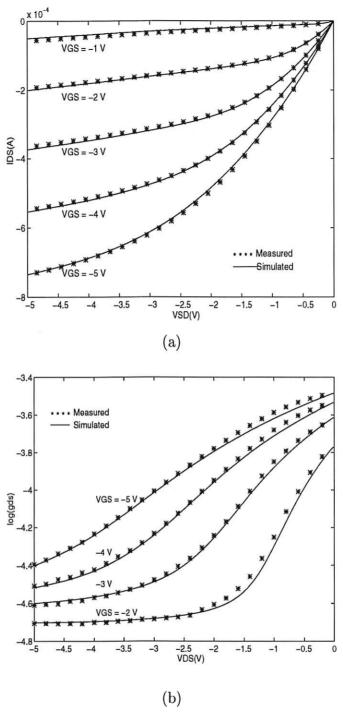

| 2 1 2 | behavior for the curve from weak- to strong-inversion regions Plots of $I_{DS}$ versus $V_{DS}$ characteristics of a long-channel PMOS tran- | 58  |

| 5.15  | sistor with $W=1.75~\mu m$ and $L=25~\mu m$                                                                                                  | 59  |

| 3 14  | Plots of DC characteristics of a short-channel PMOS transistor with                                                                          | 00  |

| 0.14  | $W=1~\mu m$ and $L=0.24~\mu m$ . (a) $I_{DS}$ versus $V_{DS}$ . (b) $g_{ds}$ versus $V_{DS}$ .                                               | 60  |

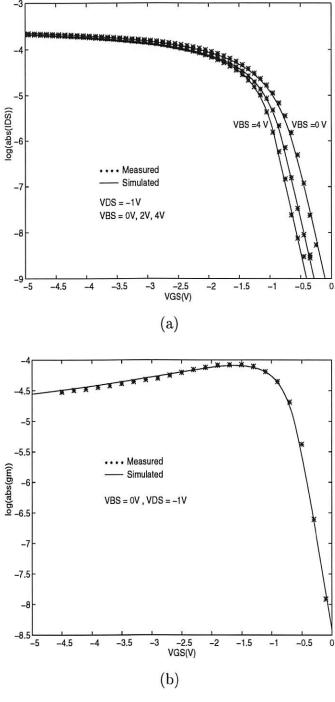

| 3 15  | Plots of DC characteristics of a short-channel PMOS transistor with                                                                          | 00  |

| 0.10  | $W=1~\mu m$ and $L=0.24~\mu m$ . (a) $I_{DS}$ versus $V_{GS}$ . (b) $g_m$ versus $V_{GS}$ .                                                  | 61  |

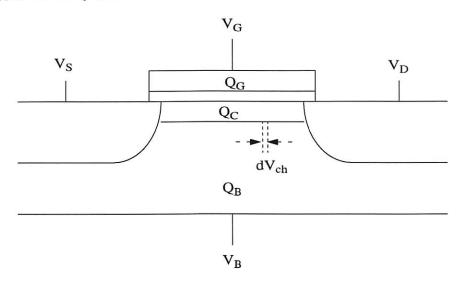

| 3 16  | The cross section of an NMOS transistor to illustrate the space charge.                                                                      | 63  |

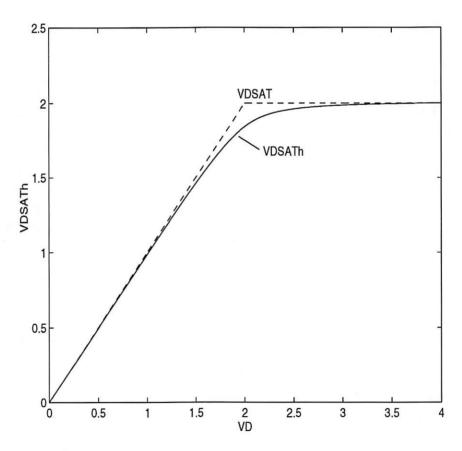

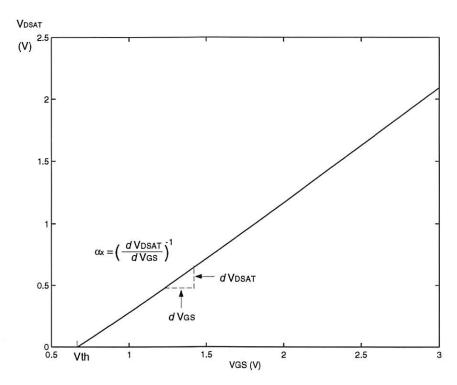

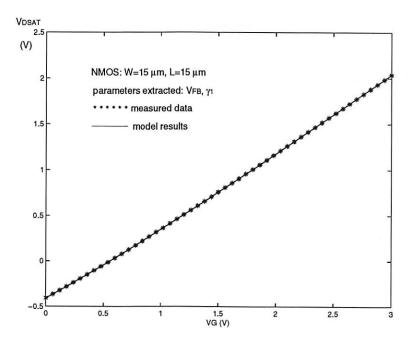

|       | The characteristics of the saturation voltage, $V_{DSAT}$ , with respect to                                                                  | 00  |

| J.1.  | the gate voltage, $V_{GS}$                                                                                                                   | 64  |

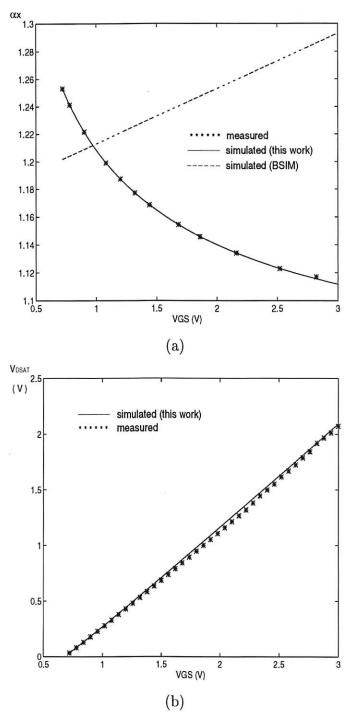

| 3.18  | Plots of the back gate degradation coefficient, $\alpha_x$ , and saturation volt-                                                            | 0 1 |

|       | age, $V_{DSAT}$ . (A) $\alpha_x$ vs. $V_{GS}$ . (B) $V_{DSAT}$ vs. $V_{GS}$                                                                  | 70  |

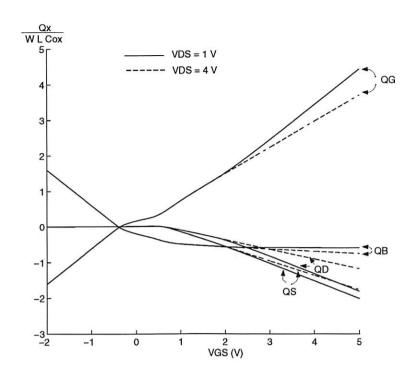

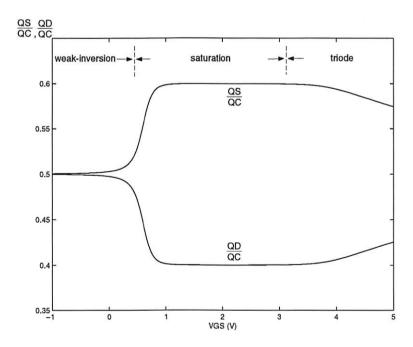

| 3.19  | Normalized terminal charges versus gate bias for two drain voltages                                                                          |     |

|       | with $V_{BS} = 0V$                                                                                                                           | 71  |

| 3.20  | Plots of drain and source charges in different operation regions. The                                                                        |     |

|       | ratio of drain charge to source charges is 40/60 in the saturation region.                                                                   | 71  |

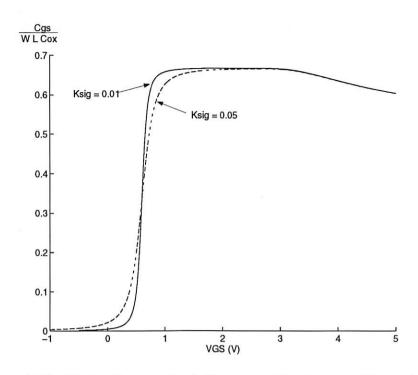

| 3.21  | Plots of normalized $C_{gs}$ versus $V_{GS}$ for two $K_{sig}$ values                                                                        | 72  |

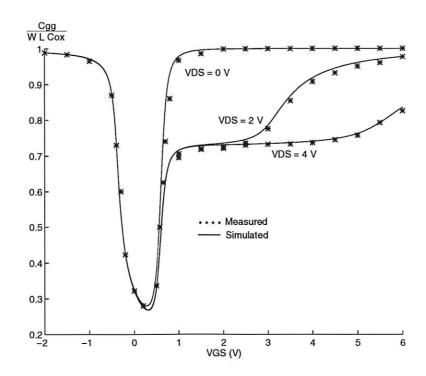

|       | Normalized gate capacitance, $C_{gg}$ , versus gate bias from accumulation                                                                   |     |

|       | to strong-inversion regions with $V_{BS} = 0V$ for an MOS transistor of                                                                      |     |

|       | $W/L = 100 \ \mu m/0.8 \ \mu m. \dots$                                                                                                       | 73  |

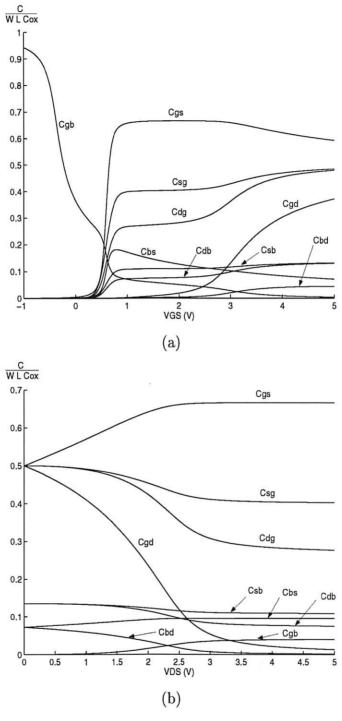

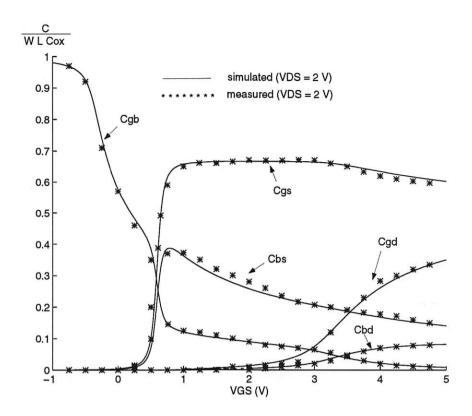

| 3.23  | Plots of nine normalized capacitances. (A) Capacitances versus $V_{GS}$                                                                      |     |

|       | with $V_{DS} = 2 V$ and $V_{BS} = 0 V$ . (B) Capacitances versus $V_{DS}$ with                                                               |     |

|       | $V_{GS} = 3.5 V$ and $V_{BS} = 0 V \dots \dots \dots \dots \dots \dots \dots \dots$                                                          | 74  |

| 3.24  | Plots of normalized capacitances versus $V_{GS}$ of an NMOS transistor                                                                       |     |

|       | of W/L = 25 $\mu m/0.35 \ \mu m$ for two $V_{DS}$ values                                                                                     | 75  |

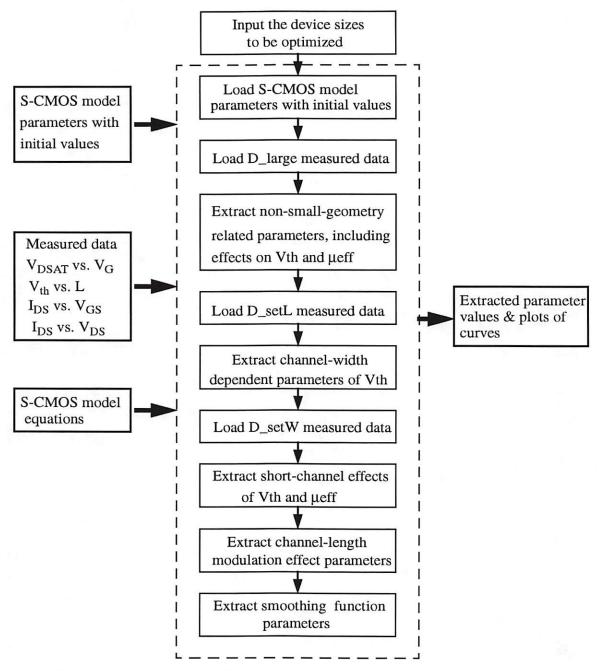

| 4.1   | The flowchart of the S-CMOS model parameter extraction                                                                                       | 90  |

| 4.2   | Plot of reverse short-channel effect for extracting the parameter,                                                                           | 90  |

| 1.2   | $\eta_1, \eta_2, \text{ and } \eta_3. \dots \dots$                               | 92  |

| 4.3   | Plot of $V_{DSAT}$ versus $V_G$ to optimize $\alpha_x$ and $V_{DSAT}$ for extracting $V_{FB}$ ,                                              | 02  |

|       | $\gamma_1$ , and $\phi_s = V_{T0} - V_{FB}$ with a long- and wide-channel transistor to                                                      |     |

|       | exclude the short- and narrow-channel effects                                                                                                | 92  |

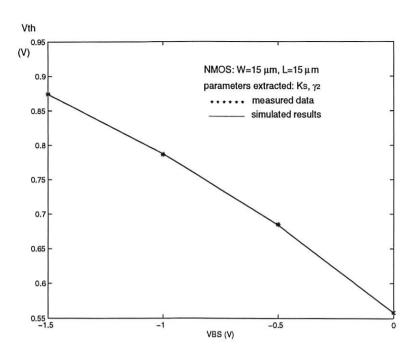

| 4.4   | Plot of $V_{th}$ versus $V_{BS}$ of a large transistor to extract the higher-order                                                           |     |

|       | body effect parameters, $K_S$ and $\gamma_2$                                                                                                 | 93  |

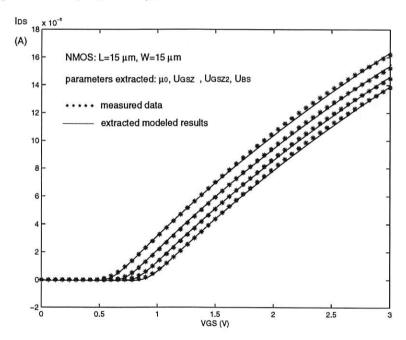

| 4.5   | Plots of $I_{DS}$ versus $V_{GS}$ of a large transistor at $V_{DS} = 0.05 V$ and                                                             |     |

|       | $V_{BS} = 0, -0.5, -1, -1.5 V$ to exclude the small-geometry effects and                                                                     |     |

|       | $V_{DS}$ effects for extracting $\mu_0, U_{GSZ}$ , and $U_{BS}$                                                                              | 93  |

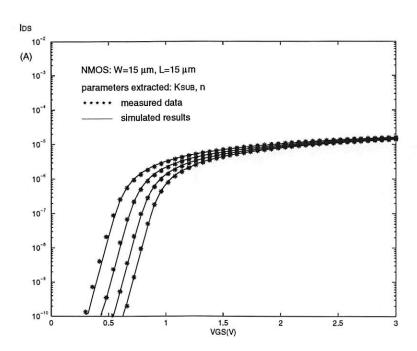

| 4.6   | Plots of $I_{DS}$ versus $V_{GS}$ in the logarithmic scale for extracting the                                                                |     |

|       | weak-inversion region parameters, $K_{sub}$ and $n$                                                                                          | 94  |

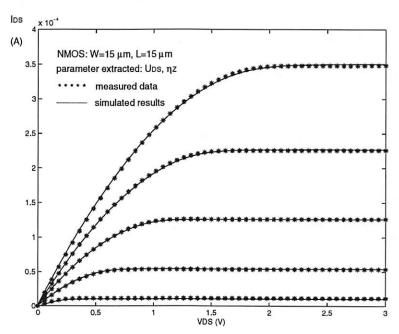

| 1.7   | Plots of $I_{DS}$ versus $V_{DS}$ at $V_{GS} = 1, 1.5, 2, 2.5, 3 V$ of a large transistor                                                    |     |

|       | for extracting $U_{DS}$ and $\eta_Z$                                                                                                         | 94  |

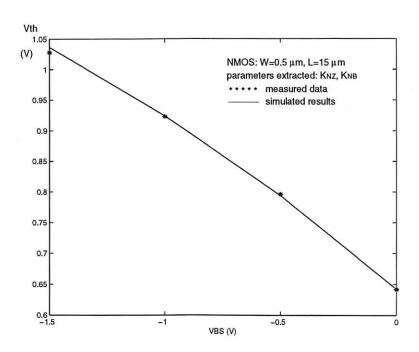

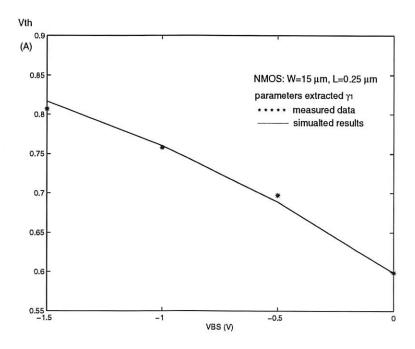

| 4.8<br>4.9<br>4.10 | Plot of $V_{th}$ versus $V_{BS}$ of a narrow-channel transistor for extracting $K_{NZ}$ and $K_{NB}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 95<br>95                          |

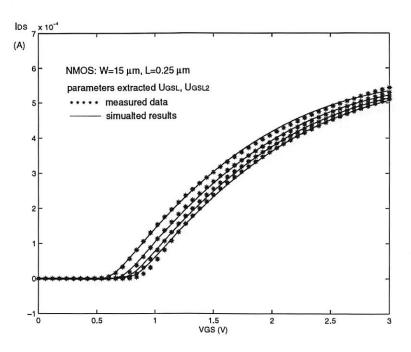

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

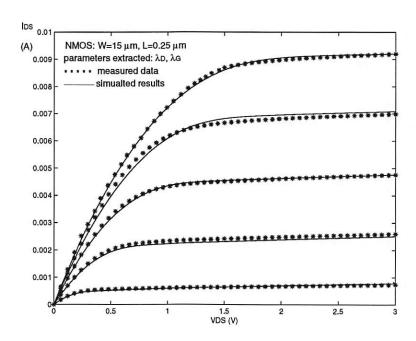

| 4.11               | $U_{GSL}$ and $U_{GSL2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 96<br>96                          |

| 4.12               | The state of the s | 97                                |

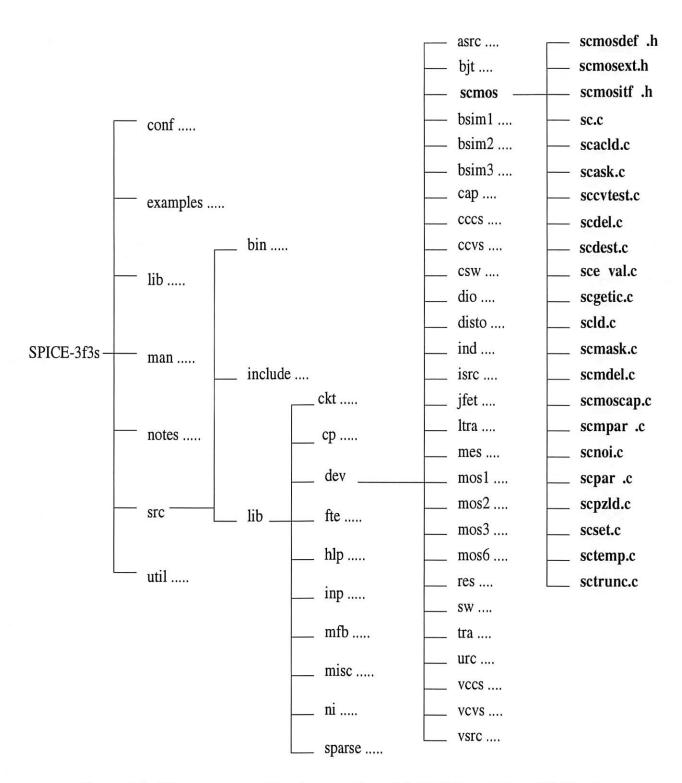

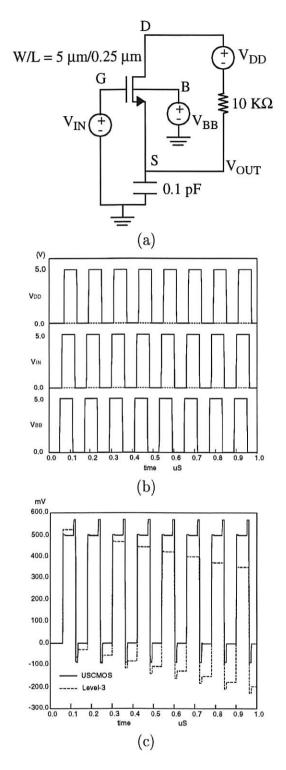

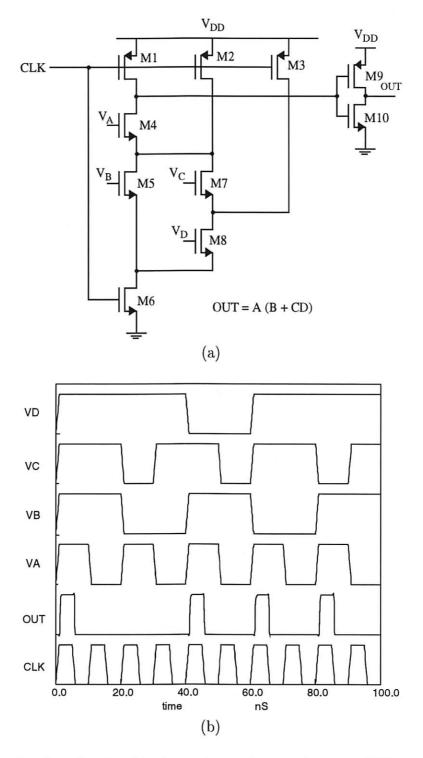

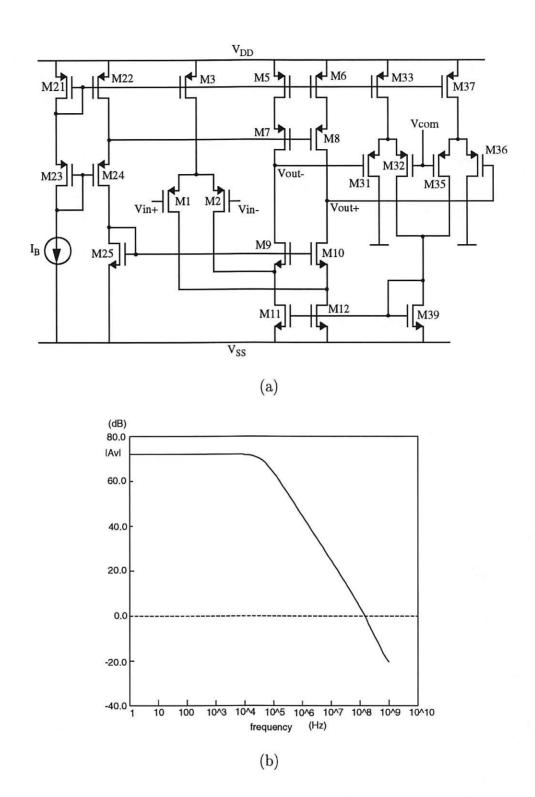

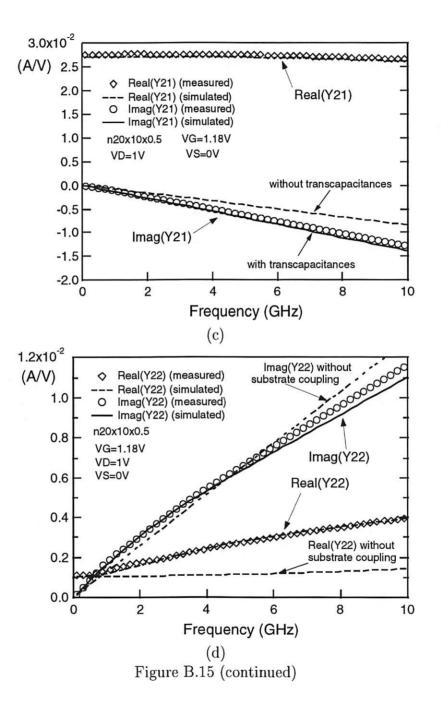

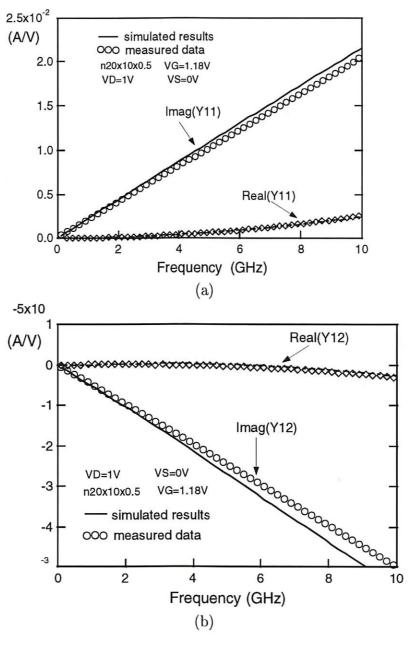

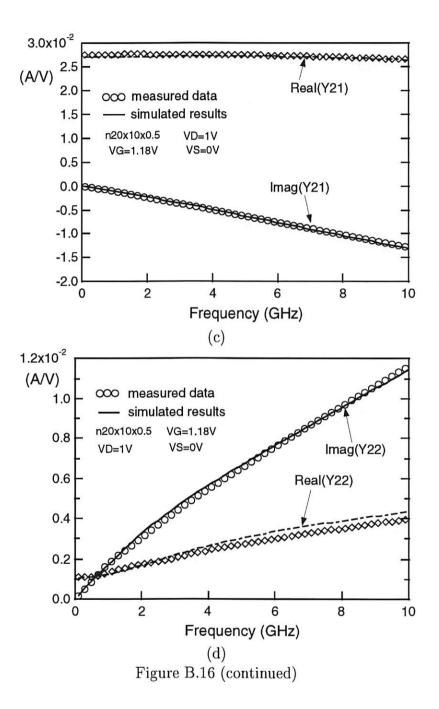

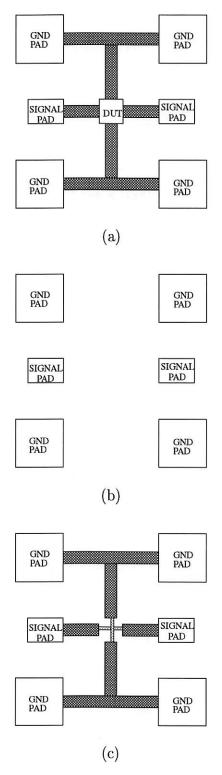

| 5.1<br>5.2         | The structure of implementation of S-CMOS model in SPICE-3f3 Charge conservation test of S-CMOS model. (a) Test circuit. (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 101                               |