### **USC-SIPI REPORT #331**

S-CMOS: A Robust Deep-Submicron CMOS Transistor Model For Very Low-Power High-Frequency VLSI Application

by

Yoondong Park April 1999

Signal and Image Processing Institute UNIVERSITY OF SOUTHERN CALIFORNIA

Department of Electrical Engineering-Systems 3740 McClintock Avenue, Room 400 Los Angeles, CA 90089-2564 U.S.A.

### Acknowledgments

I would like to express my sincerest thanks to my research advisor, Professor Bing J. Sheu, Department of Electrical Engineering and with joint appointment at Department of Biomedical Engineering, for his guidance, encouragement, support and smart words throughout these years of my Ph.D. research. I wish to extend my sincere appreciation to Professor Hans Kuehl, the chairman of my dissertation committee, Department of Electrical Engineering, Professor John Choma, Department of Electrical Engineering, and Professor Michael Khoo, Department of Biomedical Engineering, for serving on my dissertation committee. I would also like to thank them along with Professor Jim Liaw, Department of Biomedical Engineering, Dr. Wei-Chi Fang, JPL(Jet Population Lab.), NASA, for serving on my qualifying examination committee.

I am very grateful to Professor Theodore Berger, Department of Biomedical Engineering, Professor Leonard M. Silverman, Dean of the Engineering School; Professor Martin Gurndersun, Chairman of the Electrical Engineering-Electrophysics Department; Professor Robert A. Scholtz, Chairman of the Electrical Engineering-Systems Department; Professor Chrysostomos (Max) L. Nikias, Director of Integrated Media Systems Center, which is an Engineering Research Center of National Science Foundation, Ms. Ramona Gordon, Ms. Anna Fong, in the Electrical Engineering

Program, for providing such a great research environment for my Ph.D. study at the University of Southern California. This research work conducted through connection with several research organizations within USC including Integrated Media Systems Center (IMSC), Center for Neural Engineering (CNE), Signal and Image Processing Institute (SIPI), and Information Sciences Institute (ISI, MOSIS).

Valuable industrial support for this research was made possible through Dr. Glenn Perry, Ananogy Co., Bob Daniels, Avanti! Corp., Peter Bendix, LSI Logic Corp., Richard Trihy, Cadence, Klaassen, Philips Research Lab., Marek Mierzwinski, HP Co., Don Scharfetter/Ling-Chu, Intel Corp., Michel Matloubian, Rockwell International, Vance Tyree, MOSIS, Patti Rusher, EIA (Electronic Industry Alliance), and other prominent researchers in San Francisco Bay area.

Valuable discussions with graduate doctoral colleagues from VLSI Multimedia Laboratory were truly stimulating, including Dr. Steve Jen, Dr. Eric Y. Chou (now Member of Technical Staff at HP Communication Semiconductor Solutions Division, San Jose, CA), Dr. David C. Chen (now Marketing Specialist at United Semiconductor Corp., Taiwan). Many thanks to Austin K. Cho, Richard H. Tsai, Michelle Y. Wang, Wayne, C. Young, Suat U. Ay, John S. Lee, James J. Cho, Vivian H. Yoon, and Jim C. Tai, for friendly interaction.

I am very grateful to Dae-jung Kim, President of Korea, Dr. Hong-Keon Choi, Administer of the Ministry of Commerce, Industry and Energy(MOCIE), June-Suk Choo, Administer of the Small and Medium Business Administration(SMBA), Teok-Young Joo, General Director, Kee-Joong Chang, Deputy Director of National Institute of Technology & Quality, Kwan-Joong Kim, Director, in National Institute of Technology

& Quality(NITQ) and many other Korean Government officials especially in MOGAHA, SMBA and NITQ with their valuable support for my research in USC with a Korean Government Long-Term fellowship for four years.

I would like to express my whole-hearted thanks to my past father, Kwon-Sik Park, my father-in-law, Min-Seup Yoon, mother-in-law, Young-Hee Lee, my elder sister, Seol-Hee Park, younger brother Yoon-Ho Park, past younger sister Sang-Hee Park, younger brother Yoon-Seok Park, and elder brother-in-law Hee-Ro Yoon, elder sister-in-law Heui-Joo Yoon for their love and precious support throughout all these years in my study in USA.

At last, I would like to express my deepest appreciation towards forever friend, my lovely wife, Heesook Yoon, the entire part of my life, my lovely daughter, Nicola Park, my forever strong supporter, my mother Bo-Kie Eun who offer warm love and great patiences.

## **Contents**

| Acknowledgment                                   | ii   |

|--------------------------------------------------|------|

| List of Figures                                  | ix   |

| List of Tables                                   | xiii |

| Abstract                                         | xiv  |

| Chapter 1. Introduction                          | 1    |

| Chapter 2. MOS Transistor Modeling               | 12   |

| 2.1 Overview                                     | 12   |

| 2.2 MOS Transistor Models                        | 16   |

| 2.2.1 The First-Generation MOS Transistor Models | 16   |

| 2.2.1.1 The Level-1 Model                        | 16   |

| 2.2.1.2 The Level-2 Model                        | 16   |

| 2.2.1.3 The Level-3 Model                        | 17   |

| 2.2.2 The Second-Generation MOS Transistor Model | 20   |

| 2.2.2.1 The BSIM Model                           | 20   |

| 2.2.2.2 The HSICE Level-28 Model                 | 22   |

| 2.2.2.3 The BSIM2 Model                          | 23   |

| 2.2.3 The Third -Generation Models               | 24   |

| 2.2.3.1 The BSIM3 Model                          | 25   |

| 2.2.3.2 The Model-9                              | 26   |

| 2.2.3.3 The EKV Model                            | 27   |

| 2.2.4 Future Needs                               | 28   |

| Chapter 3 DC Expression for S-CMOS Model.            | 34 |

|------------------------------------------------------|----|

| 3.1 Threshold Voltage                                | 35 |

| 3.1.1 Standard Expression                            | 36 |

| 3.1.2 Non-Uniform Doping Effect                      | 37 |

| 3.1.3 Drain-Induced Barrier Lowering (DIBL)          | 38 |

| 3.1.4 Narrow Channel Effect                          | 38 |

| 3.1.5 Short Channel Effect                           | 39 |

| 3.1.6 Temperature dependency                         | 41 |

| 3.2 Mobility Model                                   | 44 |

| 3.3.1 Effective Mobility                             | 44 |

| 3.2.2 Unified Expression.                            | 46 |

| 3.2.3 Temperature dependency                         | 47 |

| 3.3 Channel Length Modulation (CLM) Effect           | 49 |

| 3.4 Parasitic Resistances.                           | 50 |

| 3.5 Noise Effects                                    | 53 |

| 3.5.1 Thermal noise effect                           | 53 |

| 3.5.2 Fliker noise effects                           | 54 |

| 3.5.3 Shot noise                                     | 55 |

| 3.5.3 Noise source                                   | 57 |

| 3.6 Unified DC Current Model                         | 57 |

| 3.6.1 Strong-Inversion Current                       | 57 |

| 3.6.2 Sub-threshold Drain Current                    | 59 |

| 3.6.3 Exponential interpolation Function             | 60 |

| 3.6.4 Unified DC MOS Model Drain current Expression  | 62 |

| 3.7 Simulation and Experimental Results for DC Model | 63 |

| Chapter 4 Charge/Capacitance Model                   | 73 |

| 4.1 Charge Model                                      | 73   |

|-------------------------------------------------------|------|

| 4.1.1 Terminal Charge Expression                      | . 73 |

| 4.1.2 transition from linear to saturation region     | 73   |

| 4.2 Channel Charge Partitioning Methods               | 74   |

| 4.2.1 The 40/60 Channel-charge Partition              | 79   |

| 4.2.2 The 0/100 Channel Charge partition              | 79   |

| 4.2.3 The 50/50 Channel Charge partition              | 81   |

| 4.3 Capacitance Model                                 | 82   |

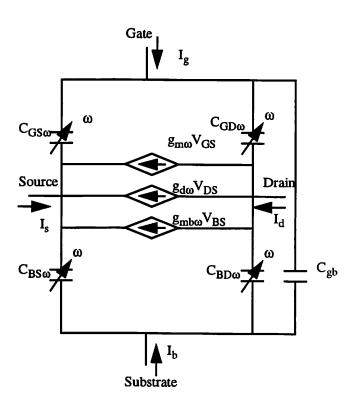

| 4.4 Small signal circuit                              | 89   |

| 4.5 Non-Quasi Static Model                            | 91   |

| 4.6 Experimental Results for Charge/Capacitance Model | 102  |

| Chapter 5 S-CMOS Model Parameter Extraction           | 109  |

| 5.1 Parameter classification.                         | 110  |

| 5.1.1 Primary Physical Parameters                     | 111  |

| 5.1.2 The Fitting Parameters                          | .111 |

| 5.1.3 The Smooth-Function Parameters                  | .112 |

| 5.2 Optimization Techniques                           | 113  |

| 5.2.1 Error Functions                                 | 113  |

| 5.2.2 Optimization Methods                            | 114  |

| 5.2.3 Least Square Fitting Techniques                 | 117  |

| 5.3 Parameter Extraction Strategies in S-CMOS Model   | 118  |

| 5.3.1 Optimization Method                             | 119  |

| 5.3.2 Multi-objective parameter extraction            | .120 |

| 5.3.3 Extraction Strategies                           | 121  |

| 5.3.4 Geometric Space                                 | 121  |

| 5.4 Parameter Extraction Phase                        | 125  |

| 5.4.1 Parameter Extraction phase                      | 125  |

|                                                       |      |

| 5.4.2 Data measurment                                           | 127 |

|-----------------------------------------------------------------|-----|

| 5.5 S-CMOS Parameter Extraction Process                         | 128 |

| 5.5.1 The Parameter Extraction procedure                        | 128 |

| 5.5.2 Model Parameter Extractor in MATLAB                       | 135 |

| Chapter 6. Implementation of S-CMOS Model                       | 146 |

| 6.1 Implementation to SPICE3f3 Simulator                        | 146 |

| 6.1.1 SPICE Analysis                                            | 149 |

| 6.1.2 Primary functions in SPICE3f3                             | 151 |

| 6.1.3 S-CMOS Model implementation in SPICE3f3                   | 154 |

| 6.2 Charge Conservation and Circuit Simulation                  | 157 |

| 6.3 Comparison of Circuit Simulation Performance                | 159 |

| 6.3.1 Folded-Cascode Operational Amplifier                      | 159 |

| 6.3.2 Wide-Range Gilbert Multiplier                             | 164 |

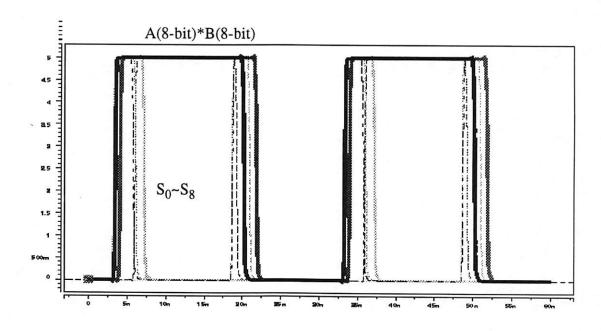

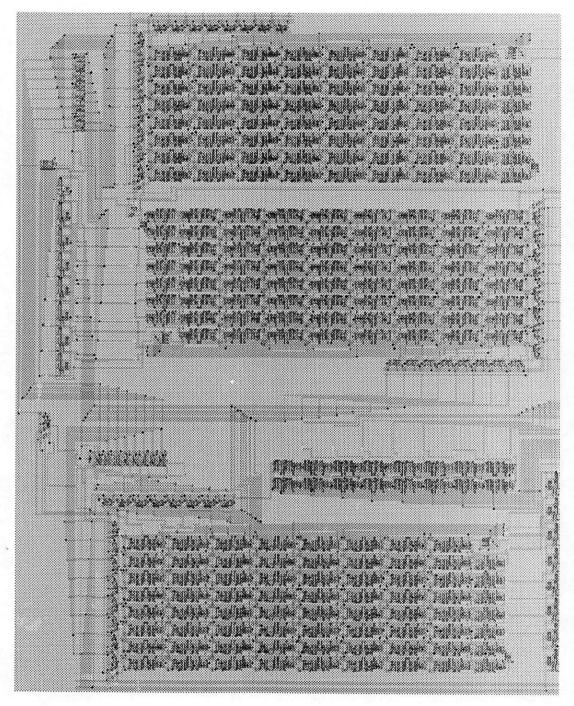

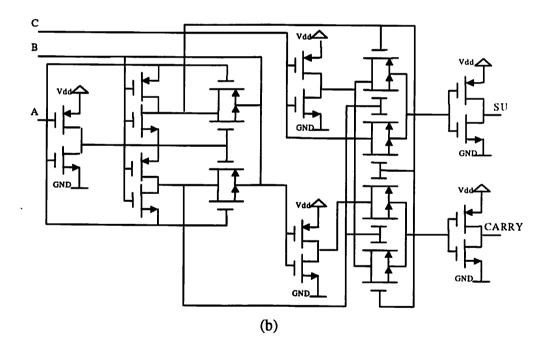

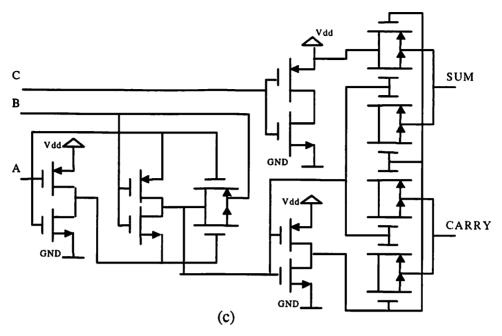

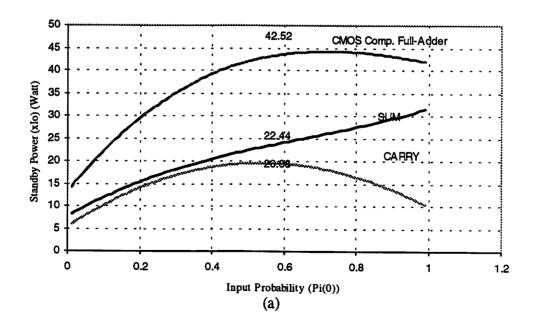

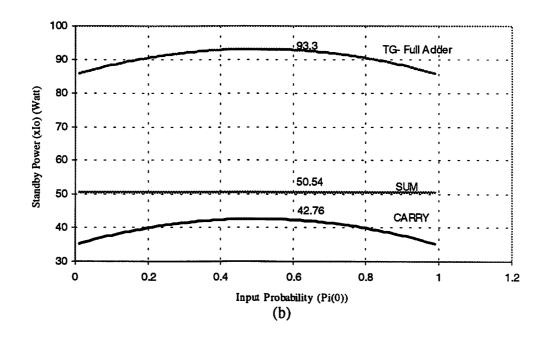

| 6.3.2 Carry Save Multiplier                                     | 168 |

| Chapter 7. Discussion and Future direction                      | 177 |

| Appendices                                                      | 182 |

| Appendix A:Low power Application for Digital CMOS circuits      | 182 |

| Appendix B: User guide for SPICE3f3 implementation of S-CMOS    | 216 |

| Appendix C: S-CMOS parameter Extractor source files             | 219 |

| Appendix D: SPICE files for the circuits simulation             | 240 |

| Appendix E: Mathcad source code for numerical Example of S-CMOS | 245 |

## List of Figures

| Chapter 1. Introduction.                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.1: The main flowchart of mixed-signal VLSI circuit and system design                                                          |

| Figure 1.2: An advanced VLSI design environment                                                                                        |

| Chapter 3 DC Expression for S-CMOS Model                                                                                               |

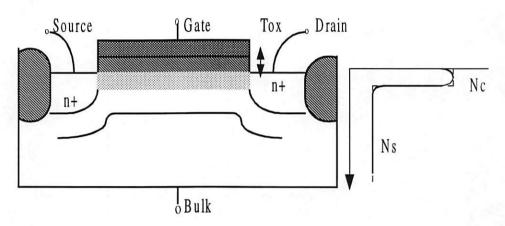

| Figure 3.1: Non-uniform Doping Concentration along the channel                                                                         |

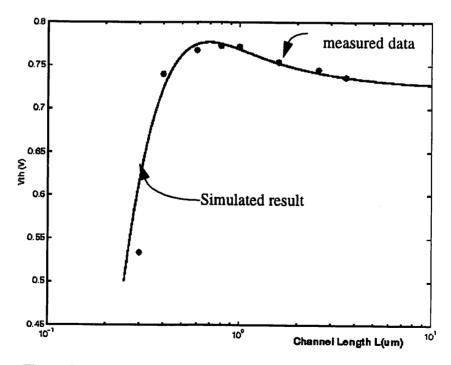

| Figure 3.2: Reverse Short Channel Effect on Threshold voltage                                                                          |

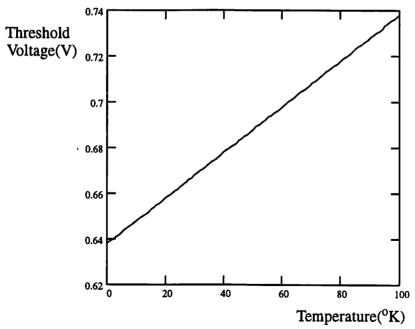

| Figure 3.3 Temperature dependency on V <sub>th</sub> : plot of the Vth vs. temperature 4                                               |

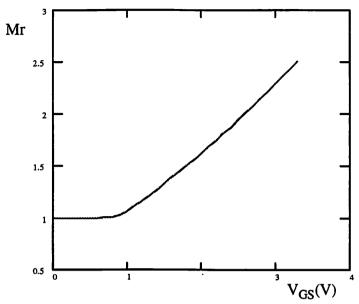

| Figure 3.4: Plot of the mobility degradation factor(Mr) versus VGS with VDS=3.3V 40                                                    |

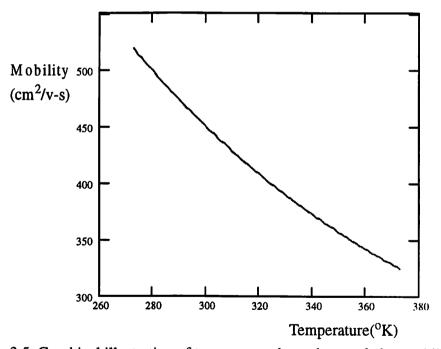

| Figure 3.5 Graphical illustration of temperature dependency of the mobility 48                                                         |

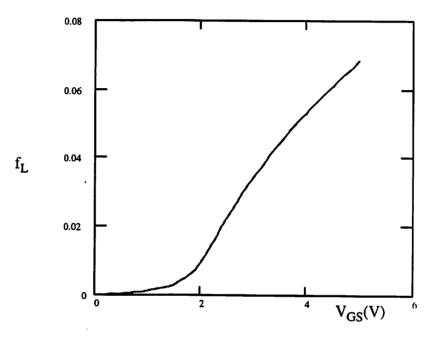

| Figure 3.6 Plot of the fL(channel length reduction factor) versus V <sub>GS</sub> 50                                                   |

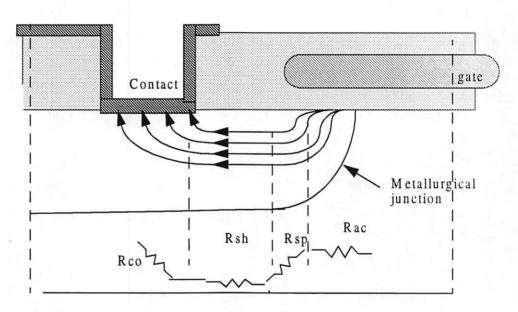

| Figure 3.7: Component of parasitic resistance in source/drain regions                                                                  |

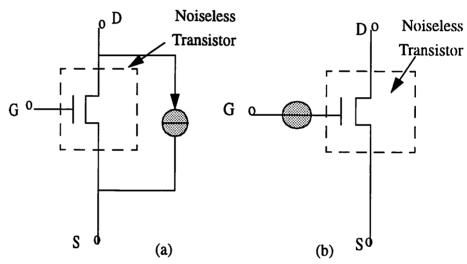

| Figure 3.8: Noise mosel (a) Current source model (b) Voltage source model                                                              |

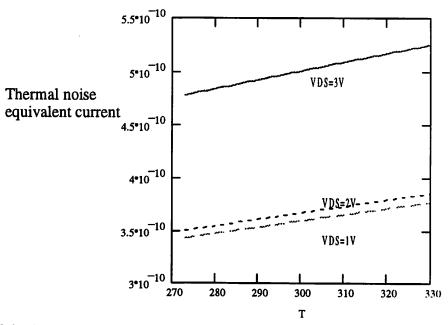

| Figure 3.9: Simulation result of Thermal noise equivalent current vs. temperature 54                                                   |

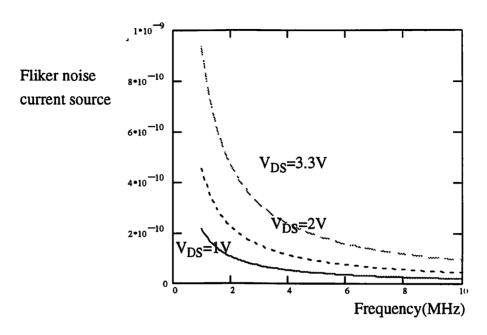

| Figure 3.10: Simulation result of Fliker noise equivalent current vs. temperature 56                                                   |

| Figure 3.11: Simulation result of shot noise equivalent current vs. VDS 56                                                             |

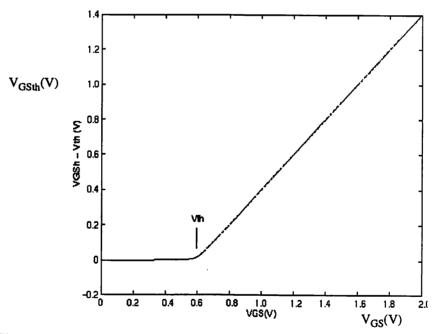

| Figure 3.12 Graphical illustration of the function (V <sub>Gsh</sub> -V <sub>th</sub> ) which reduces to zero in weak inversion region |

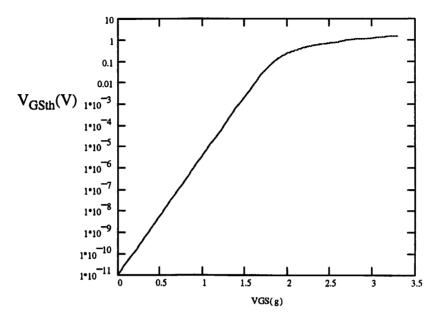

| Figure 3.13 Plot of the VGSth versus VGS with VDS=1V, VBS=0V                                                                           |

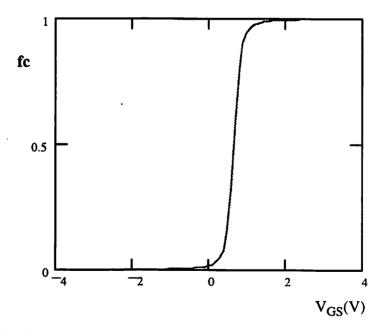

| Figure 3.14 Plot of the fc versus V <sub>GS</sub> with V <sub>DS</sub> =1V, V <sub>RS</sub> =0V                                        |

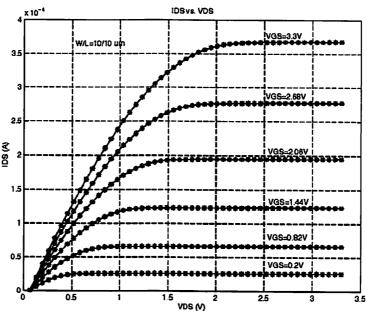

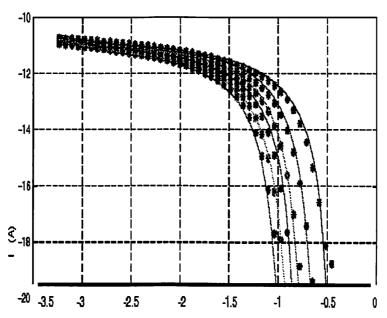

| Figure 3.15: Measured versus simulated drain current results for NMOS Transistor with W/L=10μm/10μm, and VBS=0V. [MOSIS 0.35μm Tech]63   |

|------------------------------------------------------------------------------------------------------------------------------------------|

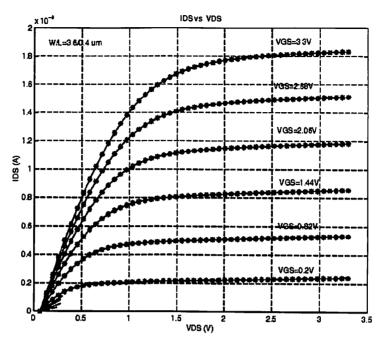

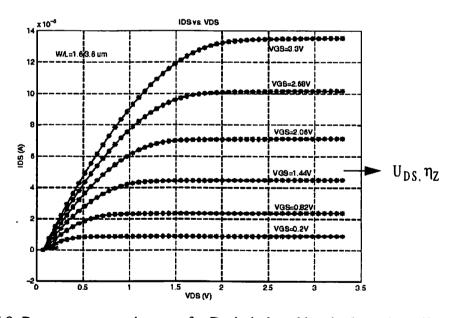

| Figure 3.16: Measured versus simulated drain current results for NMOS Transistor with W/L=3.6μm/0.4μm, and VBS=0V. [MOSIS 0.35μm Tech]64 |

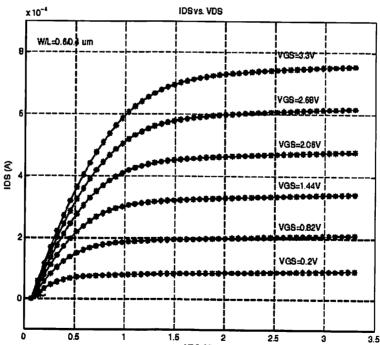

| Figure 3.17: Measured versus simulated drain current results for NMOS Transistor with W/L=0.6μm/0.4μm, and VBS=0V. [MOSIS 0.35μm Tech]   |

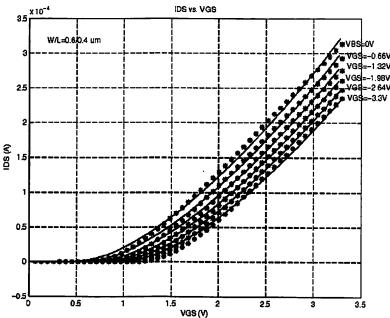

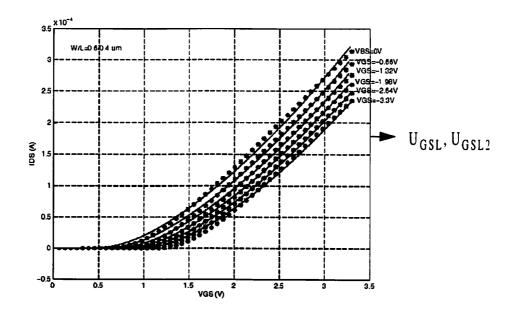

| Figure 3.18: Measured versus simulated drain current results for NMOS Transistor with W/L=0.6μm/0.4μm, and VDS=0.2V. [MOSIS 0.35μm Tech] |

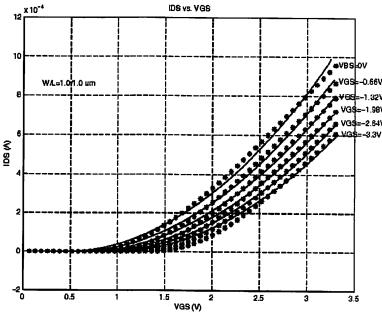

| Figure 3.19: Measured versus simulated drain current results for NMOS Transistor with W/L=1.0μm/1.0μm, and VDS=0.2V. [MOSIS 0.35μm Tech] |

| Figure 3.20: Measured versus simulated drain current results for NMOS Transistor with W/L=3.6μm/1.0μm, and VDS=0.2V. [MOSIS 0.35μm Tech] |

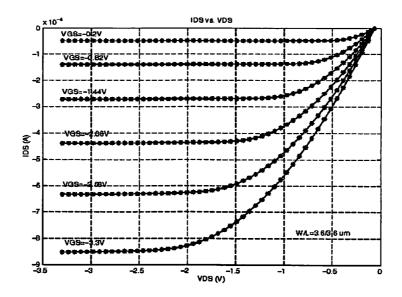

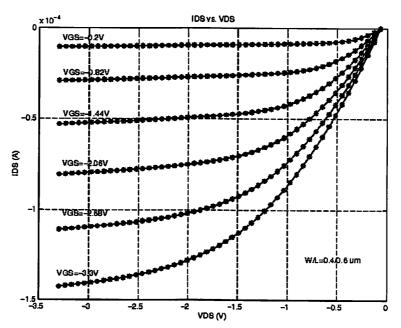

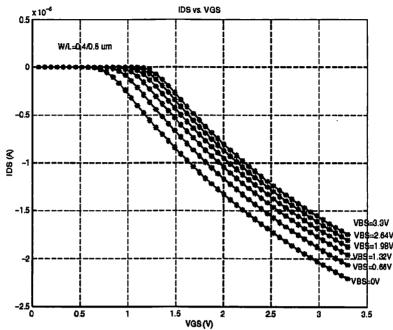

| Figure 3.21: Measured versus simulated drain current results for PMOS Transistor with W/L=0.4μm/0.6μm, and VBS=0V. [MOSIS 0.35μm Tech]   |

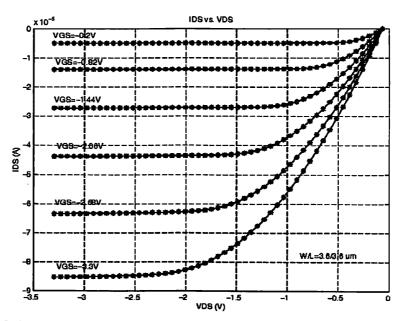

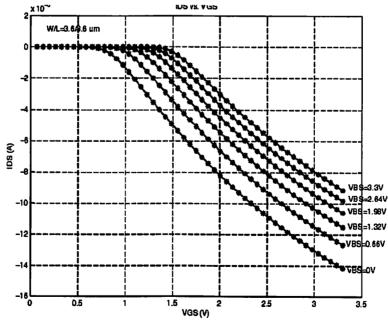

| Figure 3.22: Measured versus simulated drain current results for PMOS Transistor with W/L=3.6μm/3.6μm, and VBS=0V. [MOSIS 0.35μm Tech]   |

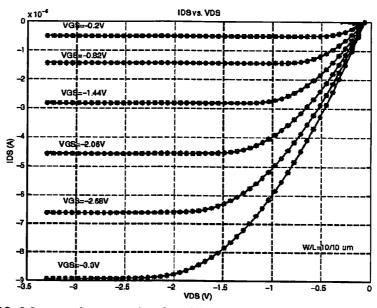

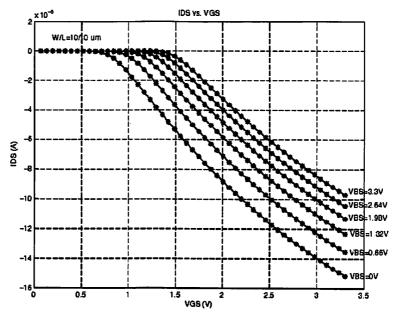

| Figure 3.23: Measured versus simulated drain current results for PMOS Transistor with W/L=10μm/10μm, and VBS=0V. [MOSIS 0.35μm Tech]     |

| Figure 3.24: Measured versus simulated drain current results for PMOS Transistor with W/L=0.4μm/0.6μm, and VBS=0V. [MOSIS 0.35μm Tech]   |

| Figure 3.25: Measured versus simulated drain current results for PMOS Transistor with W/L=3.6μm/3.6μm, and VBS=0V. [MOSIS 0.35μm Tech]   |

| Figure 3.26: Measured versus simulated conductance(gds) results for NMOS Transistor with W/L=10μm/10μm, and VBS=0V. [MOSIS 0.35μm Tech]  |

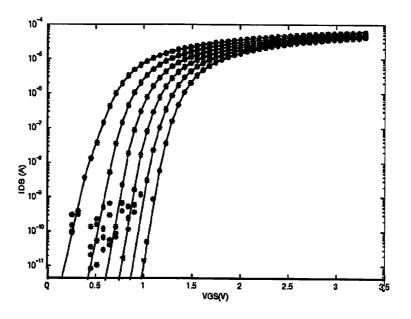

| Figure 3.27: Measured versus simulated drain current results for NMOS Transistor with W/L=10μm/10μm, and VBS=0V. [MOSIS 0.35μm Tech]     |

| Figure 3.28: Measured versus simulated drain current results for PMOS Transistor with W/L=10μm/10μm, and VBS=0V. [MOSIS 0.35μm Tech]     |

| Chapter 4 Charge/Capacitance Model                                                                                                       |

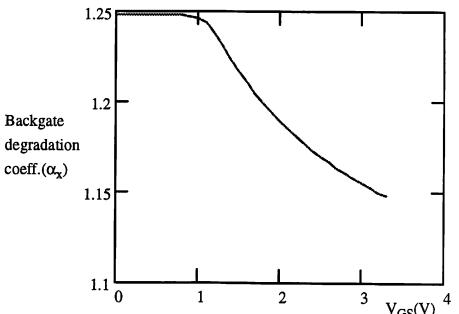

| Figure 4.1: Graphical illustration of the back-gate degradation coefficient ( $\alpha x$ )                                      |

|---------------------------------------------------------------------------------------------------------------------------------|

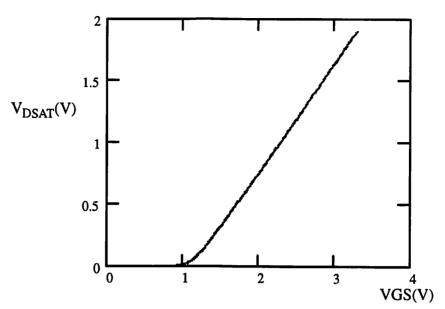

| Figure 4.2 Plot of VDSAT versus VDS with VDS=1V, VBS=0V                                                                         |

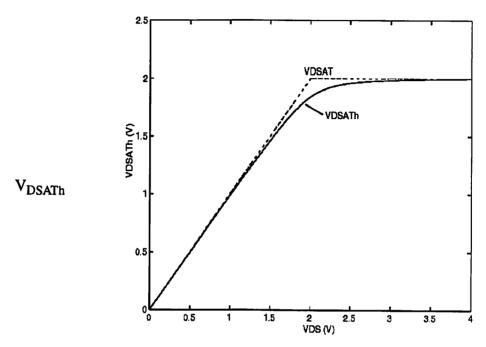

| Figure 4.3: Plots of the VDSATh versus VDS with VGS=3.3V, VBS=0V77                                                              |

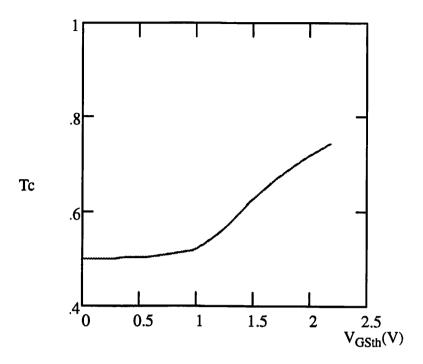

| Figure 4.4: Plots of the Tc versus VGS-Vth with VDS=1V and VBS=0V79                                                             |

| Figure 4.5: Graphical illustration of the Tc versus VGS-Vth                                                                     |

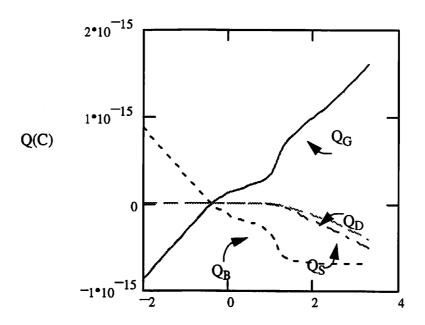

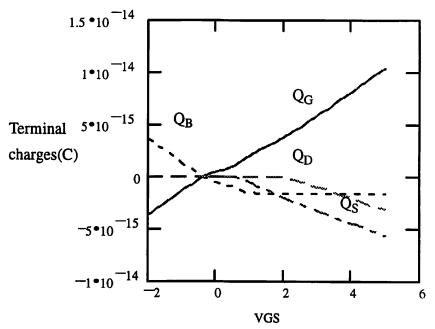

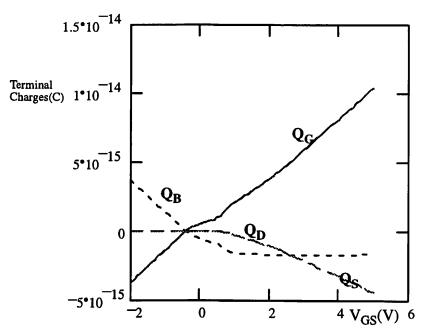

| Figure 4.6: Plots of the Terminal charges versus VGS with VDS=1V and VBS=()V8                                                   |

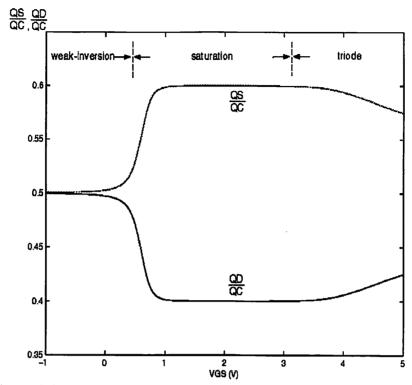

| Figure 4.7: Plots of the drain and source charges versus V <sub>GS</sub>                                                        |

| Figure 4.8: Plots of the terminal charges versus VGS in different operation regions with VDS=1V and VBS=0V                      |

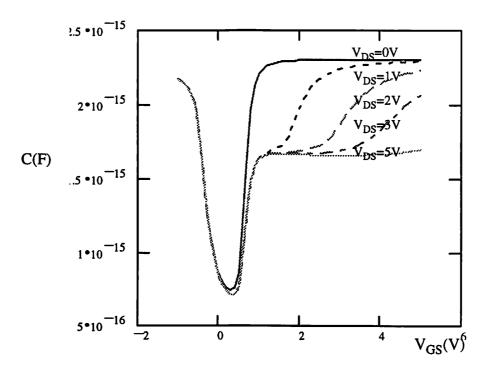

| Figure 4.9: Gate capacitances versus gate voltage for VDS=0, 1, 2, 3, 5V 86                                                     |

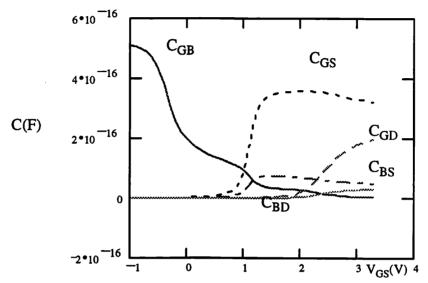

| Figure 4.10: Terminal capacitances versus gate voltage for VDS-=1V                                                              |

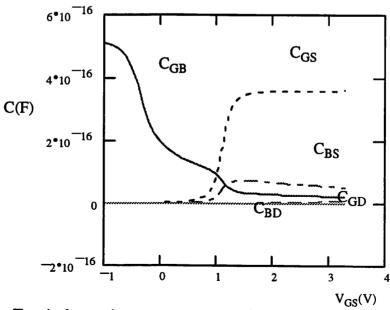

| Figure 4.11: Terminal capacitances versus gate voltage for VDS-=3.3V                                                            |

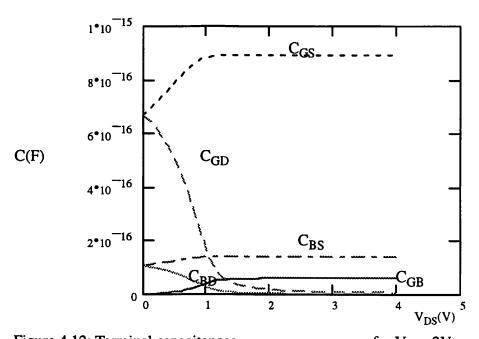

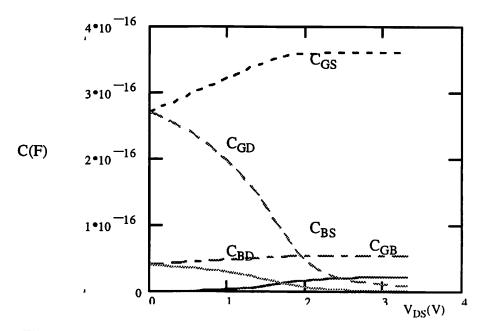

| Figure 4.12: Terminal capacitances versus drain voltage for VGS=1V88                                                            |

| Figure 4.13: Normalized terminal capacitances versus drain voltage for VGS=3.3V 88                                              |

| Figure 4.14: Normalized terminal capacitances versus drain voltage for VGS=3.3V 90                                              |

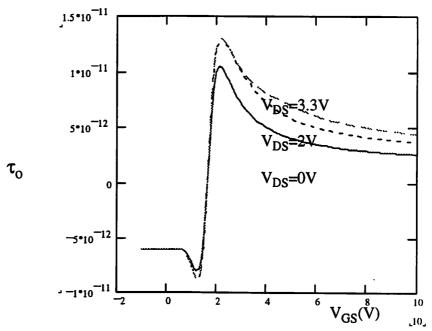

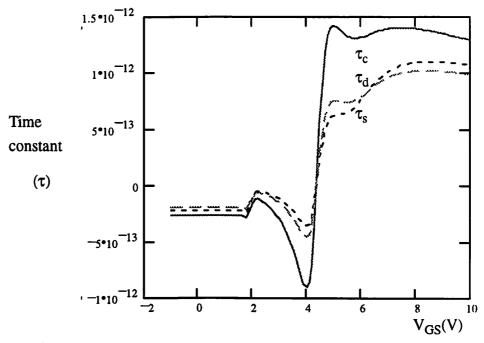

| Figure 4.15: The plots of τ <sub>o</sub> versus VGS for VDS=3.3, 2, 0V and VBS=1V for W/L= 1μm /0.5μm NMOS Transistor96         |

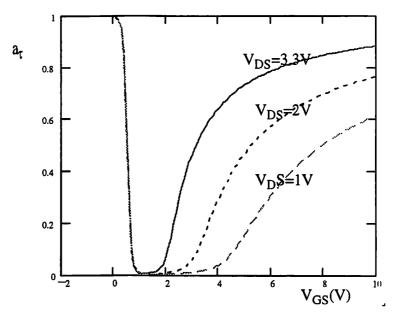

| Figure 4.16: Plots of a <sub>t</sub> versus VGS for VDS=1, 2, 3V, and VBS=1V for W/L=1.0µm/0.5µm NMOS Transistor                |

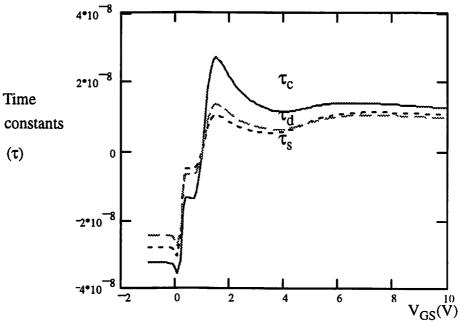

| Figure 4.17:Plots of time constants versus gate voltage for VDS=3.3V and VBS=1V.for W/L= 50μm/50μm NMOS Transistor              |

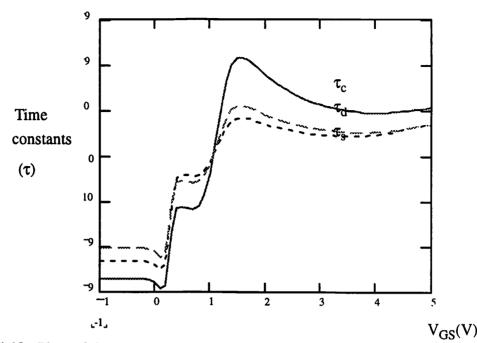

| Figure 4.18:Figure 4.23: Plots of time constants versus gate voltage for VDS=3.3V and VBS=1V. for W/L=10μm/10μm NMOS Transistor |

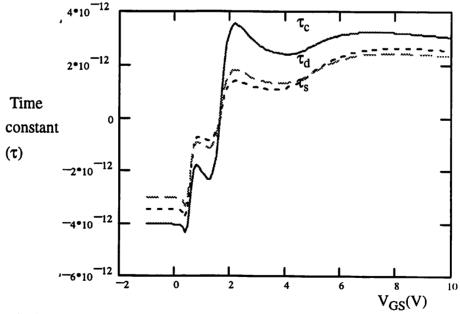

| Figure 4.19: Plots of time constants versus gate voltage for VDS=3.3V and VBS=1V. for W/L= 1µm/0.5µm NMOS Transistor            |

| Figure 4.20: Plots of time constants versus gate voltage for VDS=3.3V and VBS=1V for W/L= 0.18µm/0.18µm NMOS Transistor                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

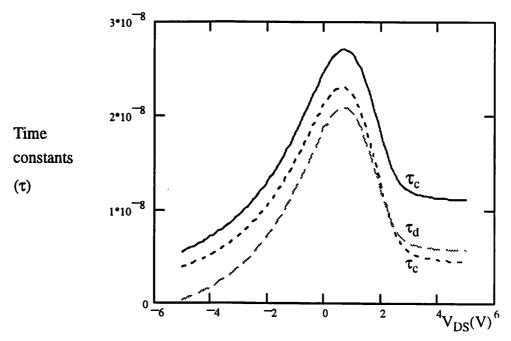

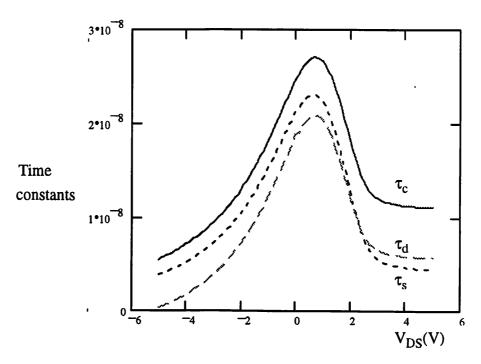

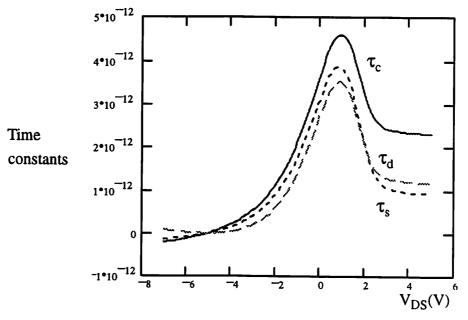

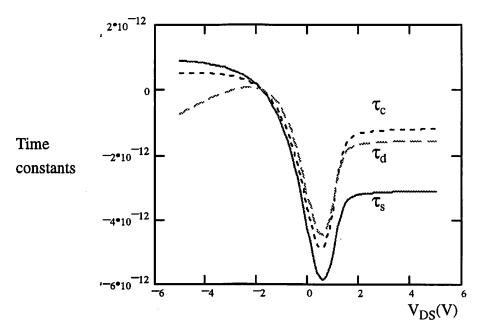

| Figure 4.21: Plots of time constants versus drain voltage for VGS=3.3V and VBS=()V.for W/L= 50μm/50μm NMOS Transistor                                                                                                 |

| Figure 4.22: Plots of time constants versus drain voltage for VGS=3.3V and VBS=()V. for W/L= 10μm/10μm NMOS Transistor                                                                                                |

| Figure 4.23: Plots of time constants versus drain voltage for VGS=3.3V and VBS=()V. for W/L= 1.0μm/0.5μm NMOS Transistor                                                                                              |

| Figure 4.24: Plots of time constants versus drain voltage for VGS=3.3V and VBS=()V. for W/L= 0.18μm/0.18μm NMOS Transistor                                                                                            |

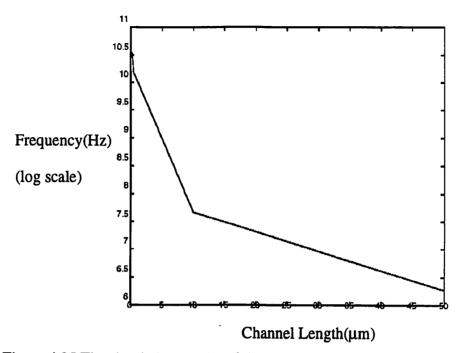

| Figure 4.25 The simulation results of time conatants in different channel length102                                                                                                                                   |

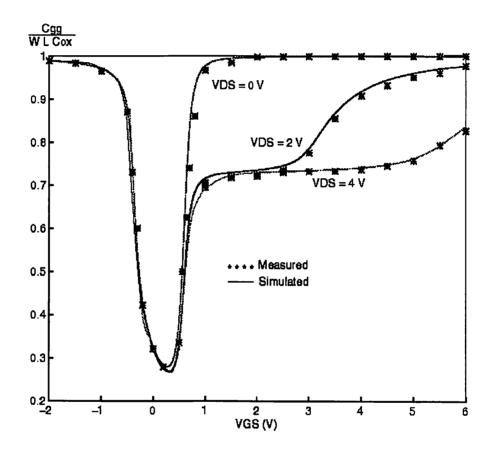

| Figure 4.26 Plots of capacitances versus VDS of an NMOS Transistor 103                                                                                                                                                |

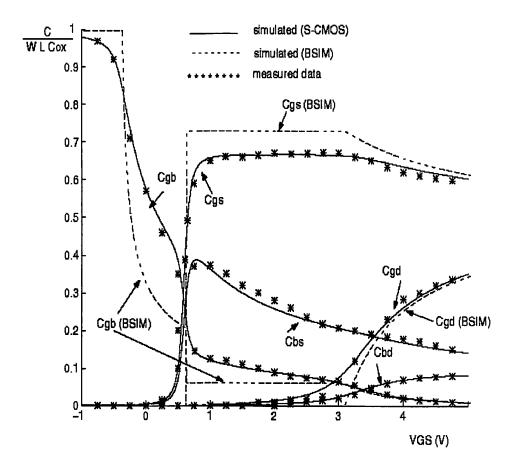

| Figure 4.27: Plots of capacitances versus VGS of an NMOS Transistor of W/L=25µm/0.5µm                                                                                                                                 |

|                                                                                                                                                                                                                       |

| . Chapter 5 S-CMOS Model Parameter Extraction 109                                                                                                                                                                     |

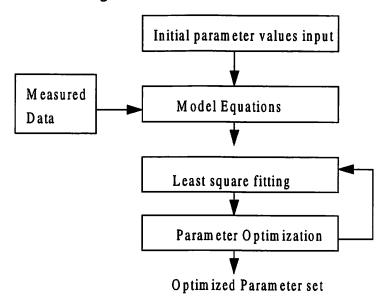

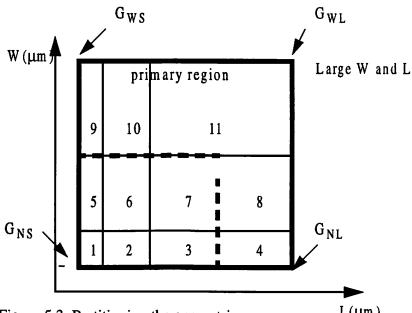

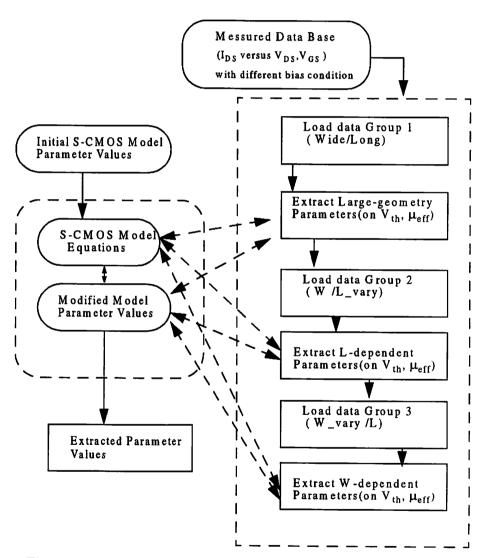

| Chapter 5 S-CMOS Model Parameter Extraction 109 Figure 5.1: Flow of the parameter extraction optimization procedure in S-CMOS 119                                                                                     |

|                                                                                                                                                                                                                       |

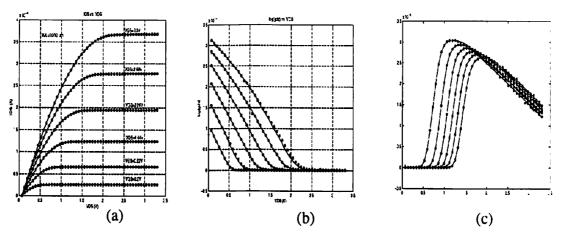

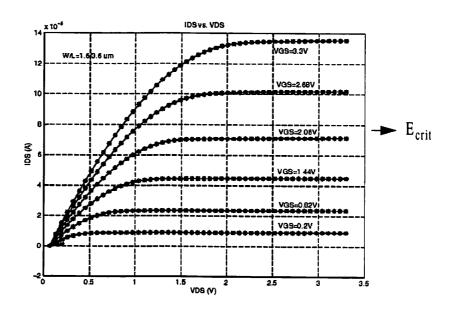

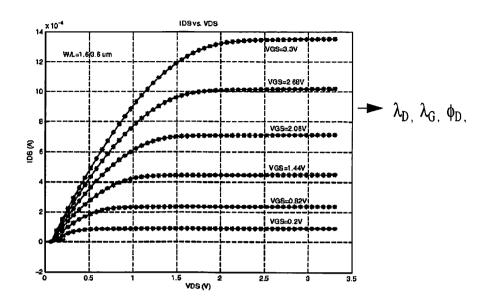

| Figure 5.1: Flow of the parameter extraction optimization procedure in S-CMOS 119 Figure 5.2: Measured versus simulated results for NMOS Transistor (a)IDS vs. VDS b)                                                 |

| Figure 5.1: Flow of the parameter extraction optimization procedure in S-CMOS 119  Figure 5.2: Measured versus simulated results for NMOS Transistor (a)IDS vs. VDS b)  gds vs. VDS (c) gm vs. VGS with W/L=10μm/10μm |

| Figure 5.1: Flow of the parameter extraction optimization procedure in S-CMOS                                                                                                                                         |

| Figure 5.1: Flow of the parameter extraction optimization procedure in S-CMOS                                                                                                                                         |

| Figure 5.1: Flow of the parameter extraction optimization procedure in S-CMOS                                                                                                                                         |

| Figure 5.1: Flow of the parameter extraction optimization procedure in S-CMOS                                                                                                                                         |

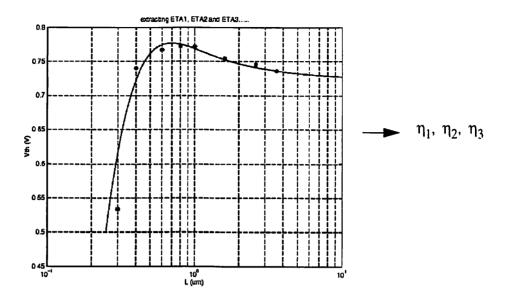

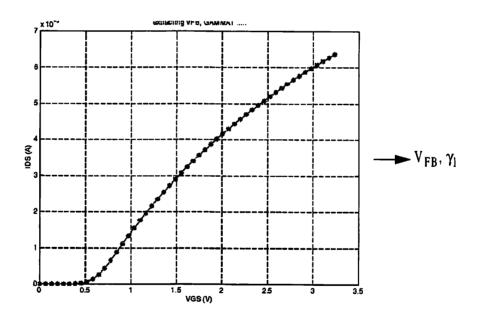

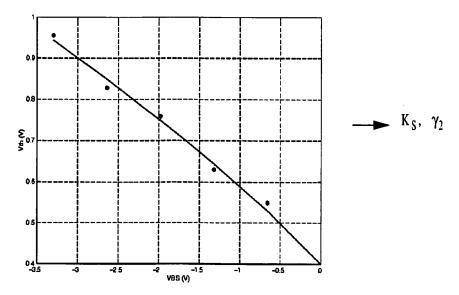

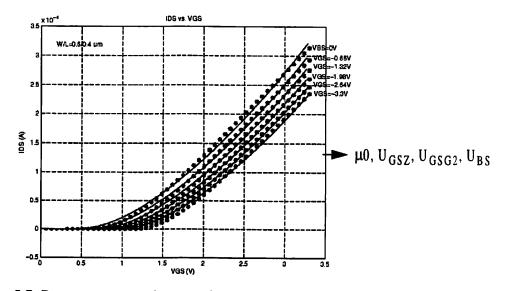

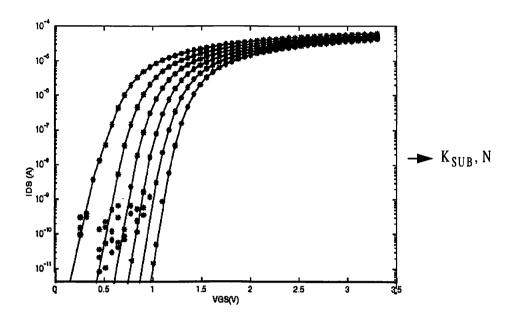

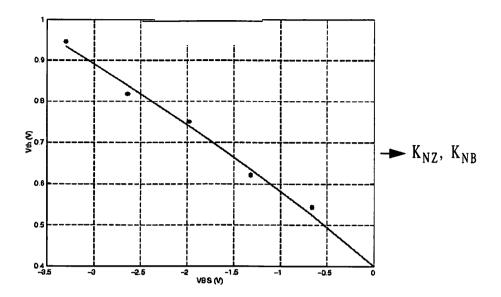

| Figure 5.10: Parameter extraction step for narrow channel threshold voltage  | . 132 |

|------------------------------------------------------------------------------|-------|

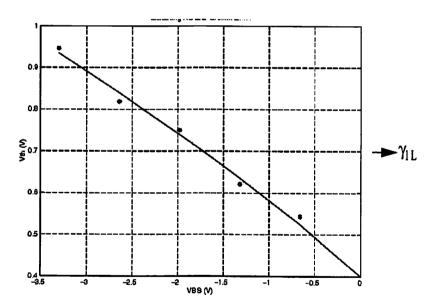

| Figure 5.11: Parameter extraction step for short channel body effects        | 132   |

| Figure 5.12: Parameter extraction step for gate-voltage mobility degradation | . 133 |

| Figure 5.13 : Parameter extraction step for critical electrical field        | 133   |

| Figure 5.14: Parameter extraction step for Channel Length Modulation Effects | . 134 |

| Figure 5.15: Parameter extraction procedure in S-CMOS Model                  | 135   |

| Chapter 6. Implementation of S-CMOS Model                                    | 146   |

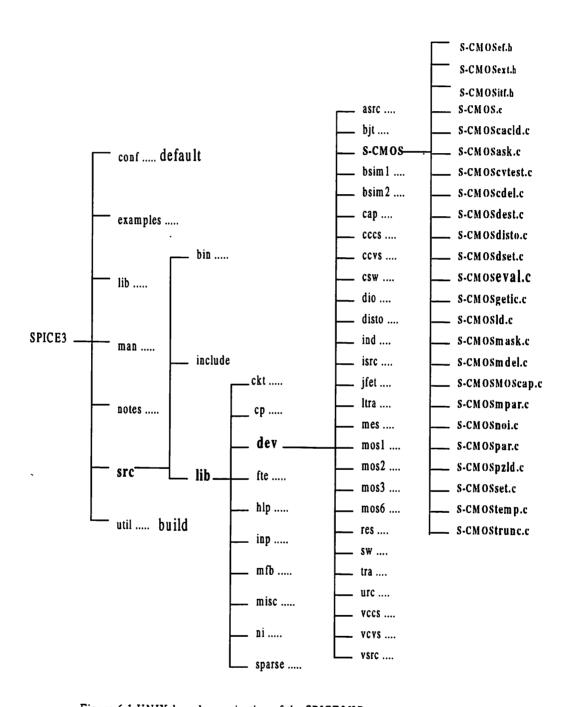

| Figure 6.1: UNIX-based organization of the SPICE3f3P program                 | . 152 |

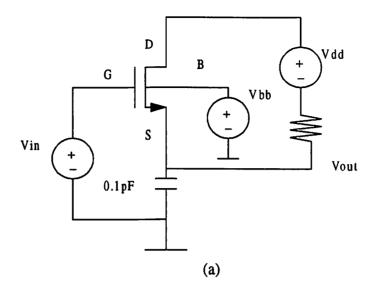

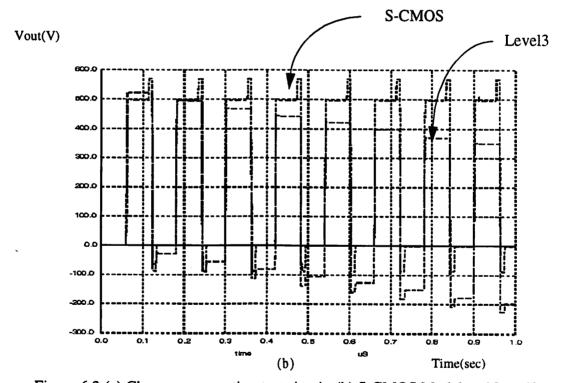

| Figure 6.2:(a)Charge conservation test circuit(b) S-CMOS Model and Level3    | . 159 |

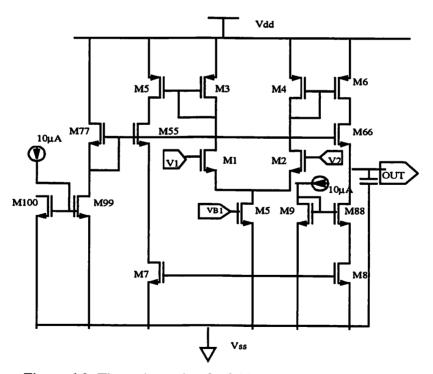

| Figure 6.3: The schematic of a folded-cascode Op-Amp                         | . 160 |

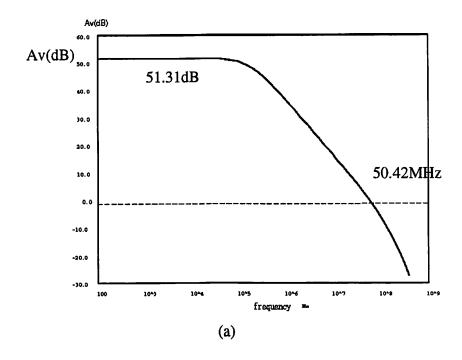

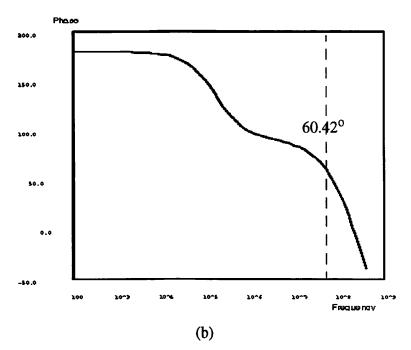

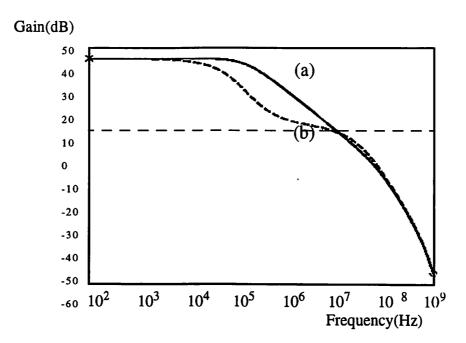

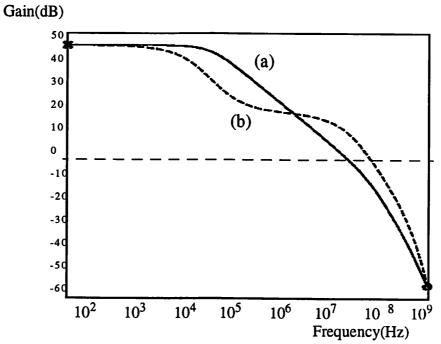

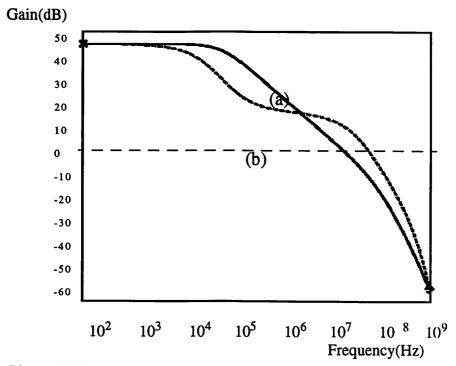

| Figure 6.4 Simulation result by S-CMOS model                                 | 161   |

| Figure 6.5 Simulation result by Level2 model                                 | . 161 |

| Figure 6.6 Simulation result by Level3 model                                 | 162   |

| Figure 6.7 Simulation result by BSIM3v3 model                                | 163   |

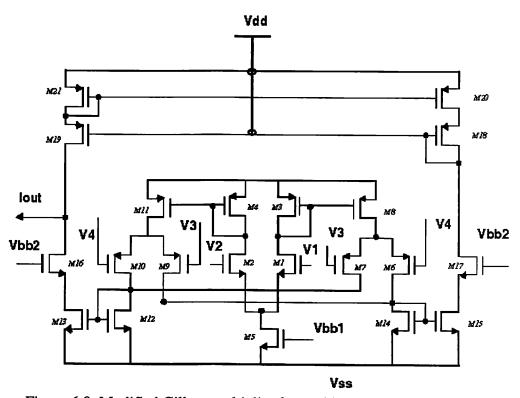

| Figure 6.8: Modified Gilbert multiplier for a wide operation range           | 165   |

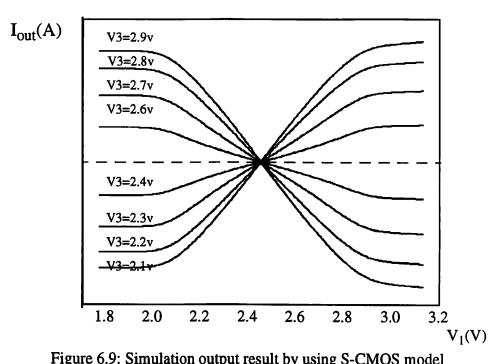

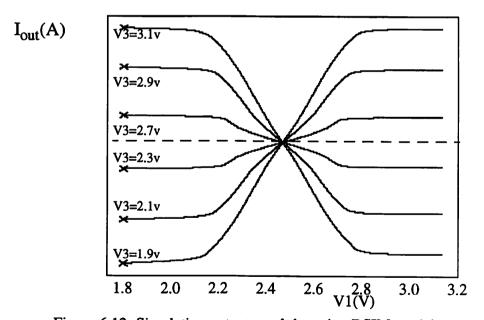

| Figure 6.9: Simulation output result by using S-CMOS model                   | 165   |

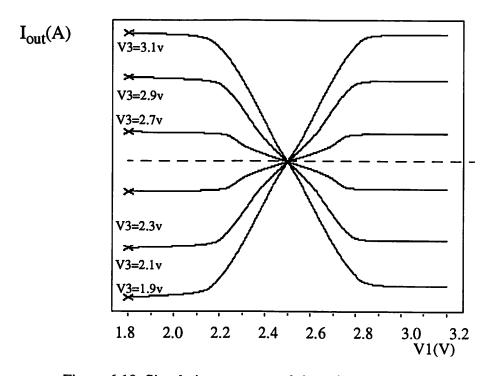

| Figure 6.10: Simulation output result by using Level2 model                  | 166   |

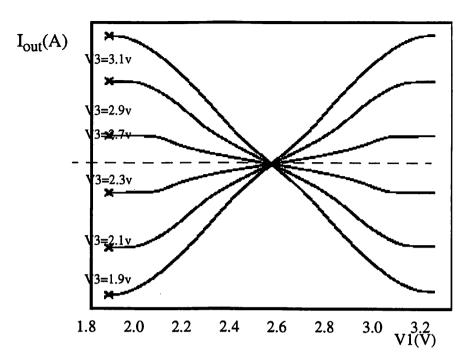

| Figure 6.11: Simulation output result by using Level3 model                  | 166   |

| Figure 6.12: Simulation output result by using BSIM model                    | 167   |

| Figure 6.13: Simulation output result by using BSIM3v3 model                 | 167   |

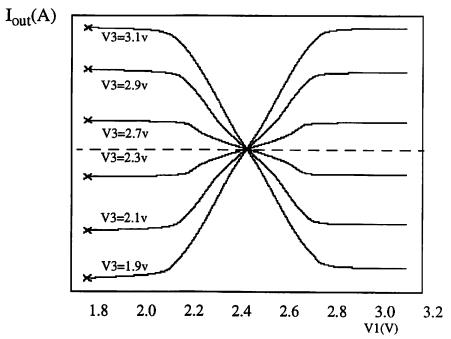

| Figure 6.14 The structure of 8-bit Carry Save adder                          | 169   |

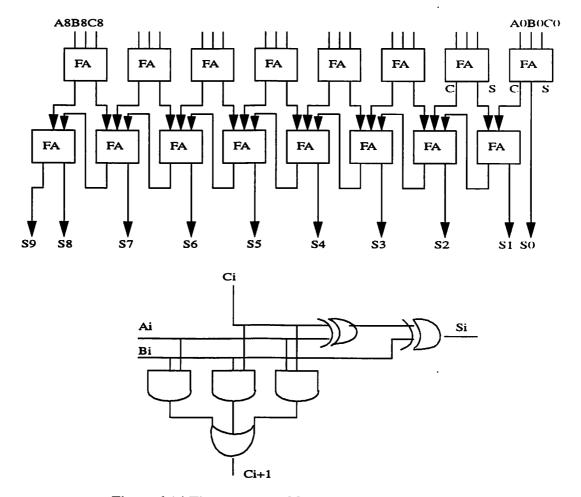

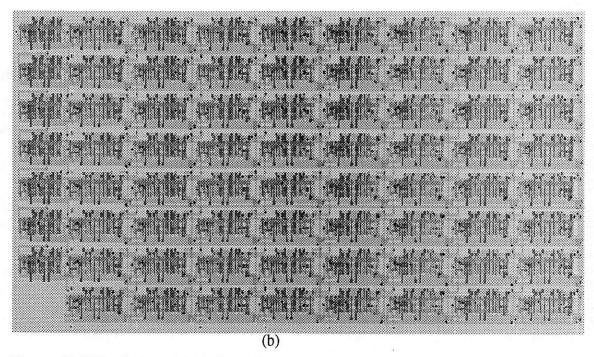

| Figure 6.15 The design of 8-bit Carry Save Multiplier (a) Block diagram of the multiplie |     |

|------------------------------------------------------------------------------------------|-----|

| (b) Layout of the multiplier                                                             | 171 |

| Figure 6.16: Simulation output result of the 8-bit carry save multiplier                 | 171 |

| Figure 6.17: The flow chart of 8-bit divider algorithm                                   | 173 |

| Figure 6.18: The layout of 8-bit divider                                                 | 174 |

## **List of Tables**

| Chapter 2. MOS Transistor Modeling                                                        | 12    |

|-------------------------------------------------------------------------------------------|-------|

| Table 2.1 The representative models comparison with S-CMOS model                          | 30    |

| Chapter 5 S-CMOS Model Parameter Extraction                                               | 109   |

| Table 5.1 S-CMOS Default Model Parameter Values                                           | .138  |

| Table 5.2.Extracted parameter values for CMOS 0.35 $\mu$ m Tech. (10/10, 0.6/10, 10/0.4)  | 140   |

| Table 5.3.Extracted parameter set for CMOS 0.35μm Tech. (10/10, 0.6/10, 10/0.4)           | . 140 |

| Table 5.4. Extracted parameter set for CMOS 0.35μm Tech.(10/0.4, 0.6/0.4, 5/0.4)          | . 141 |

| Table 5.5. Extracted parameter set for CMOS 0.35μmTech.(10/0.4, 0.6/0.4, 1.2/0.4)         | . 141 |

| Table 5.6. Extracted parameter set for CMOS 0.35μmTech.(10/10, 0.6/10, 5/0.4)             | . 142 |

| Table 5.7: Extracted parameter set for CMOS 0.35μmTech.(10/10, 0.35/10, 10/().4)          | 142   |

| Table 5.8. Extracted parameter set for CMOS 0.35µmTech.(2.5/1, 0.35/1, 2.5/().4)          | 143   |

| Chapter 6. Implementation of S-CMOS Model                                                 | 146   |

| Table 6.1: Simulated performance characteristics of the single stage folded cascode O Amp |       |

| Table 6.2 Simulated performance characteristics of Gilbert multiplier                     | 168   |

| Table 6.3 Simulated performance characteristics of 8-bit Carry save multiplier            | 172   |

| Table 6.4 Simulation comparison of the models                                             | 173   |

| Chapter 7. Discussion and Future direction                                                | 177   |

| Table 7.1 The Important features in many properties of the S-CMOS model                   | 178   |

| Table 7.2 The comparison in computation time and applicable technology                    | 180   |

### **Abstract**

A robust deep-submicron Short-Channel MOS transistor model (S-CMOS) is developed. All operation regions of MOSFET can be simulated with unified expression of S-CMOS model including the triode, saturation, subthreshold, weak and strong inversion regions. Temperature dependency on threshold voltage and effective mobility was investigated and efficient model was developed. Simple noise model was developed to describe the behavior of the noise in MOSFET devices. The effective mobility expression includes the effects of lateral and vertical electric fields in the channel efficient degradation factor which simplifies the expression and reduce the computation time. The unified drain current and terminal charge expressions, which provides a highly continuous behavior for the conductances and capacitances in all regions of operation are developed and the robustness was verified by simulating every mathematical components. The charge model uses the better expression of conductance degradation coefficient to model the channel charge density. The unified expressions of charge densities are valid for all operation regions, including the accumulation region. Non-quasi-static charge capacitance analysis is developed for radio frequency application and a unified first-order non-quasi-static expression including time constants for long-channel transistor and high frequency are derived. The

characteristics of time constants in all geometric regions are simulated and analyzed for high frequency Very large Scale Integration (VLSI) application. Efficient parameter extraction procedure was developed by using multiple-objective function which is able to include not only drain current but also conductance and transcoductance characteristic of the transistor and the extraction procedure of the S-CMOS model was implemented in MATLAB software. The accurate parameter values are extracted in accordance with the measurement data of 0.35µm technology transistors from MOSIS Service. The S-CMOS model is implemented into SPICE3f3 from U.C. Berkley successfully under SUN Solaris 2.6. and the performance comparison of S-CMOS, MOS Level2, Level3, BSIM, and BSIM3v3 models in circuits simulation including folded-cascode Op-Amp, analog multiplier, comparator, 8-bit carry-save adder, and 8-bitx8-bit carry-save multiplier are demonstrated. Detailed design and simulation results on efficient 8-bitx8bit divider design and simulation results are also included. The estimation methods of dc power dissipation of basic CMOS digital circuit blocks are also presented.

# **Chapter 1**

## Introduction

The idea of complementary MOSFET (Metal Oxide Semiconductor Field Effect transistor) was introduced in early 1960's. With the benefit of improvements in the Integrated Circuits(IC) fabrication technology in 1980's, Complementary Metal Oxide Semiconductor (CMOS) technology was widely accepted and used for VLSI system implementation. This acceptance was because of the unique advantages of CMOS circuits over nMOS and Bipolar junction transistor counterparts. CMOS technology consumes less power than other technologies and it is very suitable for battery-operated systems. Also, low cost, high-package density, large design margin (easy to design,) high noise margin, easy to scaling, wider temperature and voltage operation range make CMOS technology unique and promising for Very large-scale integration (VLSI) and Ultra large-scale integration (ULSI). VLSI circuits fabricated by metal-oxide-semiconductor (MOS) technologies are widely used in industry to implement high-performance computing, signal processing, multimedia, and telecommunication systems [1]. As the integrated-circuit industry continues its tremendous growth, a urgent concern is the industrial standard MOSFET models that can be commonly used in integrated-circuit simulation. MOSFET models are taken as representing the electrical behavior of a particular transistor fabrication technology and

provide the critical link, the "communication vehicle" between a foundry and its fabless customers. The emergence of CMOS as the main fabrication technology over the past decade has been accompanied by a reduction in feature size from 2.5µm to 0.18µm, an increase in chip area from 50mm<sup>2</sup> to 300mm<sup>2</sup>, and an increase in the number of transistors from 100,000 to 1 billion for memories and from 60,000 to over 7 million for microprocessors [2], the further newest multi-chip-module (MCM) package technology can bind several chips in a single substrate with more than 20 million transistors, a drop in the onchip gate delay from 1 nano-second to 10 pico-second and an increase in the chip clock frequency from 10 MHz to over 1 GHz [3]. In the competitive industrial environment, efficient design automation is invaluable in ensuring that high-quality products developed within a short period of time. In such an environment, circuit and system designs can take place simultaneously with continuous technology improvement. This requires closer relationship in the vertical integration from the device-level simulation through the circuitlevel design to the system-level simulation. In recent years, concurrent engineering has been replacing traditional isolated design and manufacture approaches.

The level of circuit integration on a single chip has been greatly increased by new lithography and etching techniques. The increased use of deep-submicron technologies has created new challenges for researchers in mixed-signal VLSI hardware design, high-performance circuit simulation, and microelectronic system design. At the transistor level, detailed investigation of small-geometry effects on the behavior of transistors is required. Effects of coupling between interconnections and neighboring devices can be more significant due to compactness of the circuit. The degradation of device behavior with time of

operation can be more significant due to higher electrical stresses in the channel region of MOS transistors. At the circuit design level, accurate modeling of transistors is urgently needed so that special features of advanced technologies can be exploited to the greatest extent. Desirable features of the model include a compact set of parameters, continuity of the drain current and its derivatives across different regions of operation, and the ability to use a single parameter set over a large geometric design space. At the system design level, new architectures are required in order to utilize advanced technologies effectively and extend boundaries of achievable performance. Advanced computer architectures are likely to use superpipelined multiprocessors with distributed memories and optical interconnections. Nowadays, the integrated media systems combine all the advanced audio/video, telecommunication, and memory technologies to structure the information super-highway. Simultaneous efforts at the device, circuit, and system levels are essential in order to achieve the high performance computing and communication.

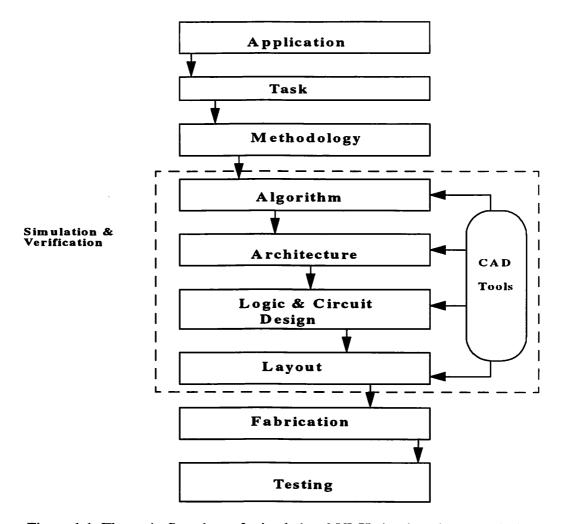

The main flowchart of mixed-signal VLSI circuit and system design is shown in Fig 1.1. Application is the first and most important issue, such as multimedia, telecommunication, microprocessor, hard disk drive, etc., which determines the aspect of the VLSI design. After that, the design methodology and algorithm should be determined to optimize the design cost and expected performance. During the circuit implementation period, simulation and verification are needed for each step to ensure the correction of the function and operation. In order to achieve the new generation of VLSI design which involves a very complex design procedure, the advanced computer-aided design (CAD) tools are required.

Figure 1.1: The main flowchart of mixed-signal VLSI circuit and system design

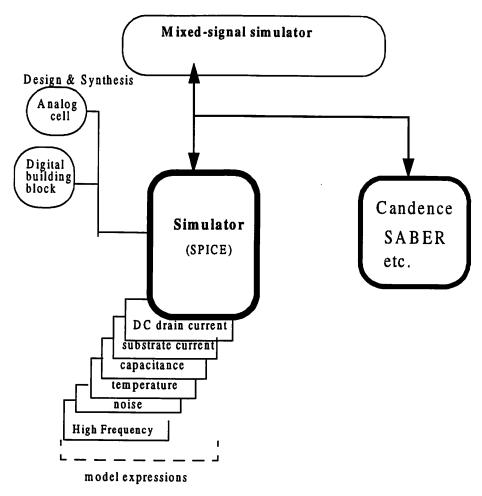

Fig.1.2. shows the main component of an advanced VLSI design environment. In the design and synthesis portion, the CAD tools for the digital domain are fairly well developed. However, the design of the analog sections often remains a bottleneck. To increase the efficiency of the design process, and reduce the design time for the mixed-signal VLSI, the analog CAD should be paid a lot of attention. Due to short prototype development time, device/process simulators such as SUPREM[9], SAMPLE and PISCES[10] from Stanford University can be used to analyze the effects of adjusting process variables,

and to predict detailed device behavior. Device simulators can be used to generate circuitlevel parameters so that simulation can be performed for prediction of circuit performance. This link between device and circuit simulators enables optimization of fabrication

processes based on circuit performance. The core of VLSI simulation environment contains circuit simulators such as SPICE from U.C. Berkeley [4], which use models of

devices such as transistors to predict the detailed electrical behavior of analog and digital

circuits.

Figure 1.2: An advanced VLSI design environment

The model expressions calculate the terminal voltage and current waveforms of devices based on model parameters. Several commercial circuit simulators are based upon the SPICE program including HSPICE from Avant! Corp.[5]. and PSPICE from Microsim Corp. [6]. The use of macro-models increases the efficiency of these detailed circuit simulators. Some circuit simulators such as SPLICE from U.C. Berkeley [11] and iSPLICE from Univ. of Illinois, can perform simulation of mixed-signal circuits that contain substantial analog and digital circuitry. Other circuit simulators such as RELAX from U.C. Berkeley [12] and AWESIM from Carnegie Mellon University use waveform relaxation techniques to speed up simulation tasks. In addition to simulation results of the freshly manufactured circuit, the designer may require information about the degraded performance of a circuit after it has operated for some period of time, because the use of extremely small feature sizes causes concerns of transistor and interconnection reliability. Reliability simulators such as RELY from University of Southern California [7], BERT from U.C. Berkeley [14], and iSMILE from Univ. of Illinois, can be used to predict the lifetime of circuits based on technology-dependent degradation parameters. Reliability simulation results can be used to modify circuit designs for reliability enhancement before actually committing the circuit to fabrication. Reliability predictions are also useful in determining warranties to be given to customers using electronic products. At the highest level of abstraction in the simulation environment, logic and timing simulators use behavioral models of the circuit to predict and verify the functionality and speed performance of electronic sub-systems or systems. IC designers moving to deep submicron technologies face big challenges. Initial design projects have experienced unexpectedly long design cycles, a larger than expected number of design iterations, problems getting chips to oper-

ate at target clock speeds and surprises with die size late in the design cycle. The effects of deep submicron geometries, higher clock speeds, and soaring gate counts all create new design problems that are not addressed by existing tools and methodologies. The limitations of available tools and methodologies are clear. Logic designers, who once needed to know little about the physical implementation of their devices to successfully complete their designs, must now have access to key physical design information early in the design process. Without this information, timing delays, routability, and power dissipation are not accurately predicted and the logic designer has no way of knowing if basic design constraints such as functionality, cost, power, and speed are being met. The result is often big surprises late in the design cycle. Results from the circuit simulator affect crucial decisions that are made during architectural specification, circuit design, and chip fabrication. Accurate and efficient MOS transistor models are keys to the successful operation of such VLSI simulation environments. As the integrated-circuit industry continues its tremendous growth, an urgent concern is the Industrial Standard MOSFET models that can be commonly used in integrated-circuit simulation. MOSFET models are taken as representing the electrical behavior of a particular transistor fabrication technology and provide the critical link-the "communication vehicle" between a foundry and its fabless customers[16]. In the area of standard model testing, once a particular model is selected it should be tested using standard test cases. To cope with the urgent industrial demands, Compact Short-channel MOS Model (S-CMOS) will be completed for industrial application. With the growing use of portable and wireless electronic systems, reduction in power consumption has become more and more important in today's VLSI circuit and system designs. In CMOS digital circuits, power dissipation consists of dynamic and static components.

Since dynamic power is proportional to the square of supply voltage V<sub>dd</sub> and static power is proportional to V<sub>dd</sub>, lowering supply voltage is obviously the most effective way to reduce power consumption. With the scaling of supply voltage, transistor threshold voltage (Vth) should also be scaled in order to satisfy the performance requirements. Unfortunately, such scaling leads to an increase in leakage current which becomes an important concern in low voltage high performance circuit designs. Multiple thresholds can be used to deal with the leakage problem in low voltage high performance CMOS circuits. This technique has commonly been used in DRAM chips by raising threshold voltages of the array devices with a fixed body bias. Besides reducing threshold and supply voltages, other level of power reduction methodologies, such as; architecture, system or logic/circuit levels should be used during the design process for optimizing the power dissipation of digital systems. Because reducing threshold voltage causes in an exponential increase in the leakage current, DC power consumption of the CMOS circuits becomes more crucial for low-power, low-voltage CMOS circuits. Leakage current related power consumption analysis and optimization of the CMOS digital circuits was reported in the literature lately[17]. A model for deep-submicron CMOS digital circuits were examined and applied to basic CMOS digital building blocks. 0.35µm CMOS submicron process technology model parameters and SPICE3f3 circuit simulation program[4] is used.

According to the needs of the advance MOS transistor model for circuit designers and device engineers, a deep-submicron MOS transistor model for low-power and low-voltage mixed-signal circuit design is developed. The deep-submicron techniques and some interpolation and smoothing functions will be used to achieve accuracy and continuity of the

transistor operation. Besides the drain current and charge/capacitance models, temperature and noise effects on circuit performance will also be considered in the new model. Based on the SPICE simulator structure, the new model will be designed to increase the accuracy, decrease the computational complexity, and avoid the non-convergence problem. The MOS transistor modeling problem is described in Chapter 2. Literature publications in this area have been surveyed and significant results area briefly described. In this Chapter, an overview of MOSFET modeling for circuit simulation is presented. After discussing some of the implications of analog and low-power applications, the history of the MOS models commonly used in SPICE-like circuit simulators and the simulators are presented. In Chapter 3, based on the BSIM, drain current model structure described by unified expression is introduced. In Chapter 4, a newly developed Charge/Capacitance MOSFET model and the experimental results are presented. Non-quasi-static approach for high frequency application is proposed also in this Chapter. In Chapter 5 an efficient parameter extraction procedure and its strategies are presented. Accurate S-CMOS parameter values extracted with MOSIS 0.35µm tech. are introduced in this chapter. The implementation of the model in SPICE3f3 simulations are presented in Chapter 6. The performances comparison of S-CMOS, MOS Level2, Level, BSIM1, and BSIM3v3 models in circuits simulation including folded-cascode Op-Amp, analog multiplier, comparator, 8-bit carry save adder, and 8-bitx8bit carry save multiplier are presented in this chapter. Efficient 8-bitx8bit divider design and simulation results are included in this chapter also. Finally, Chapter 7. presents discussion and conclusion for implementation in the industrial application.

drain current, output conductance, transconductance, and their derivatives in all regions of

#### **Reference List**

- [1] B. Sheu, M. Ismail, E. Sanchez-Sinencio, T. Wu, Microsystems Technology for Multimedia Applications: An Introduction, IEEE Press: Piscataway, NJ, 1995.

- [2] J. Schutz, R. Wallace,"A 450MHz IA32 P6 family microprocessor," IEEE ISSCC 1998, pp. 236-237, Feb. 1998.

- [3] J. Silberman, "A 1.0 GHz single-issue 64b Power PC integer processor," IEEE ISSCC 1998, pp. 230-231, Feb. 1998.

- [4] B. Johnson, T. Quarles, A. R. Newton, D. O. Pederson, A. Sangiovanni-Vincentelli, SPICE-3E3 User's Guide, Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, Apr. 1993.

- [5] HSPICE User manual, Avant! Inc., Irvine, CA, Mar. 1997.

- [6] PSPICE User's manual, Microsim Corp., Irvine, CA, Jan. 1992.

- [7] B. J. Sheu, W.-J. Hsu, B. W. Lee, "An integrated-circuit reliability circuit simulator RELY," IEEE J. of Solid-State Circuits, vol. 24, no. 2, pp. 473-477, Apr. 1989.

- [8] S.-Y. Oh, K.-J. Chang, K. Lee, "Interconnect modeling and design in high-speed VLSI/ ULSI systems," Proc. of IEEE Custom Integrated Circuits Conf.,pp. 9.4.1-4, Boston, MA, May 1992.

- [9] D. A. Antoniadis, S. E. Hansen, R. W. Dutton, SUPREM-II: A Program for IC Process Modeling and Simulation, Tech. Report, Stanford Electronics Lab., Stanford University, Oct. 1979.

- [10] M. R. Pinto, C. Rafferty, R. W. Dutton, PISCES-II: Poisson Continuity Equation Solver, Tech. Report, Stanford Electronics Lab., Stanford University, 1984.

- [11] R. A. Saleh, A. R. Newton, SPLICE User's Guide Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA, 1986.

- [12] J. White, A. Sangiovanni-Vincentelli, "RELAX2: A new waveform relaxation approach for the analysis of LSI MOS circuits," Proc. of IEEE Int'l Symp. on Circuits and Systems, pp. 756-759, Newport Beach, CA, May 1983.

- [13] L. T. Pillage, R. A. Rohrer, "Asymtotic waveform evaluation for timing analysis," IEEE Trans. on Computer-Aided Design, vol. 9, no. 4, pp. 352-366, Apr. 1990.

- [14] R. H. Tu, E. Rosenbaum, C. C. Li, W. Y. Chan, P. M. Lee, B.-K. Liew, J. D. Burnett, P. K. Ko, C. Hu, BERT-Berkeley Reliability Tools, University of California, Berkeley, CA, Feb. 1992.

- [15] H. M. Jen, A Deep Submicron Drain-Current and Charge Model for MOS Transistors, Ph.D. Dissertation, USC-SIPI Report #321, Univ. of Southern California, Aug. 1998.

- [16] D. Foty, MOSFET Modeling with SPICE: Principles and Practice, Prentice-Hall, 1997.

- [17] Gu, R.X., Elmasry, M.I., "Power Dissipation Analysis and Optimization of Deep-Submicron CMOS Digital Circuits", IEEE J. of Solid-State Circuits, Vol.31, May 1996, pp. 707-713.

# Chapter 2

# **MOS Transistor Modeling**

### 2.1 Overview

Rapid progress in VLSI technology have made the implementation of high density chips possible which contains multi-million transistors. Reducing feature size of the CMOS devices is the main way to increasing integration density in VLSI. New fabrication technologies, like CMOS Shallow Junction well FET (SJET) by Toshiba Corp., Twin-tub CMOS process with Lightly Doped Drain (LDD), and SOI (Silicon on Insulator)[1] have been developed for producing deep-submicron devices. When MOS transistors are made smaller (shorter or narrower) for VLSI circuits, several small-geometry effects arise, and two-dimensional effects near the edges of the smaller transistor become significant. Therefore, simple one dimensional gradual channel approximation (GCA)[2] no longer useful for explaining effect took place under the channel of the small geometry MOS device. Two-dimensional potential distribution in small-geometry MOSFETs, cause in reduction on threshold and punch-through voltages and cause in degradation on the sub-

threshold characteristics of the MOS devices. Also, reducing feature size and keeping supply voltage high, like 5V, cause in hot carrier generation and impact ionization which degrade device performance and characteristics. In the device design standpoint, proper design of the sub-micron devices become crucial for avoiding those short-channel effects. In the device model standpoint, short-channel effects such as carrier velocity saturation, carrier mobility degradation, and drain-induced barrier lowering (DIBL), should be included in the MOS transistor models. This kind of sophisticated models are available in today's technology and can be found in the literature [1],[2],[3]. Digital CMOS IC's have been the main driving force behind the VLSI technology for implementation of high-performance computing and other kinds of commercial or scientific applications. It seems that the demand of high density and high-performance digital CMOS IC's will be continually increased, because of the unique features of CMOS technology mentioned before. During last several years, tremendous amount of improvements have been seen in miniaturization of CMOS devices. Deep sub-micron CMOS devices were introduced and have become widely used in the market. However, as VLSI technology continuous to develop, power consumption, interconnection delay, and clock skew of the VLSI chips become crucial design considerations. Also keeping computing capacity high [4] and avoiding hot carrier effect in deep-submicron CMOS digital circuits, supply voltage of the system should be scaled down. With reducing V<sub>dd</sub>, for keeping circuit speed the same and increasing the current drive capability of the logic gate or transistor, threshold voltage of the MOS transistor should be scaled down by keeping the ratio [5]. Three major criteria can be used to evaluate MOS transistor models for circuit simulation and circuit design: accuracy of simulation results, computational efficiency, and convenience of the model to circuit designers. The accuracy of circuit simulation results depends upon the ability of the model and the associated parameter set to simulate transistor characteristics including drain current, conductances, terminal charges and internodal capacitances over useful ranges of terminal voltages and transistor geometries that are used in the circuits. There is usually a balance between the accuracy and computational efficiency of a model, and clever handling of such a balance is an important engineering challenge. The usefulness of a device model to circuit designers depends upon several factors including the number of parameters, the different effects and features that are incorporated into the model, and how well the accuracy/efficiency balance is achieved. Significant results were reported over the past two decades from research on MOS transistor modeling. The tremendous advance achieved in improving the performance of these devices demands corresponding amount of efforts and progress in modeling their behavior. Three main categories of MOS transistor modeling research include:

type-1: investigation and modeling of specific important aspects of transistor behavior including threshold voltage, mobility, saturation velocity, and subthreshold conduction: type-2: development of highly accurate and computational complex transistor drain current models that include many second-order and higher-order effects which are useful to

device engineers; and

type-3: development of accurate and computationally efficient transistor models with compact parameter sets that closely address the needs of VLSI circuit designers.

For historical reasons, it is useful to classify the existing SPICE MOSFET models into three evolutionary generations[1]. The first-generation models were based on the simple

intention of physically-based analytical expressions, with all simple geometry dependence included in the model equations. These models concentrate on the description of the MOS transistor rather than the behavior of the model equations in a circuit simulator. This generation of models is comprised of Level-1, Level-2, and Level-3 models.

The second-generation models represented a major change from the philosophy for the first-generation ones. In this set of models, analytical equations are subject to extensive mathematical conditioning, with a clear focus on the circuit simulation usage. The parameter structure is twofold; there are individual device parameters, and there are also geometry-related (length and width) parameters. The model structure and its parameters take on considerable empirical character. This has the effect of shifting the challenge in the model to parameter extraction, which is imposed on a rather systematic formulation. This generation of models encompasses BSIM [7] and BSIM2, along with HSPICE Level-28 [21] which is based on BSIM. More recently, third-generation models started to emerge. The fundamental intent is to return to a simple model structure, possibly with a reduced number of parameters. These parameters are strongly physically-based, rather than being very empirical. Mathematical conditioning is also important in these models. However, in contrast to the polynomial functions which are heavily used in the second-generation models. the third-generation models employ more specialized smoothing functions which are mathematically well behaved. With the use of smoothing functions, the analytical equations for drain current and terminal charge and their derivatives are continuous and smooth. A single equation can be used for all regions of transistor operation. An overview of widely used MOS transistor models is presented here to provide the background of the new model development effort. The survey includes analytic models such as the MOS

Level-1, Level-2, Level-3, Level-6, BSIM, and BSIMplus [12] that are implemented in the SPICE3 circuit simulator, the ASIM model from AT&T Bell Laboratories, table look-up approach models, and the newest developed models, EKV model [13] from Europe and aMOS model from TI Inc..

### 2.2 MOS Transistor Models

The first-generation MOS transistor models were based on simple description of the device. The main focus is on the analytical description of the MOS transistor.

#### 2.2.1 The First-Generation MOS Transistor Models

#### 2.2.1.1 The Level-1 Model

The Level-1 MOS model is a first-order model that is useful for hand calculations when designing and analyzing new circuits. Simple expressions are used to describe the drain current characteristics. The Level-1 model applies well to large devices. The only geometric dependency is the inclusion of a simple 1-expression for channel length modulation. Also, there is no subthreshold conduction expression.

#### 2.2.1.2 The Level-2 Model

The Level-2 MOS model, reported by Vladimirescu and Liu [5], requires 18 parameters and includes many second-order effects suitable for in devices with channel length down to 1.2µm. The threshold voltage expression in the Level-2 MOS model included the substrate-bias and narrow-channel effects. The body-effect coefficient due to the depletion charge at the drain and source terminals was modified by correction factors. Depletion-

layer widths near the source and drain were calculated from the source and drain voltages, respectively. A single parameter with inverse-width dependence is used to model the drain-included barrier-lowering effect as well as the narrow-channel effect on the depletion charge-sharing coefficient. The channel length reduction was calculated from a complex expression that included the depletion layer width, the carrier mobility at the semiconductor surface, and the maximum carrier drift velocity at velocity saturation. The transition point between the weak and strong inversion regions was defined to be above the threshold voltage by a multiple of the thermal voltage value. The multiplication factor was calculated from the bulk depletion capacitance and a curve-fitting parameter that was related to the fast surface states at the oxide/silicon interface. A complex expression modeled the drain current in the weak-inversion region as an exponential function of the gate terminal voltage and the transition voltage. Continuity of drain current expressions was achieved at the transition point between weak and strong inversion. However, continuity of the first-order derivative of the drain current expressions was not achieved at this transition point.

#### **2.2.1.3 The Level-3 Model**

The Level-3 MOS model, which was also reported by Vladimirescu and Liu, is a semiempirical model and can be used for technologies with feature sizes down to 1.0µm. The Level-3 model requires 18 parameters in the drain-current expressions that were mainly based on the curve fitting approach. The model took into account the two-dimensional nature of the potential distribution in the channel region. Geometrically dependent effects were included to a limited extent in order to increase the accuracy of the model for technologies below 1.5µm. The threshold voltage in the Level-3 MOS model was calculated from the flat-band voltage and the surface inversion potential, and included the drain-induced barrier-lowering effect and the non-uniform substrate-doping effect. The drain-induced barrier-lowering effect was modeled with an inverse dependency on the cubed channel length. The non-uniform substrate doping effect included correction terms for the short-channel and narrow-channel effects. The correction factor for short-channel effects was calculated from the junction depth by using a trapezoidal approximation. The correction factor of narrow-channel effect was calculated from an inverse-width dependence and modeled the adjustment of depletion charges at the edge of the channel.

The surface carrier mobility was calculated from the intrinsic mobility in the channel region and an empirical fitting parameter. The effect of the vertical field on the intrinsic carrier mobility was modeled as a function of the gate voltage. The effective mobility also included the velocity saturation effect that was dependent upon the horizontal field in the channel and was calculated using the maximum carrier drift velocity parameter. The amount of channel-length reduction was calculated from the lateral electric field at the channel pinch-off point. The coefficient of depletion layer width which was calculated from the substrate doping concentration, and an empirical fitting parameter, was also used to determine the amount of channel-length reduction. The drain-current expression included a Taylor series expansion coefficient of bulk charge and the transconductance coefficient. The saturation voltage was defined as the drain voltage at which the carrier velocity approached the value of the maximum carrier drift velocity parameter. If this parameter was not given, the saturation voltage was determined from the maximum of the

drain-current equation. The weak-inversion drain current expression was similar to that used in the Level-2 MOS model. The Level-3 MOS model used a compact set of parameters. This was convenient for circuit designers who used the model, and also eased the parameter extraction task in which device engineers characterized the technology in terms of the model parameters. Since many model parameters were empirical, integration of the circuit simulator with device-level simulators that solve Poisson equations is quite difficult. Such integration includes determining the transistor parameter values from electronic quantities that are predicted by the device-level simulators. Empirical parameters are usually extracted to fit a limited voltage range or geometric space, while circuit designers could require simulations over a large voltage range and extensive geometric design space. The use of cubic inverse-length dependence for the drain-induced barrier-lowering term of the threshold voltage could limit the range of channel lengths over which a single parameter set is applicable. The use of a square-root dependence on  $(V_{DS}-V_{DSAT})$  in the channel length modulation expression could cause discontinuity in derivatives of the drain-current expressions at the triode/saturation transition point. Such discontinuity could lead to non-convergence problems in the circuit simulation. The MOS Level-6 model was a simple model based on the n-th power law. The simulation times using this model were reported to be considerably better than the Level-3 model. Smooth drain current characteristics at the transition between the triode and saturation regions of operation improved the convergence of the circuit simulator. Parameters can be quickly calculated from a small number of data points. The model is general, and can also be applied to GaAs FETs.

### 2.2.2 The Second-Generation MOS Transistor Models

In the second-generation models, the device geometry is excluded in the basic model equations. In addition, an entirely separate parameter group is used solely to describe the geometric dependence. Independent parameters are extracted for each device. Then the geometry parameters are extracted to fit initial set of independent parameters across the length and width. The goal is to provide an apparatus in which the original independent device parameters can be reconstituted for any particular choice of channel length and width.

### 2.2.2.1 The BSIM Model

The BSIM(Berkeley Short-Channel IGFET Model)[7] is based on the device physics of small-geometry MOSFETs. It was a circuit-level MOS model with strong device physics emphasis which can accurately describe drain-current characteristics of transistors with channel lengths down to about 0.8µm[7]. The model used a total of 62 parameters in the drain-current expression. There were 24 electrical parameters, of which 19 were calculated from nominal, inverse-length and inverse-width coefficients. The simple framework of geometry dependence was a salient feature of the BSIM model. The parameter values were calculated by, length-dependent coefficient and width-dependence coefficient of the parameter respectively. The extracted parameters are in the form of a process file containing parameters for different layers including the NMOS and PMOS transistors, N-diffusion, P-diffusion, and metal layers showing a fully-integrated approach for computer-

aided parameter extraction and circuit design. The threshold voltage expression in the BSIM model included the effect of non-uniform substrate doping on the depletion charge term. The effect of extra bulk charge at the edge of narrow transistor channels was not explicitly modeled in the threshold voltage expression. The drain-induced barrier-lowering coefficient was calculated using zero-bias, substrate-voltage and drain-voltage dependence parameters, each of which has geometry dependency. The reduction of carrier mobility in the triode region due to vertical and horizontal electric fields was modeled by terms that were dependent upon the drain and gate voltages. The vertical field effect included only the gate voltage contribution explicitly. A second-order dependence upon the substrate voltage was included in the parameter that was used to model the vertical field effect. The parameter that describes the horizontal field effects was dependent upon the substrate and drain voltages. The drain-current expression in the saturation region included a body-effect coefficient term and a carrier saturation-velocity term. The drain current and its first-order derivatives were continuous at the transition between the triode and saturation regions. The subthreshold conduction expression in the BSIM model was dominated by the diffusion current component. The subthreshold slope was calculated using drain-voltage and substrate-voltage dependence coefficients. The diffusion component of the subthreshold current was modeled by using an exponential dependence on the gate and drain terminal voltages. The subthreshold current was limited in the strong-inversion region by clamping. The total drain current in all regions of transistor operations was expressed as the sum of weak-inversion and strong-inversion drain current components. The simple geometric dependence framework included in the BSIM model was intended to increase accuracy of the model over a large geometric range. However, the number of

parameters that are to be extracted is quite large. As a result, only a small geometric region can be accurately characterized. Simulation of transistors beyond this characterized region can result in abnormal simulation results. due to exaggeration of second-order geometry-dependent effects. The technique used to model the non-uniform substrate doping effect can cause non-monotonic threshold voltage variation at high substrate voltages, resulting in simulation non-convergence problems. This happens because the terminal voltage during intermediate circuit simulation iterations sometimes take very high values beyond the power—supply rails of the circuit. The drain current and the first-order derivatives are continuous at the triode/saturation transition and this is critical for circuit simulation purpose. However, the second derivative of the drain—current is not continuous, resulting in poor output conductance behavior at the triode/saturation transition and in the saturation region.

#### 2.2.2.2 HSPICE Level-28 Model

HSPICE Level-28 model [21] is a proprietary model which has used HSPICE as a vehicle to gain rather widespread acceptance. The model structure is based on BSIM, but has been extensively enhanced. Through extensive mathematical conditioning, HSPICE Level-28 has been made suitable for analog design. It is thus commonly employed in the IC industry. A unique feature of HSPICE Level-28 model is that the model structure is designed to accommodate model binning. Additional terms are introduced to provide the continuity of the model parameters at all four corners of a bin. In its structure, HSPICE Level-28 model enhances the quadratic expressions which appear in BSIM, so that they become less trou-

blesome. The drain-current expression contains very extensive conditioning of the various transition points. This foreshadows the structure of the third-generation models, and has led to very successful results. The saturation voltage model defines a transition region in addition to the normal use of the linear region and the saturation region, which produces good results. A similar conditioning approach is used on the subthreshold model, where several subregions are defined. In particular, the problems introduced in BSIM by the simple addition of the weak inversion current to the strong inversion current are eliminated. HSPICE Level-28 model maintains the clear focus of the second-generation models on the circuit design purpose. However, the model parameter set is very empirical. In addition, due to its roots, HSPICE Level-28 model carried virtually the entire BSIM mathematical structure. It can thus be slow in the simulation of large circuits. Due to its suitability for analog circuit design, HSPICE Level-28 model is commonly employed in the industrial circuit design environment.

# 2.2.2.3 The BSIM2 Model

The BSIM2 model from U.C. Berkeley [8] was a significant modification of the BSIM model. Several additional empirical parameters were added to model second-order effects of transistor behavior. By increasing the number of parameters, the accuracy of the model in the submicron region was improved. However, additional problems of complexity in circuit simulation and parameter extraction were created due to the very large parameter set. Extrapolating the process file from existing technologies to future technologies for all parameters that was used in BSIM, was retained in BSIM2. The threshold voltage in BSIM2 was very similar to that used in BSIM. The drain-voltage dependence of the drain-

induced barrier-lowering coefficient was removed in order to prevent the occurrence of negative output resistance at low current levels. The effect of the vertical field on the carrier mobility included a quadratic dependence upon the gate voltage in order to model the effect of large electric fields that occur in devices with thin gate oxides. The velocity saturation effect was modeled using the critical electric field parameter, which was calculated from a second-order dependence on the drain and saturation voltages. The effect of source/drain parasitic resistances were lumped with the mobility term during parameter extraction. The horizontal and vertical field effects on the mobility were combined as a summation of terms rather than as a product. The subthreshold drain current was calculated using the charge-sheet approximation. The depletion-layer capacitance and the surface potential at the channel/oxide interface were calculated as functions of the gate voltage. A transition region was defined around the threshold voltage and the effective gate voltage that was used in this region was generated using a cubic spline function in order to improve the transition between the weak-inversion and strong-inversion regions. The ability to handle analog design requirements is a major feature of BSIM2. In addition, the drain current model is more accurate, and provides better convergence behavior during circuit simulation. The main problem with BSIM2 is its complexity as it contains a very large number of parameters.

# 2.2.3 The Third-Generation Models

The third-generation MOS transistor models have started to emerge. The original intent was simplification of the MOS transistor model formulation, a reduction of the number of

model parameters, and the development of parameters which are physically-based rather than being empirical, as in the second-generation models. There is also extensive use of well-behaved mathematical smoothing functions, which allows for smooth and continuous expressions for model equations and their derivatives. The use of these smoothing functions usually leads to a combined equation which is valid for all regions of device operation.

#### 2.2.3.1 The BSIM3 Model

The BSIM3 model from U.C. Berkeley [9], at present, has several different versions released. The original intent of BSIM3 was simplicity, with a simplified model structure and a small number of physically-based parameters. However, Versions 1 and 2 showed several shortcomings. An attempt to repair these problems is made in Version 3, but this is done with large infusion of empirical equations and new model parameters. The model has evolved into an extremely complex form with a very large number of parameters. This seems to deviate from the original intent of the third-generation models. In addition, the complexity of the model and the large number of parameters suggest that parameter extraction task for BSIM3 could be complicated. The BSIM3v3[24] has several new features as compared with BSIM3v2. A single I-V expression describes drain-current and output-conductance characteristics from the subthreshold to the strong inversion as well as from the triode to the saturation regions. Such formula guarantees continuities of I<sub>DS</sub>, gds, gm and their derivatives throughout all V<sub>GS</sub> and V<sub>DS</sub> bias conditions. New width dependencies for bulk charge and source/drain resistance are included. This enhances the accu-

racy in modeling the narrow-width devices. The charge/capacitance model is still based on the BSIM1 structure including more high-order effects in modeling the saturation voltage and the active channel width and length. Non-quasi-static model expression is an option for charge/capacitances in BSIM3v3. It is based on the Elmore equivalent circuit to model the channel charge and channel time constant. However, the RC network and the time constant from gate to source and drain are not considered. The BSIM3v3 was originally intended for one set of parameter values fitting the whole designing geometry space. It has about 110 parameters. However, the extraction procedure is very complicated. Many parameters are difficult to extract and obtain the proper values. Therefore, the binning" is still applied on BSIM3v3 and it results the number of parameters to be more than 300.

### **2.2.3.2 The MOS Model-9**

The MOS Model-9 model was developed at Philips Laboratories [25]. Numerical smoothing functions are added to the MOS Model-9 model to allow for the use of a single expression for device characteristics, e.g. the drain current, conductances, or terminal charges, over the entire operating range of a transistor. The geometry dependence is included with an HSPICE-Level-28-like approach. However, unlike the second-generation models, this method is applied selectively to only certain parameters, and is used in different ways for different parameters. This makes the model more amenable to "binning". In the threshold-voltage modeling, besides the non-uniform doping effects, more efforts was spent on describing the drain-induced-barrier-lowering effect. The effect of static feedback on the threshold voltage is also considered. This effect is particularly important at large drain

biases, when the drain depletion region is a major portion of the total device depletion region. The effective carrier mobility only includes the first-order terms from the vertical and lateral field effects. The terminal charge is derived with gradual channel approximation for different operation regions, and the smooth functions are used to unify the expressions. With fewer number of parameters, the unified current and terminal charge expressions have a simpler format than BSIM3v3. It is easier to perform the "binning" parameter extraction.

#### 2.2.3.3 The Enz-Krummenacher-Vittoz (EKV) Model

The Enz-Krummenacher-Vittoz (EKV) model [13] is clearly oriented toward use in low power analog circuit design. While it contains many third-generation features, the EKV model stands somewhat apart from other models, in that it employs a new and fresh approach to the study of the analytical modeling of the FET. Rather than use the source node as the voltage reference point, the substrate node serves this role; this allows the source and drain to be treated symmetrically, with separate voltages, which is particularly useful in circuits where the FET is used bi-directionally (a common practice in analog circuits). The EKV model develops a somewhat more involved and physically detailed description of the inversion charge. Like the third-generation models and other candidate models, it also uses one drain current equation and a number of smoothing functions, to ensure continuity of that drain current equation and its first derivatives. In contrast to the Power-Lane model and PCIM, which appear to be finished models, the EKV model is a work in progress, and continues to be improved and extended. Although the EKV model includes only two parameters for the description of short channel effects, it has

demonstrated good results using a single parameter set for all geometries for channel lengths as short as  $0.7 \mu m$  [13].

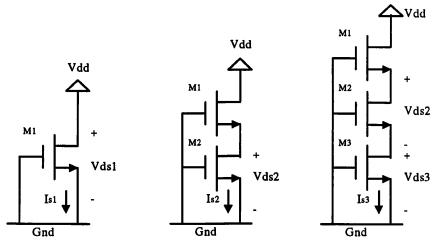

# 2.3 Future Needs

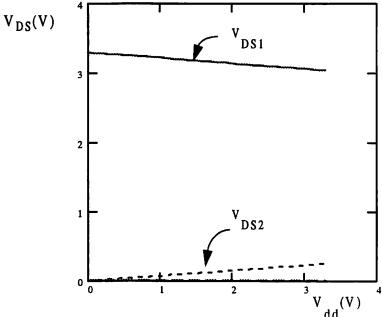

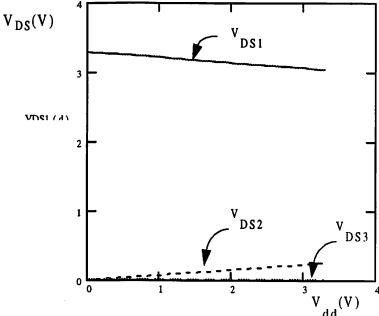

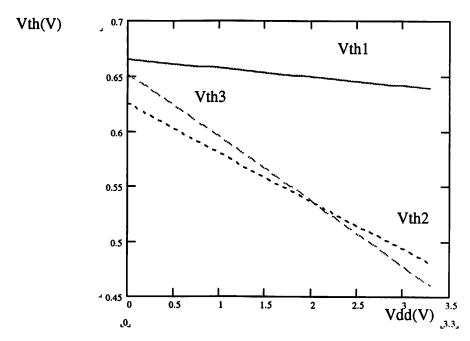

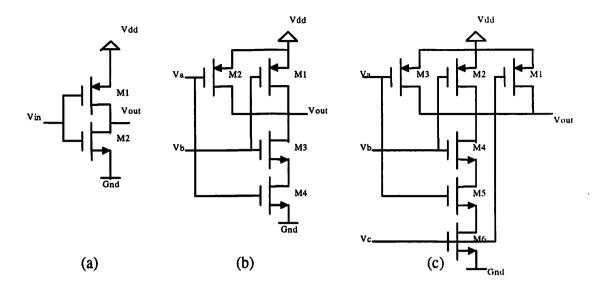

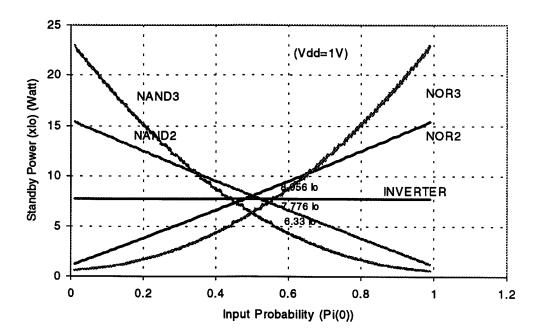

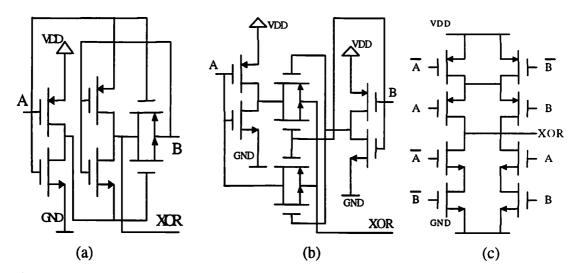

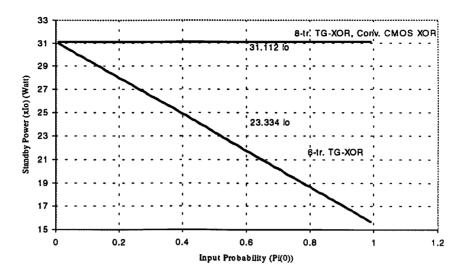

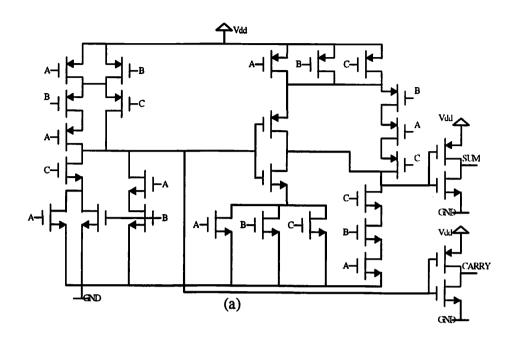

As the CMOS technologies advance to the deep-submicron for low-voltage/low-power and high-speed/high-frequency applications, the accuracy and efficiency of MOS transistor models have to be improved. In the past, most of the MOS transistor modeling work was focusing on the drain current and the terminal charge behavior at the MHz range. Typically, model development was trying to improve the linkage between the technologies and the model behavior. However, the parameter extraction was usually not carefully considered during the model development. This results in a large number of parameters which can not be easily extracted, and the extracted results are highly user- and program-dependent. On the other hand, the charge/capacitance model was derived associated with the DC model and also affected by DC model parameters. Once the DC model parameters are extracted, the charge characteristic is determined accordingly. This leaves little room to match the charge/capacitance behavior, and the results, typically, may not be as good as DC model. For the digital circuits, it does not cause significant trouble, once good DC model behavior is obtained. However in analog circuit design, the charge/capacitance characteristics are as important as the DC part. For the high-frequency behavior, it is even more important to achieve accurate charge/capacitance modeling. Especially, in the lowvoltage design, a transistor can be biased near the transition between different operation regions. Although the DC may have very good accuracy, the improper model of the charge